追求数据吞吐量、响应时间和安装成本,是推动工业网络设计驱动力

描述

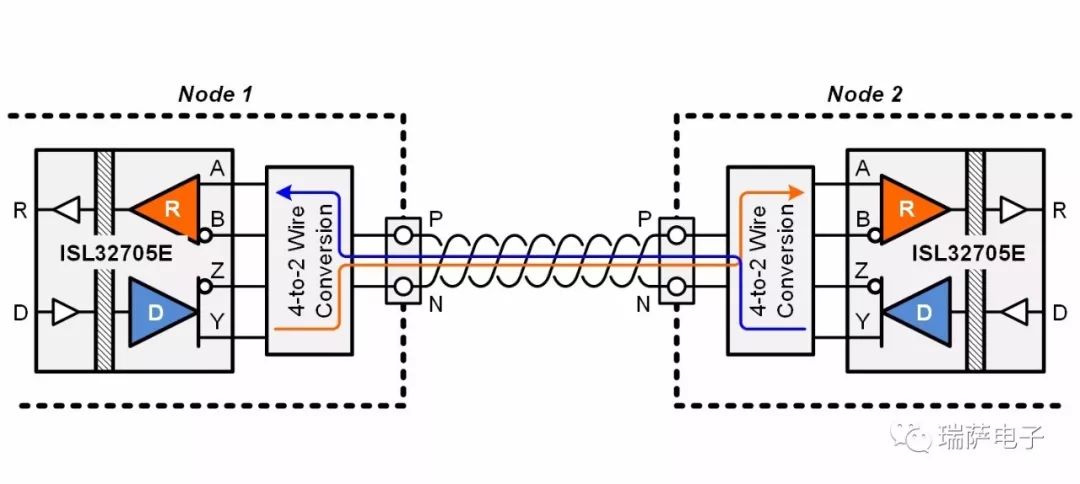

追求更高的数据吞吐量、更短的响应时间和更低的安装成本,是推动工业网络设计持续改进的驱动力。因此,在点对点连接中,为了允许即时和连续地交换二进制数据,全双工总线已经成为首选接口。与一次仅在一个方向上发送或接收数据的半双工接口不同,全双工接口同时在两个方向上发送或接收数据。然而,全双工接口带来迅捷性的代价是需要更多的电缆,安装成本也更高(参见图1)

图 1. 全双工接口需要使用的电缆量是半双工接口的一倍

为了抵消这种缺点,RS-485 用户决定采用一种允许在单条双绞线电缆上传输全双工数据的新型接口。

这种新型点对点接口违反了RS-485在任何时候都要避免总线争用的基本原则之一,通过保持两个全双工收发器始终启动,依靠总线争用运行。

为了增强接口的抗噪声性能,这类收发器是电气隔离的。这样就可保持总线免受共模噪声影响,从而可在共模电压高达±600V、有电噪声的环境中,确保可靠的数据传输。

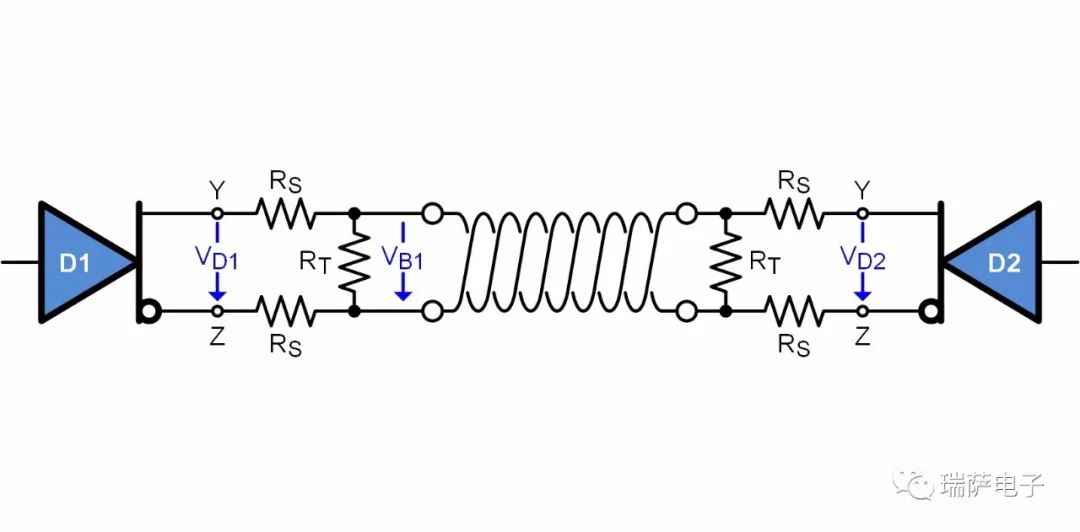

通过单个信号对进行全双工通信需要在收发器之间进行 4 线至 2 线转换,并要求总线电缆能够区分进来(接收)的数据和出去(发送)的数据(参见图 2)。

图 2. 通过单条双绞线进行全双工传输需要 4 线至 2 线转换

4 线至 2 线转换器的设计是比较难办的部分。尽管有解决数字化数据隔离问题的电路,但是这类电路元件数量多,PCB 布局复杂,因此设计成本相当高。这种方法还有一个很大的缺点:这种电路只能在低噪声实验室环境中运行。此外,电路如果暴露于高共模电压之中,会导致电路停止运行。

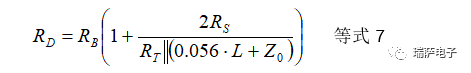

为了向设计师提供可靠的高速解决方案,通过100米长的电缆以4Mbps速率传输数据,同时承受高共模电压,本文讨论了一种总线节点设计,该设计由1个隔离式全双工收发器和6个电阻构成,执行电流限制、线路终接和4线至2线转换。

总线节点设计

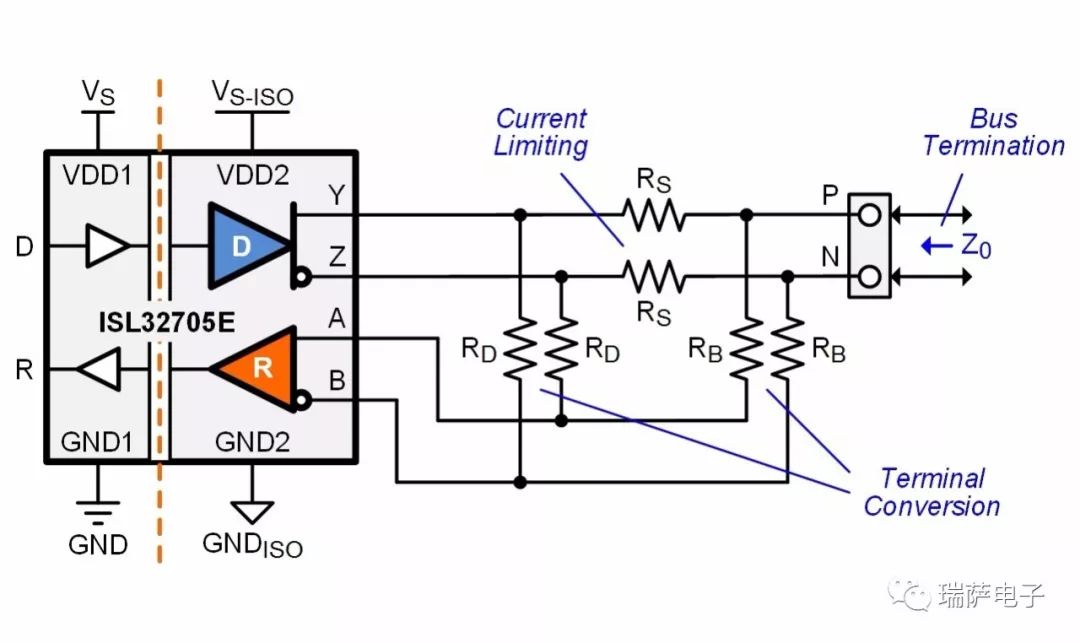

在总线节点设计中,有3个主要方面需要考虑(参见图3):

电流限制:因为两个收发器都持续运行,就会发生总线争用,导致较大的差分电流。此外,收发器接地线之间有很大的地电位差,这也会导致较大的共模电流流过。为了防止驱动器过载并最终导致热关断,必须在驱动器输出路径中放置电流限制电阻(RS)。

总线节点终接:为了防止信号在线路上的反射,总线节点阻抗与总线电缆的特性阻抗必须匹配。这种匹配是通过终端电阻RT实现的。

4线至2线转换:由总线电阻(RB)、驱动器输出电阻(RD)和接收器输入阻抗(RIN)组成的电阻分压器从总线上的全双工数据中提取接收信号。

图3. 总线节点设计的3个主要方面

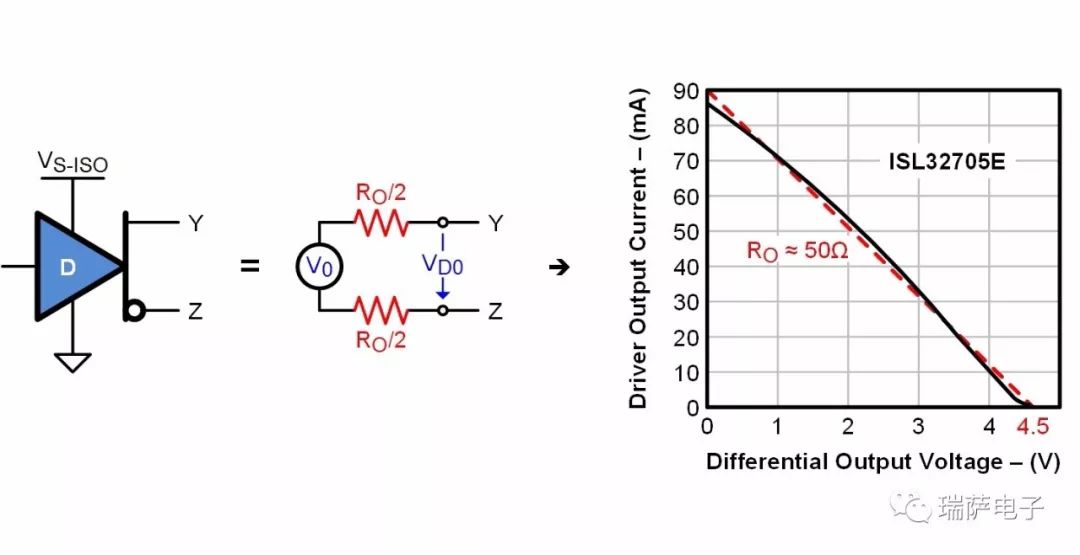

驱动器输出参数R0 和 V0

因为两个驱动器始终保持运行,那么它们的输出阻抗 (RO) 和差分电动势 (V0) 就会影响所有电阻值和总线上电压关系的计算。通过驱动器的 V-I 特性画一条最适合的直线,就可以迅速确定这两个参数,收发器数据表中通常提供该特性。就图 4 所示的收发器而言,这些参数为 V0 = 4.5V 和 RO = V0/IO = 50Ω。

图 4. 用 RO = 50Ω 和 VO = 4.5V 确定驱动器输出特性

电流限制电阻RS

计算RS的值,以便在两个驱动器输出电压之差处于最大值时,将其电流限制在正常工作时的值。例如,如果两个驱动器的输出极性相反,那么它们之间的典型电压差为 3.3V。若将输出电流限制到约30mA,就需要3.3V/30mA=110Ω的总电阻,即每个RS为55Ω。使用工具箱中标准值最接近的电阻,每个RS就变成了60.4 Ω。

图5. 单端、点对点数据链路

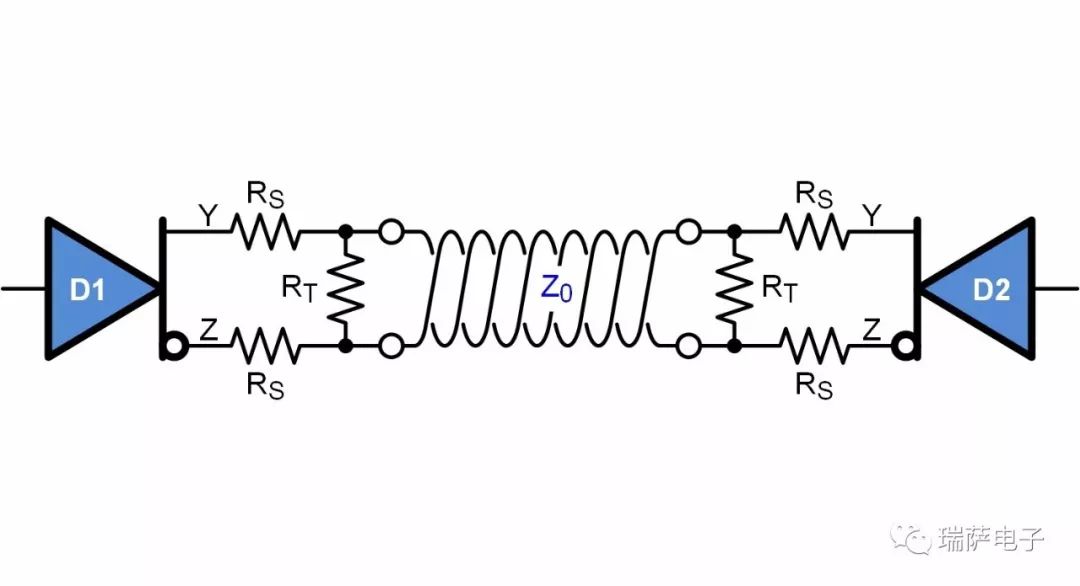

线路终接

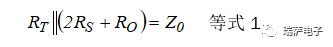

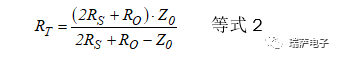

为了防止总线上的信号反射,总线节点的输入阻抗必须与电缆特性阻抗ZO匹配。这意味着,终接电阻(RT)与由两个RS电阻和驱动器输出阻抗(RO)组成的串联电路并联后,总阻抗应该等于ZO。

因为RT是调节总线节点阻抗使其接近ZO的惟一选择,那么我们就从等式1中求出RT:

在等式2中代入RS = 60.4Ω、RO = 50Ω和Z0 = 100Ω(就CAT-5电缆而言)这些值,得出的结果为241Ω,从E-96系列标准电阻值中选择下一个稍高的值,那么Z0 = 243Ω。

4线至2线转换

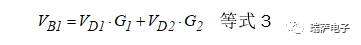

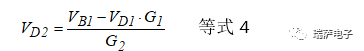

4线至2线转换器使总线节点能够从总线上的全双工信号中,提取相反方向总线节点的输出信号,它是通过从总线电压减去其自身驱动器输出做到的。注意看节点1(参见图6),我们以G1和G2作为通用增益系数建立了总线电压VB1的等式。

从中解出VD2分量,我们就可得到总线节点2衰减后的输出:

电路方面,等式4可以用多个差分放大器实现。每个放大器级都需要4个增益电阻,元件数量显著增加,因此这种解决方案是一种成本较高且复杂的设计。

图6. VB1= VD1 x G1 + VD2 x G2

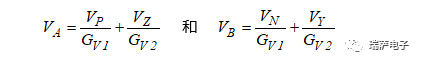

不过,如果我们将VD1 和 VB1 分解成各自的线电压(VD1= VY – VZ,VB1 = VP – VN),并通过电阻分压器(参见图7)加上这两个电压,那么我们就可以在求和点处将这些电压定义成接收器输入电压 VA和 VB:

其中,GV1 和 GV2 是分压器的通用增益系数。

图7. 分压器实现电压求和

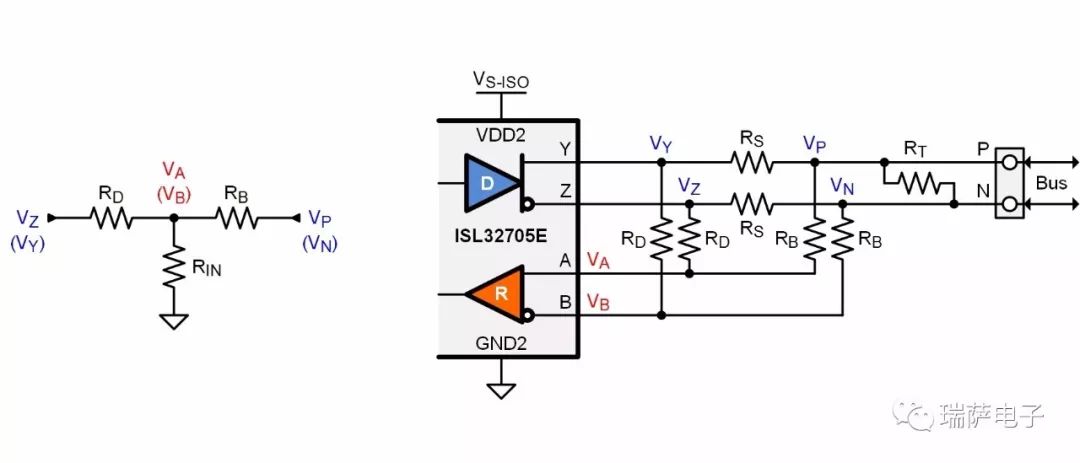

然后,求出 VA – VB 之差,就得到了实际的接收器输入电压:

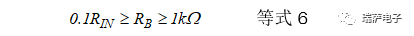

比较等式4和等式5的增益系数,得出G1= GV1、G2 = GV1x GV2和GV2= 1,这证明分压器概念是有效的。就实际应用而言,必须考虑接收器输入阻抗(RIN),因为它会导致增益系数降低。为了将 RIN 的影响降到最低,建议使RB值小于0.1 RIN,但是大于1kΩ,以保持较低的差分总线负载:

RB/RD之比应该等于VB1/VD1之比,即G1,因此要求RD= RB/G1。不过,G1是L(总线电缆长度)、RS、RT和Z0的非线性函数,因此产生了一个复杂的代数表达式。为省去读者了解代数表达式细节的麻烦,等式7为计算RD的最终表达式:

其中L是电缆长度,单位是英尺。

应用举例

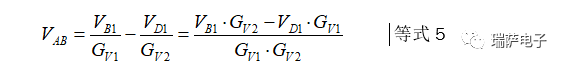

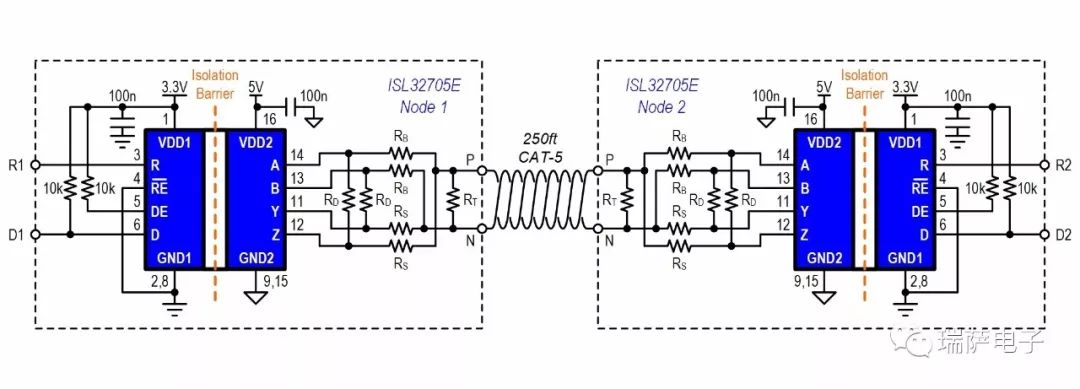

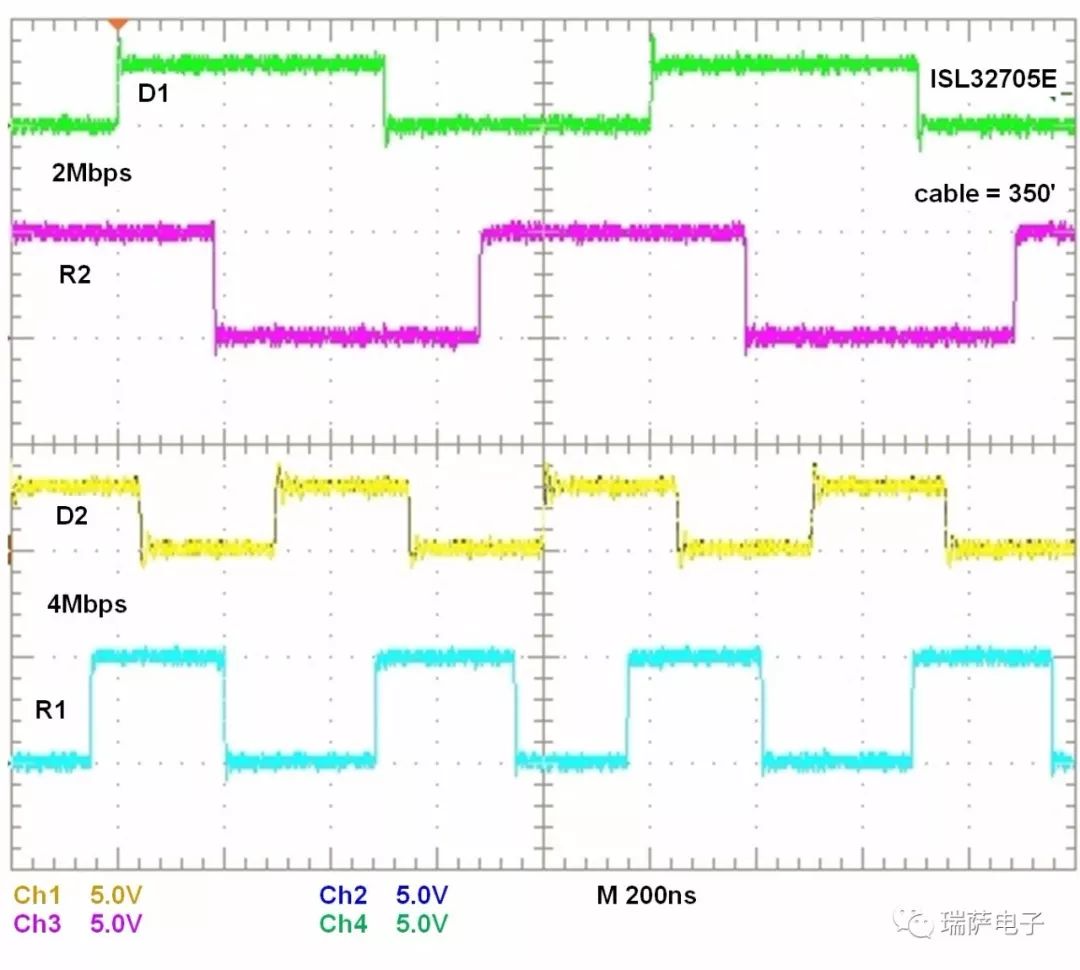

图8和图9显示了100米CAT-5电缆上4Mbps高速全双工数据链路的设计和波形截图。每个总线节点都包括一个隔离式4Mbps全双工收发器和一个RS = 60.4Ω、RD = 2.49kΩ、RB = 1kΩ和RT = 243Ω的电阻网络。

请注意,从DE及DI引脚到正电源应用10kΩ上拉电阻,可在总线空闲时和本地控制器的发送输出为高阻抗时,使驱动器输出保持高水平。

图8. 通过单条100米CAT-5电缆链路,在节点1以2Mbps数据速率和在节点2以4Mbps数据速率进行全双工数据传输

驱动器输入由不同数据速率的逻辑信号提供。D1和D2以随机相移分别接受2Mbps信号和4Mbps信号。图9显示,节点2(R2)的接收器输出正确显示了D1的输入数据,反之亦然。R1显示D2的输入数据。

图9. 正确解码的全双工2Mbps和4Mbps数据

结论

通过4线至2线转换器,实现了在单条双绞线电缆上发送全双工数据,将全双工收发器的4引脚总线I/O连接到2个总线电缆连接器上。为了实现简单、低成本的总线节点设计,可以采用分压器从总线上的全双工混合信号中提取接收信号。除了本文讨论的采用隔离式全双工收发器ISL32705E的高速数据链路,Intersil另外还提供广泛的针对各种数据速率、输出驱动和共模电压的全双工收发器。

-

驱动钛丝(SMA)的可靠性设计(3) 响应时间的设计2024-11-27 0

-

网卡吞吐量测试解决方案2013-12-23 0

-

无线测试之吞吐量测试2015-06-25 0

-

SAR ADC响应时间和市场营销的类比2018-09-12 0

-

USB CDC吞吐量问题2019-10-14 0

-

防火墙术语-吞吐量2010-02-24 1548

-

SAR ADC响应时间与市场营销有何相同点?2018-07-10 812

-

隔离式全双工高速数据链路应用设计方案2018-03-05 8971

-

如何提高无线传感器网络的吞吐量2019-10-04 2604

-

SAR ADC是如何实现更高数据吞吐量的2022-02-06 1837

-

debug 吞吐量的办法2022-08-23 972

-

如何让接口吞吐量提升10多倍2023-01-17 1891

-

iperf吞吐量的测试流程2023-04-03 345

-

如何显著提高ATE电源吞吐量?2023-11-08 717

全部0条评论

快来发表一下你的评论吧 !