赛灵思软件通过调整编译参数以及运行并行编译来优化FPGA时序性能

描述

介 绍

传统时序优化的方法和训练方向主要集中在检查和改善RTL代码或是时序约束。尽管这种方法行之有效,但在实战中因为技术和商业方面的限制,很多更改都不可能真正的执行下去。比如某些对设计比较大的修改,可能会让产品的发布日期承担滞后的风险。当下盛行可重复使用的设计模块,设计中经常会出现不能轻易更改的第三方IP核。最糟糕情况的解决方案(“worstcase scenario” solution)也不过就是把目标器件升级到一个更大的或是有更快速度等级的版本,尽管它们都将带来一笔不小的花费。

万幸的是,当今FPGA工具(比如Xilinx的 Vivado)都有很多开关和设置选项来帮助时序收敛。InTime的方法,就是通过调整FPGA工具的编译过程来解决用户的时序问题和其他性能问题。Xilinx 的ISE和Vivado软件包含了很多综合和布局布线的参数,每一项都至少有两个值可以直接影响最终结果。InTime帮助设计师深入挖掘这些工具的性能,以达到要求的结果。

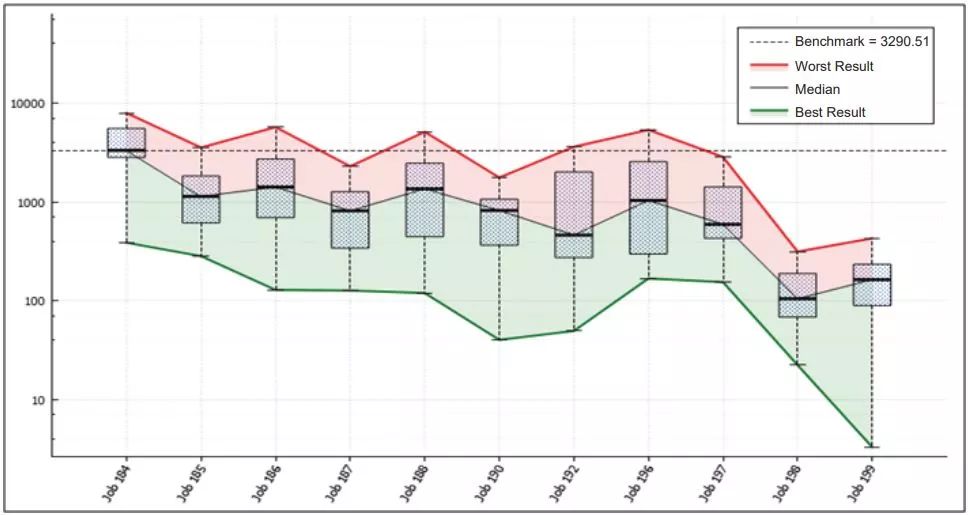

上图是一个客户案例,X轴代表采用不同综合和布局布线的编译批次,Y轴显示的是失败最差余量(Failing Worst Slack, 0代表时序通过)的绝对值,单位为纳秒。在这里您可以清楚地看到InTime把失败最差余量从-0.45ns (-450ps) 减少到了0ns,仅通过调整编译参数就达到了时序目标,而且对设计没有任何变动。

很多情况下,用户经常使用默认的综合和布局布线的参数。因为不确定会有什么后果,很少有人会尝试改变这些参数。再加上很多参数是相互联动的,多个参数如果被同时设置错误会让时序变得更加糟糕;所以调试参数这项任务,就变得更加举步维艰。

更多内容还请点击 “阅读原文”,下载白皮书

了解InTime的流程

优化设计的步骤

步骤一:生成数据

步骤二:使用“Deep Dive”配方

步骤三:Auto Placement配方或Extra Optimization 配方

云端运行InTime和Vivado

结论

-

C程序的完整编译过程2023-11-15 5565

-

FPGA设计时序约束指南【赛灵思工程师力作】2012-03-01 53901

-

选择赛灵思(Xilinx)FPGA 7系列芯片的N个理由2012-09-06 4527

-

直接在Vivado上用亚马逊云来编译优化设计~2017-11-22 6619

-

用FPGA 嵌入式处理器实现高性能浮点元算2018-08-03 3745

-

基于赛灵思FPGA的卷积神经网络实现设计2019-06-19 4223

-

赛灵思ISE® 设计套件11.1版对FPGA有什么优化作用?2019-07-30 2073

-

赛灵思行业最大且性能最高FPGA上市2010-01-18 1034

-

赛灵思FPGA设计时序约束指南2016-05-11 795

-

基于Xilinx的InTime优化设计及流程详讲2017-11-15 1272

-

从赛灵思FPGA设计流程看懂FPGA设计2018-02-20 17059

-

赛灵思推出首个基于机器学习优化算法 FPGA EDA 工具套件2021-06-24 2832

-

赛灵思Vivado ML版优化应用设计2021-07-02 3729

全部0条评论

快来发表一下你的评论吧 !