赛灵思推出首个完全支持软件编程的异构计算平台

描述

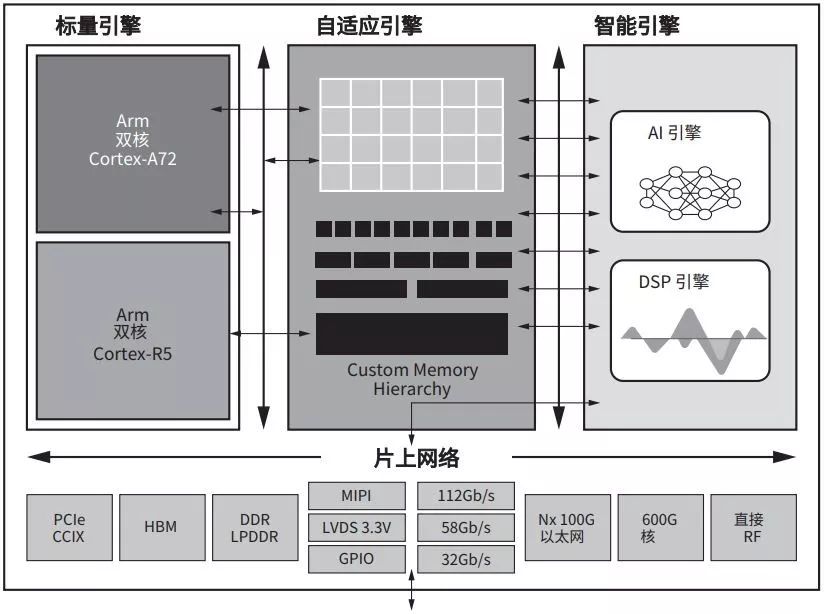

赛灵思正式推出 Versal ACAP,这是一个完全支持软件编程的异构计算平台,可将标量引擎、自适应引擎和智能引擎相结合,实现显著的性能提升,其速度超过当前最高速的 FPGA 20 倍、比当今最快的 CPU 实现快 100 倍,该平台面向数据中心、有线网络、5G 无线和汽车驾驶辅助应用。

近期在半导体工艺领域涌现的技术挑战阻碍了传统上通用 (one-size-fits-all) 型 CPU 标量计算引擎的扩展。如图 1 所示,半导体工艺频率缩放的变化迫使标准计算单元愈发趋于并行。

因此,半导体工业正在探索替代特定领域的架构,包括以往被归入特定极端性能应用的部分,如基于向量的处理 (DSP、GPU) 和完全并行可编程的硬件 (FPGA)。问题在于,哪种架构最适合哪项任务?

推出 ACAP:面向并行异构计算开展软硬件优化

ACAP 的特点在于它结合了新一代标量引擎、自适应引擎和智能引擎。NoC 通过存储器映射接口将它们相连,总带宽为 1Tb/s+。除 NoC 之外,可编程逻辑(和集成型 RAM 块)支持的大量存储器带宽支持可编程存储器架构针对单个计算任务进行层级优化(避免了其他基于高速缓存计算单元固有的高时延和时延不确定性)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

【AD新闻】赛灵思新CEO访华绘蓝图,7nm ACAP平台要让CPU/GPU难企及2018-03-23 4893

-

赛灵思Zynq-7000可扩展处理平台让编程流程更简单2019-05-16 3476

-

如何利用赛灵思28纳米工艺加速平台开发?2019-08-09 2193

-

异构计算的前世今生2021-12-26 3223

-

赛灵思推出DTV可编程平台2010-01-09 937

-

赛灵思推出ISE 12软件设计套件2010-05-05 914

-

赛灵思强推28柰米FPGA目标设计平台2012-02-06 671

-

专访赛灵思资深副总裁汤立人:赛灵思力推完全可编程元件2012-04-18 1517

-

赛灵思正式推出Versal ACAP,一个完全支持软件编程的异构计算平台2018-11-13 6828

-

加速第二代分布式计算 IBM 和赛灵思启动首届异构计算大赛2019-07-30 2316

-

引领迈入自适应计算时代,Xilinx Versal ACAP荣膺2019“世界互联网领先科技成果”2019-10-21 1235

-

揭秘赛灵思计算平台ACAP技术细节2021-01-04 4046

-

异构平台设计方法 探索赛灵思Versal ACAP设计方法论2022-08-02 1307

全部0条评论

快来发表一下你的评论吧 !