PCIe分岔--避免向英特尔接入数据流

描述

INVEA-TECH和CESNET(捷克共和国国家研究所和教育网)演示了一个方法,并行使用两个FPGA PCIe Gen 3×8接口来维持从100Gbps以太网端口到CPU主机的数据传输。这个概念叫做分岔(bifurcation),几年前在英特尔Core I7 CPU中被引进。Intel 试图允许将CPU的PCIe的16个端口分开,使得他们可以处理两个独立的任务,当然相反模式下也能工作,比如将两个外部PCIe8端口合并为一个16端口。使用分岔在单个FPGA上建立一个100Gbps的系统,这消除了对额外PCIe切换芯片的需求,可以节省成本、板上空间和大约6W的功率。

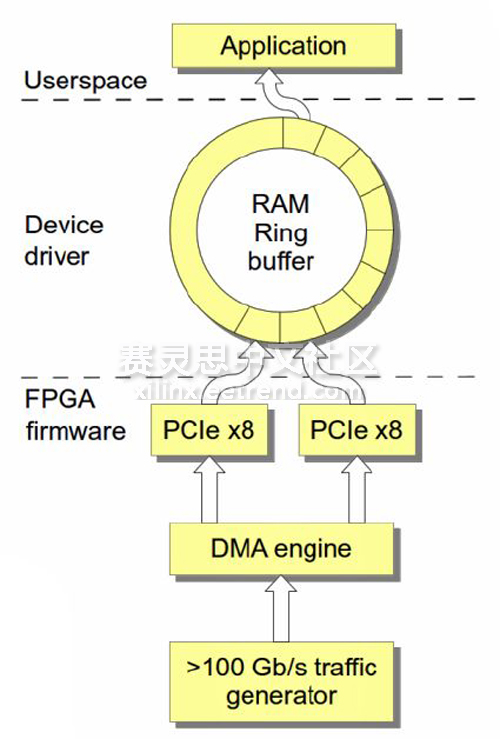

CESNET和INVEA-TECH进行了一系列实验来展示PCIe分岔的好处。测试程序包括装载一块赛灵思Virtex-7 H580T 3D FPGA的FPGA卡。两块FPGA PCIe x8硬块接入卡上的PCIe x16卡槽。运行了Linux设备驱动的FPGA固件将数据传输给位于PC RAM中的环形缓冲区。PCIe x8接口使用round-robin的方式将数据传输给单个缓存。下面的方块图显示了实验过程:

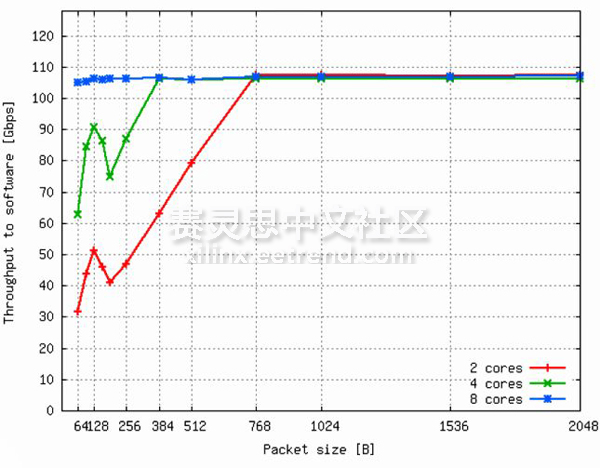

在FPGA生成的超过100Gbps的流量中,例化了随机的分组数据生成器。下图显示了传输速率的结果:

DMA引擎在FPGA组包中例化,因此分组长度不会影响原始PCIe吞吐量。可达到的吞吐量为107Gbps。注意到,至少需要8个CPU核为较小的分组缩放进程,以达到目标的100Gbps。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#高通 #英特尔 #Elite 高通X Elite芯片或终结苹果、英特尔的芯片王朝深圳市浮思特科技有限公司 2023-10-27

-

苹果微软AMD抛弃英特尔加入ARM阵营2012-11-06 3273

-

英特尔转型移动领域难言乐观2012-11-07 3374

-

宿敌相争 AMD向英特尔授权显卡芯片技术的可能性不大2017-05-27 3672

-

【AD新闻】英特尔解读全球晶体管密度最高的制程工艺2017-09-22 3202

-

高通又起诉苹果,指责其违约向英特尔泄露专利代码2017-11-03 3129

-

英特尔爱迪生闪存失败2018-11-02 5302

-

英特尔Optane 32GB Optane内存模块是否可以与7i5BNH兼容?2018-11-19 2343

-

为什么选择加入英特尔?2019-07-25 5327

-

苹果放弃未来在iPhone上使用英特尔5G基带芯片 精选资料推荐2021-07-23 3015

-

英特尔重新思考解决芯片短缺的常用基板2022-06-20 6934

-

需要向英特尔CPU主机接入100G以太网数据流吗?PCIe分岔就是答案2017-02-08 583

-

英特尔应力比特流和编码器的作用介绍2018-11-01 3848

-

英特尔向合作伙伴出货Stratix10DXFPGA2019-09-20 968

-

数据与计算的变革 未来英特尔的产业规划与展望2019-12-29 4938

全部0条评论

快来发表一下你的评论吧 !