两块FPGA器件研究

描述

你可以将两块FPGA器件甚至是两块FPGA开发板捆绑在一起,使用并行或串行I/O以及Chip2Chip LogiCORE和AXI IP的组合,使他们相当于一个器件进行工作。这在新的应用笔记“AXI Chip2Chip Reference Design forReal-Time Video Application”(XAPP1160)中有展示。这个文件的重点在于,在两块Kintex-7 FPGA KC705 Eval板之间,或者在一块Kintex-7 FPGA KC705 Eval板和一块Zynq-7000 AP SoC ZC706 Eval板之间传输实时高清视频流,两板之间通过FMC HPC接口连接。

这里的基本概念是FPGA或者SoC中的具体化的IP和FMC-to-FMC线连接“消失”了,器件上的其他逻辑认为它是在与传统的AXI端口对话,同时发送出去的和接收到的数据就像是它开创了一条连接线缆的道路一样,在另一块板的上器件中的AXI端口上出现。就像是一种AXI的瞬间移动。

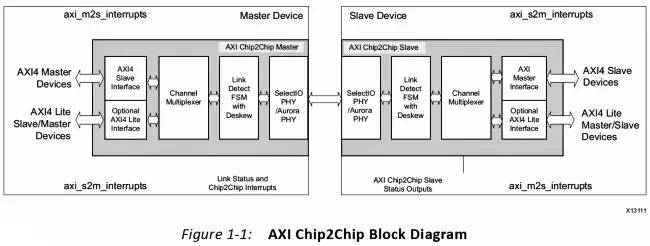

这里有一张来自“LogiCORE Chip2Chip产品指南” (PG067)的简单框图,用来说明基本概念:

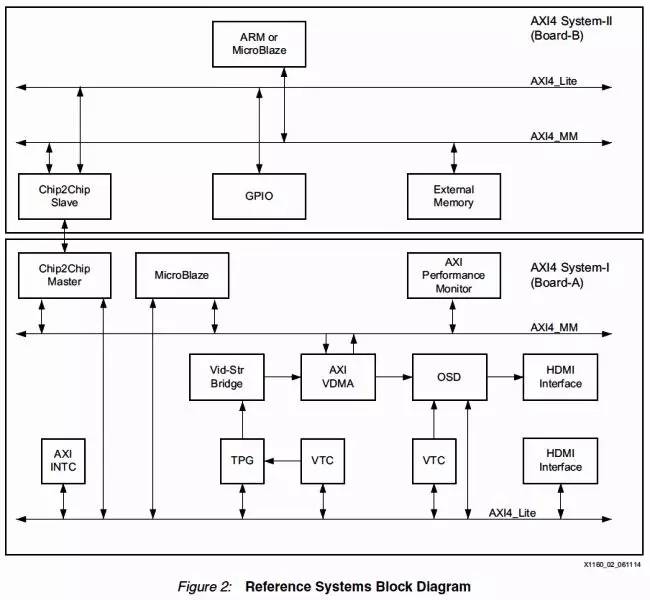

这里是来自“AXI Chip2Chip Reference Design forReal-Time Video Application” (XAPP1160)应用笔记的更详细的参考设计方块图。

操作说明书中的一张图片,展示了使用跨板FMC接口的内部链接方案将两块Kintex-7 FPGA KC705板捆绑在一起。

在连接Kintex-7 FPGA和Kintex-7 FPGA的设计中,设置64位 AXI Chip2Chip主实例为物理层以频率为200MHz运行的独立时钟模式。在连接Kintex-7FPGA和Zynq-7000 APSoC设计中,使用32位的AXI数据宽度来减少在设计中的I/O信号数量。KC705-to-KC705系统在板子间发送1920x1080p60的视频。拥有较窄AXI位宽的KC705-to-ZC706系统在板间发送720x480p60的视频。

-

对于有两块flash的xilinx fpga,vivado中是否可以指定烧录哪个flash2023-04-18 2283

-

DA9063和两块DA9210评估板原理图2023-03-17 510

-

两块STM32之间 SPI DMA通信2021-12-14 1769

-

实现两块fpga之间的通信总结2021-04-27 1262

-

DN289单接口芯片控制两块智能卡2021-04-19 790

-

如何实现两块FPGA之间的通信总结2021-02-25 5329

-

苹果或使用两块屏来完成折叠屏手机2020-03-11 2924

-

用两块Kintex超大规模FPGA开发单板应该如何为两个FPGA供电?2019-04-03 1930

-

苹果iPhoneX拆解:惊现两块电池2018-01-23 20012

-

使用Chip2Chip LogiCORE和AXI 主/从 IP,在两块FPGA之间对视频数据的瞬间传输2017-02-09 3361

-

两块屏控制一台PLC2016-09-06 946

-

两块FPGA之间并行数据传输2015-01-26 2874

-

两块未知的芯片2013-06-07 2921

全部0条评论

快来发表一下你的评论吧 !