ESIstream IP–简化确定性数据序列化的设计

转换器

描述

概述

当使用现代宽带数据转换器时,管理产生的高速串行数据流是一个巨大的挑战。ESIstream 是一个开源的串行数据接口协议,成本极低,支持多种 FPGA 架构的简单硬件实现,并占用最小的资源。简单来说,它是 JEDEC 的 JESD204B 子集 1 和 2 标准的开源替代方案。另外, ESIstream 可为用户带来很多好处,这里将讨论其中的一些,包括低复杂度、低链接延迟和实现确定性延迟的简单方案。

本文将仅阐述 ESIstream 的架构,因为当前有很多文档已很好地描述了 JESD204B 的标准。然后我们将揭示这两种协议之间的细微区别,并介绍 Teledyne e2v,ESIstream 协议的开发者,已决定发布自己的 ESIstream VHDL IP,以进一步简化用户的使用。

串行的历史

新千年以来,数据转换器技术和 CMOS 工艺的发展开始到达功能的瓶颈。起初,高速 ADC 和 DAC(fs 》 10 MHz)采用并行数据接口,这意味着在印刷电路板(PCB)上需从每个数据转换器上引出/引入大量的布线(图 1)。随着采样率和输出数据速率的提高,PCB 设计变得越来越有挑战性。而串行化接口,起初使用 LVDS(低压差分型号),最近则使用串行器/解串器(SERDES)接口(时钟嵌入在数据流中),为这种数据传送的挑战提供了一种解决方案,并可简化 PCB 布线,大大推进形状参数的发展。这种接口的简化对链接的两端都有利(图 1)。Serdes 链接进一步简化了 PCB 的设计,因为无需保证数据线长度匹配。

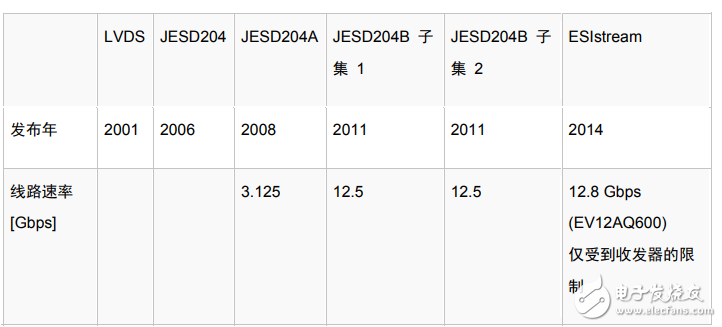

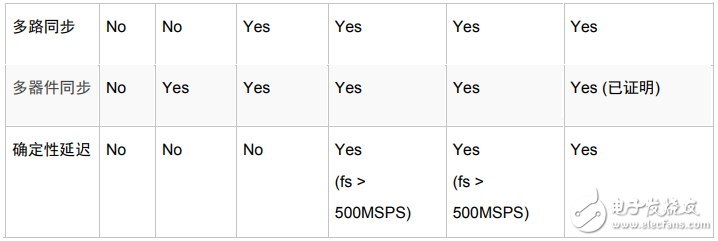

然而,经过了很多年,才有了一种串行方案解决了宽带数据转换器带来的所有系统级挑战。实现确定性延迟是同时采样的前提,人们付出了很多努力研究它。下表(表 1)展示了过去 12 年甚至更长时间里 JESD204 标准的发展和开源 ESIstream 的发展。

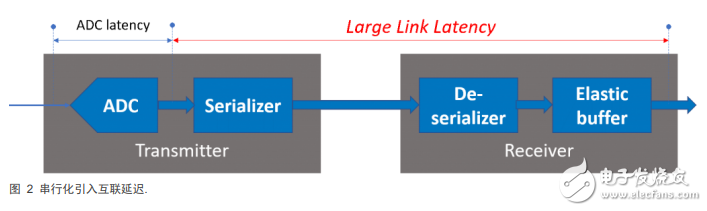

串行数据的一个显著的优点是,当分辨率提高时,器件的封装无需包含额外的数据线,这可以帮助限制引脚数的增加。但是,串行化的缺点是由于引入了编码/解码流程,且通过某些额外的接收路径弹性缓冲器补偿路径之间的对齐度,导致增加了额外的传递延迟。

串行化也可帮助管理数据转换器的电源需求,因为它能降低单个器件需要的特定输出驱动器的数目。而且,通过实现差分串行线,可帮助减少复杂系统中产生的电气噪声,以保证良好的动态范围。另外,编码方案也可分散频谱噪声,而且差分信号可降低串扰。

事实上,直到现在,早期串行接口依然不能很好地支持多个并行通道的应用,设计师依然会面临板级设计的挑战。

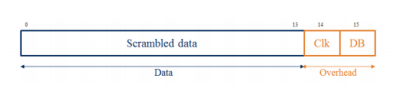

如图 3。通过这种方式,它的编码效率高达 87.5%,比 JESD204B(8b/10b 的编码流)略高。不均等位(DB)可在 CLK 位切换使能同步监控时,保持数据链间的 DC 平衡。

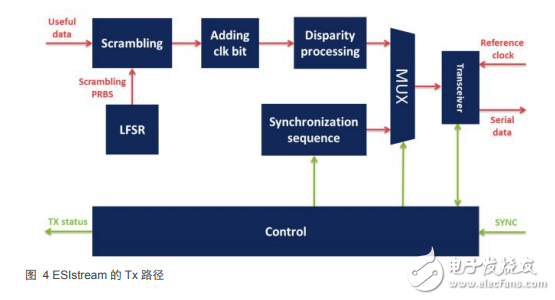

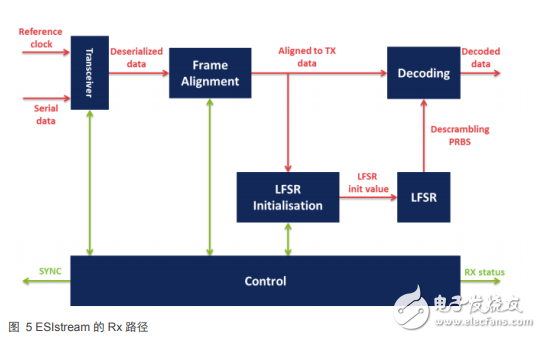

ESIstream 发射端(Tx)和接收端(Rx)核心的上层框图如图 4 和图 5 所示。

ESIstream 编码算法被设计成可减少串行接口的物理限制。最重要的是,发射端和接收端之间的链接需要 AC 耦合。考虑到这一点,发射的数据要确保 DC 平衡,否则链接耦合电容可能漂移,导致数据眼图闭合,破坏接收的数据。

在接收端,时钟和数据恢复(CDR)模块通常使用 PLL 锁到发射的信号,这样无需使用独立的时钟线。但是,为了使得 CDR 锁定并保持锁定状态,需保证传送的信号经过特定的变换次数。

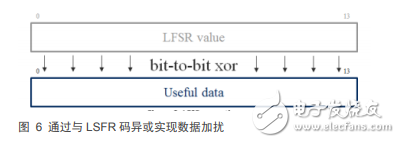

为发送的数据加扰是为了维持 DC 平衡,确保链接保持锁定。ESIstream 的开发者希望限制数字设计的复杂度,于是采用附加的算法最小化错误传递。这种算法基于斐波那契数列,长度为 2 17 -1。此外还应用了 14 位的移位。转换流程输出的有用数据和线性反馈移位寄存器数据(伪随机码)进行异或操作,如图 6。

加扰之后,14 位的数据结果被编码成 16 位的数据帧。第一个附加位时钟位,随着每个连续帧切换。第二个附加位不均等位根据不均等计数器(RDC)的当前状态设置。两种 RDC 状态可导致:

1. RDC 小于+/-16,不均等位设置为‘0’。

2. RDC 大于+/-16,不均等位设置为‘1’,数据反向(按位非运算)。

这个操作可满足 Rx PLL 锁定的最小转换次数的要求,并满足链接 DC 平衡的需要。在正常操作下,接收端首先检查不均等位。如果它为高,则在去扰前反向接收的数据。如果它为低,则直接对数据进行去扰操作。

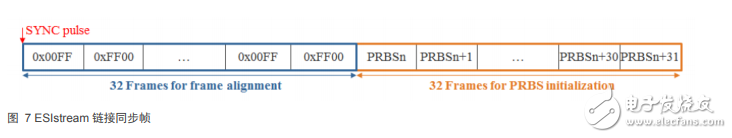

对于确定性操作,ESIstream 要求链接同步,即发射端和接收端的数据帧对齐,链接两端的加扰引擎在同样的初始化状态。同步分两步,帧对齐和伪随机位序列(PRBS)初始化。

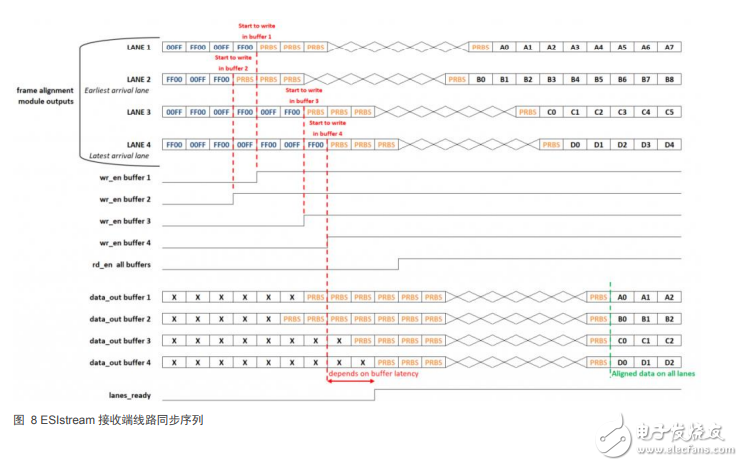

接收端通过使能 SYNC 启动流程。这个脉冲应该持续至少一个帧周期。然后发射端发送一个 32 帧的对齐样式(图 7)。在接收端,这个保留的序列绕过加扰和不均等的处理,使接收端和发射端时序对齐。在对齐帧之后,发射端立刻发送一个 32 帧的 PRBS 数据——包含 14 位的 PRBS 以及时钟和不均等信息。经过正确地处理,接收端 LFSR 由接收端的 PRBS 字初始化。这时链接已同步(图 8)。用户可在接收端通过观察时钟位,连续监控同步状态。如果时钟位在某一帧没有切换,则出现了同步问题,需复位链接重新同步。

通过加扰以及时钟位和不均等位的处理,ESIstream 可保证确定的数据传输。

-

如何使用Serde进行序列化和反序列化2023-09-30 2503

-

Java序列化的机制和原理2019-07-10 1803

-

c语言序列化和反序列化有何区别2021-07-14 1445

-

SpringMVC JSON框架的自定义序列化与反序列化2022-10-10 3470

-

理解PHP反序列化漏洞2017-09-07 770

-

java序列化和反序列化范例和JDK类库中的序列化API2017-09-27 588

-

云数据确定性删除的深层次含义2018-02-08 1056

-

什么络是确定性IP网2021-11-16 3839

-

static属性为什么不会被序列化2022-07-15 2573

-

什么是序列化 为什么要序列化2023-09-14 4150

-

如何用C语言进行json的序列化和反序列化2023-10-07 2651

-

Java序列化怎么使用2023-10-10 1183

-

科技云报到:数字化转型,从不确定性到确定性的关键路径2024-11-16 1315

-

极简代码,搞定JSON序列化与反序列化2026-02-23 453

-

JSON:简洁代码高效搞定序列化与反序列化2026-02-25 258

全部0条评论

快来发表一下你的评论吧 !