简述RF 分析仪的三大构成部分

描述

在有关 RF 数据转换器的博文中,我们了解了什么是软件驱动以及可以如何用它来管理 RF 数据转换器 IP 的状态和控制。

我们介绍了可以如何通过编写一个简单的独立应用来帮助调试系统中的 RF-ADC 和 RF-DAC 。

在那篇博客中,我提到赛灵思已通过一个叫作 RF Analyzer 的工具实现了在任何电路板上的任何器件上启用了 RF 数据转换器的调试功能。我现在将用接下来的两篇博文来拆箱此实用程序、查看其主要功能,并了解我们可以如何用它来管理 RF-ADC 和 RF-DAC 块。我还会讲讲如何用它来生成 RF-DAC 激励,以及如何查看和分析 RF-ADC 接收的数据。

这篇博客由上,下两部分组成,专门针对 RF Analyzer 而编写。在本篇文章中,我们来看一下该工具是由哪些块构建的。我认为这个 RF 分析仪是由三条主线组成的。

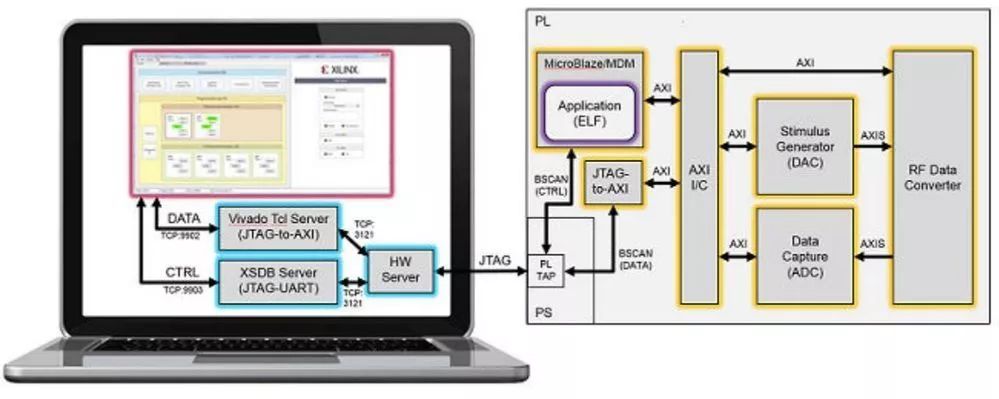

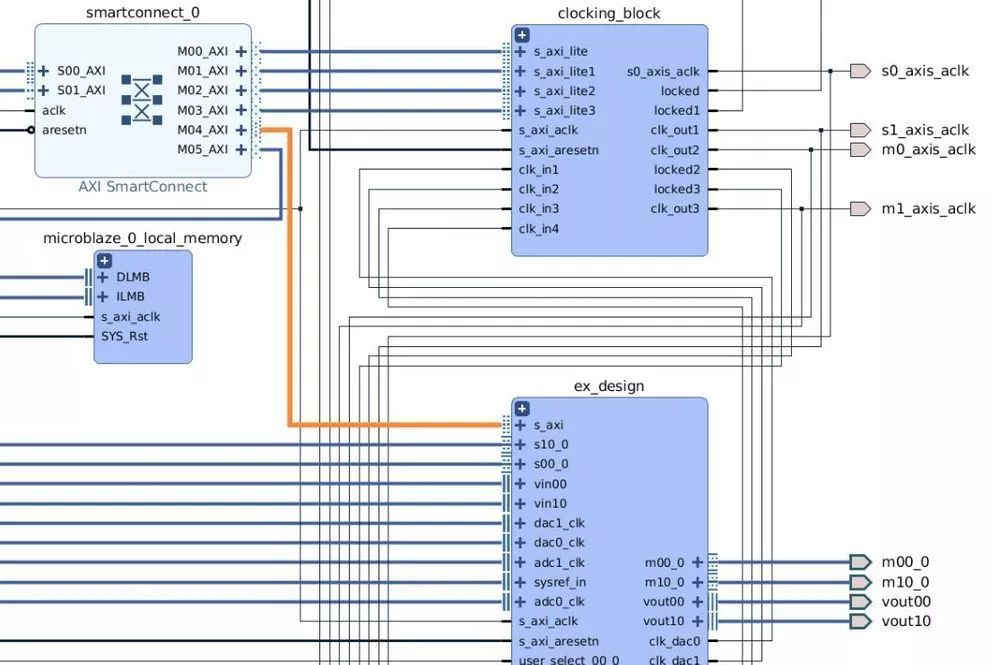

首先是 PL 设计,它是由 Zynq UltraScale+ RF Data Converter IP 示例设计、用于启用 RF 子系统状态和控制的 MicroBlaze,以及用于写入和读取 GUI 数据的 JTAG to AXI Master IP 组成的。此设计中还包含一些时钟生成功能。

该设计的最大优点就是您拥有与您的设计相匹配的 IP 配置。这意味着您现在已经将 RF 数据转换器与您的设计的其他部分分离开来。这让您能够剥离设计的其余部分,而只查看系统中的数据转换器性能、捕获 RX 数据,并分析“RF Analyzer GUI”中的数据。

应该理解为,这种独立灵活设计的成本是无法管理 DDR 内存的(因为我们想要在任何器件/任何电路板上启动),因此用于回放/捕获的存储空间是通过片上的 Block RAM 构建的。为了便于使用,我们还为每个带有分析仪数据包的可用器件提供了预先构建的比特流。

在 PL 比特流之后,我们有一个 MicroBlaze 应用。该应用旨在管理 PL 设计中的控制路径。在较高的层级,它可以接收来自 RF Analyzer GUI 的命令、对其进行解析,并通过驱动 API 从各个块中读回请求的数据,甚至可以修改块的设置。这是以 RF 分析仪设计的 ELF 文件的形式提供的。

在顶层有一个 Labview GUI,允许您与 RF-ADC 和 RF-DAC 块连接,以进行数据捕获和激励生成/回放。该 GUI 遵循与 ZCU111 RFSoC Evaluation GUI 相同的样式。

下图显示的是完整 RF 分析仪的展示图。

既然我们对 RF 分析仪有了初步的了解,那就让我们来更深入地了解一下。最好的办法是从定制的 IP 配置开始,并逐一了解一下在 RF Analyzer 环境中使用它所需的所有步骤。

在本示例中,我们将使用 ZCU1275 功能描述电路板。该电路板配有 16x16 ZU29DR 器件。我们实际上不需要对这个电路板太了解。我们只需要确定以下内容:

转换器时钟已设置

Bullseye 连接器在构建中连接妥当,以与我们特定的 IP 配置相匹配

RF 分析仪会对其余部分进行管理。我们稍后会回过头来讨论这个问题。

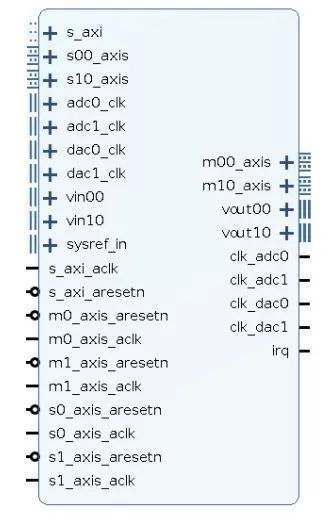

第一步是设置 IP。这是我们构建 RF Analyzer PL 设计的基础。您可以从 IP 目录中选择它,也可以在“IP Integrator”中的块设计 (block design) 中找到它。

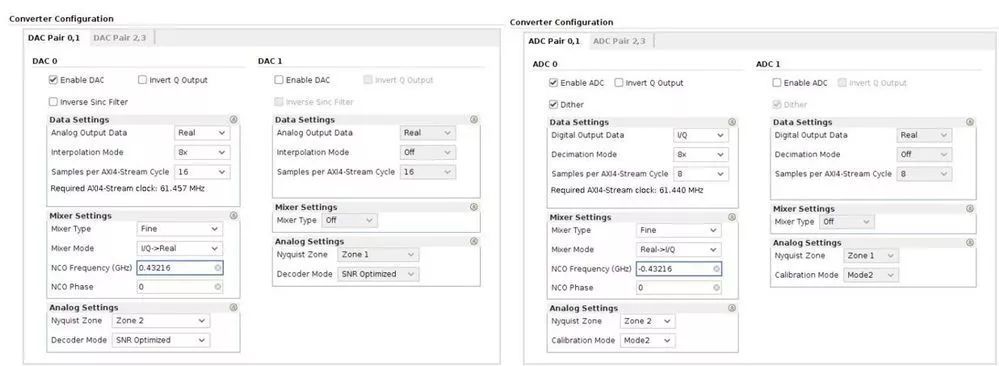

所以,我认为展示 RF-ADC 和 RF-DAC 配置并查看一些 CW(连续波)音调是有意义的。

然后,我们会设置两个块以启用环回,我们还可以从 RF-DAC 发送上转换 QAM16 矢量并通过 RF-ADC 来接收它。

在本示例中,我们将运行采样率为 1966.08 MHz 的 RF-ADC 和采样率为 3932.16 MHz 的 RF-DAC。

您最终获得的 IP 类似于此处显示的 IP。两个 DAC 块皆处于活动状态,并使用了两个ADC块。

您现在可以单击“OK”并决定跳过 IP 的 OOC 综合。

我们必须指示工具,当我们创建示例设计时,我们打算启用 RF 分析器。您需要在 Vivado Tcl 控制台中输入以下命令。

set_property -dict [list CONFIG.RF_Analyzer {1}] [get_ips]

接下来,右键单击 IP 并点击“Open Example Design”。您随即会获得一个包含示例设计和 Analyzer 基础结构的新工程。

在此设计的顶层,我们利用 STARTUPE3 块为设计提供 AXI4-Lite 时钟和外部复位。您将在设计的顶级 RTL 封装中看到此步骤实例化。

一旦加载了比特流,就会在 PL 结构中置位 EOS(启动结束)信号。此步骤对复位进行管理,并会启动设计和应用的运行。

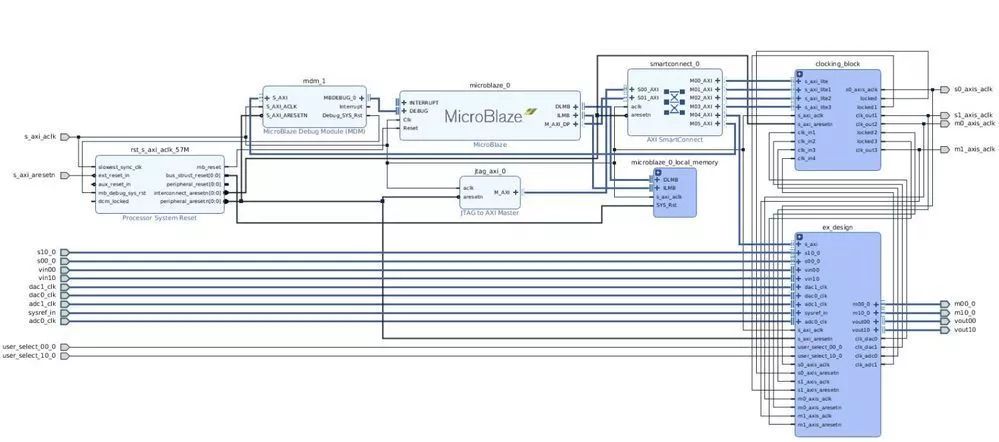

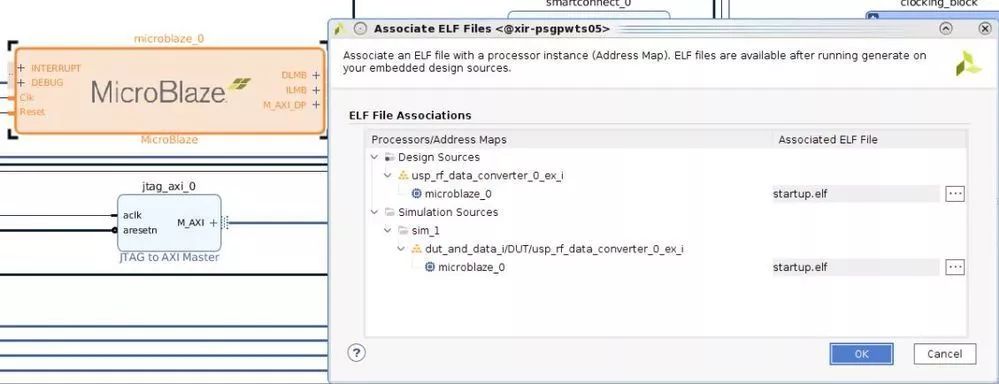

如前所述,该设计包含 MicroBlaze。

这将对 RF 数据转换器和时钟的状态和控制进行管理。如果您右键单击此处,您会看到有一个与之关联的 ELF 文件。

这将嵌入对比特流中的设计和 Analyzer GUI 之间的通信进行管理的程序。

您还将在此块设计中看到 JTAG to AXI master IP。该 master IP 将分别管理 Source 和 Sink IP 的数据路径。

我们利用 AXI SmartConnect 来管理 MicroBlaze/JTAG2AXI Master 与其他设计之间的接口。

您可以看到与 IP 示例设计 AXI4-Lite 接口的连接:

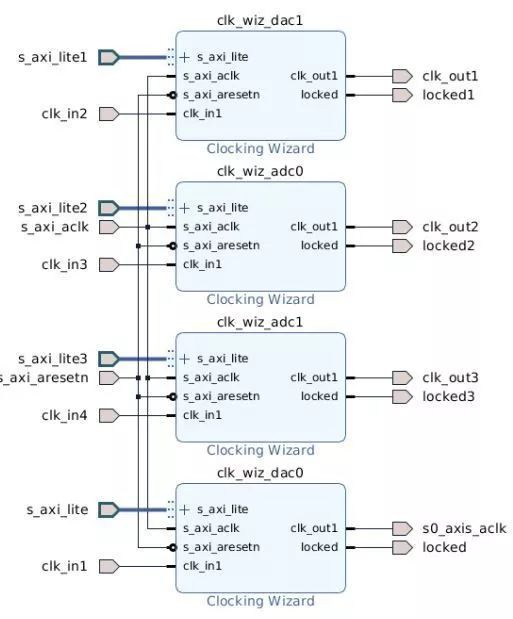

还有一个时钟块。这需要块输出时钟并使用 MMCM 将 AXI4-Stream 时钟驱动到各个块。每个 MMCM 都启用了 AXI DRP 端口。这使我们能够灵活地管理数据转换器时钟的变化,并在运行时扩展 AXI4-Stream 时钟。

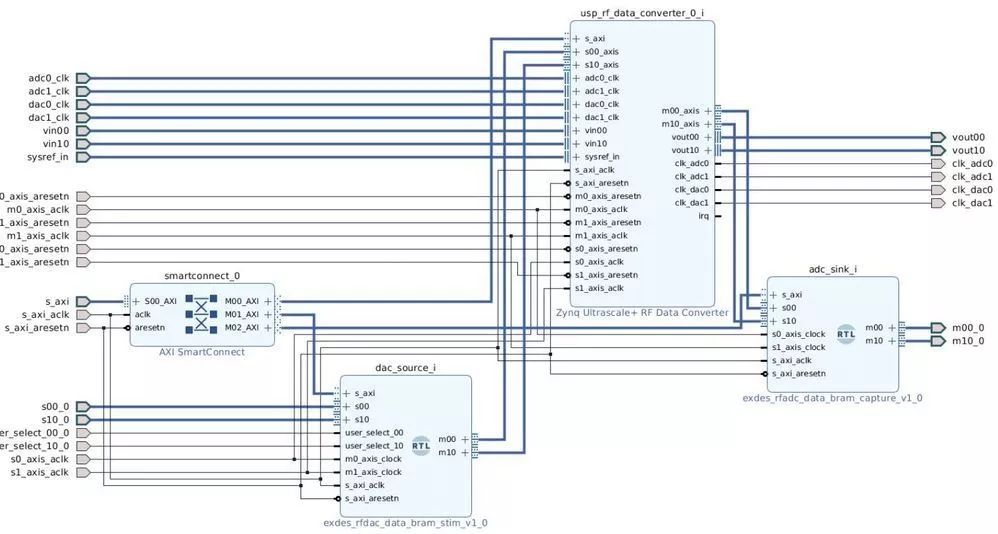

现在我们来深入了解一下带有 IP 示例设计的层级结构。

当我们在主项目中进行配置时,我们可以看到该层级包含 RF Data Converter IP、DAC 源和 ADC 接收器。这些块是 RTL,如果右键单击并选择“Go to Source”,您可以更详细地进行查看。

RF-DAC 数据激励块由可以加载样本的 128 kbits 的块 RAM 组成,这些样本接着会被发送到 RF 数据转换核中启用的 RF-DAC 通道。

实际上,DAC 源只是一个构建 BRAM 的 XPM,可以使用新的激励写入 BRAM,也可以将其内容传输到 DAC。

激励块中的每个通道都会驱动 Zynq UltraScale+ RF 数据转换器 IP 核上的 AXI4-Stream。由于每个转换器最多可以有四个 AXI4-Stream 接口,因此 DAC 源块中最多有 16 个通道。每个启用的 AXI4-Stream 接口都会被映射到从 DAC0 开始的连续通道。

DAC 激励块的寄存器映射包含在 (PG269). 的表 56 中。同样,可以在 Sink 块中捕获 ADC 流数据并进行回读。

Zynq UltraScale+ RF 数据转换器上每个启用的 AXI4-Stream 输出数据都存储在数据采集块的单独通道中。由于每个转换器最多可以有四个 AXI4-Stream 接口,因此数据捕获块中最多有 16 个通道。

启用的 AXI4-Stream 接口会被映射到以 ADC0 开始的连续通道。

每个通道的存储包括 128 kbit 的块 RAM。捕获块的地址映射可以在 (PG269) 的表 55 中找到。

在我们实现它并生成比特流之前,您可以在以下文件中查看我们对设计的约束:

usp_rf_data_converter_0_example_design.xdc

这些约束可以创建主时钟并会添加一些 PBlock 进行平面布局设计,以便激励和捕获存储器能够和数据转换器块放在相邻的位置。

为了管理 axi_aclk 域和 AXI4-Stream 时钟域之间跨时钟域的静态控制信号,添加了一些时序例外。

例如,num_samples_reg 会提示数据激励和示例设计中的捕获块要从 RF-ADC 块获取多少样本或要发送多少样本到 RF-DAC 块。由于这是在控制路径上,因此它与 axi_aclk 同步。然后,该设置会按照在 AXI4-Stream 时钟上运行的 Stimulus 和 Capture 块中的地址计数器逻辑来使用。信号不应经常变化(如果有变化的话),因此在实现过程中将其作为定时路径忽略不会有问题。

在此阶段,您可以将设计一直运行到 write_bitstream。

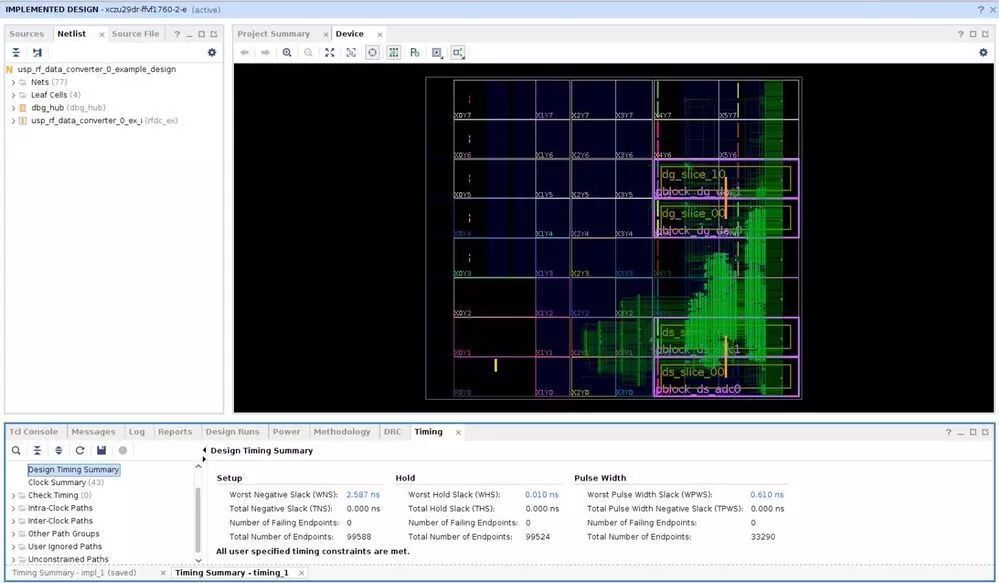

您会看到时序条件已满足。注意:Pblock 用于锁定相关块旁边的捕获和激励内存。

比特流的运行路径类似于以下路径:

\ip_name\ip_name.runs\impl_1

现在我们已准备就绪,可以下载此比特流了。我们拥有使用分析仪所需的一切,可以查看电路板上的数据转换器了。

下次我们将通过 ZCU1275 功能描述电路板来启动此比特流并探索“RF Analyzer GUI”的功能。

回头见!

-

Intersil血糖分析仪系统框图及构成2009-11-30 4875

-

关于RF矢量信号分析仪的简单介绍2019-06-06 1878

-

基于实时频谱分析仪的毛刺和其它瞬态RF信号分析2019-07-23 2331

-

ENA RF网络分析仪2019-09-24 1773

-

ENA RF网络分析仪AN1463-82019-09-30 1109

-

逻辑分析仪的应用分析2008-11-27 1163

-

尿液分析仪2009-08-12 1093

-

安捷伦发布整合式FieldFox RF合成分析仪2009-08-03 869

-

功率分析仪作用_功率分析仪分类2019-12-19 4687

-

浅谈频谱分析仪的基本模块2021-02-15 2944

-

频率特性分析仪的构成与频率特性分析仪的原理分类2023-07-28 2496

-

矢量网络分析仪和射频网络分析仪有什么区别2024-05-20 3087

-

矢量网络分析仪的工作原理 矢量网络分析仪的扫描速度2024-06-03 4683

-

Keysight 频谱分析仪(信号分析仪)2024-09-12 2336

-

安捷伦AgilentE4291B 阻抗分析仪 RF阻抗/材料分析仪2025-01-08 997

全部0条评论

快来发表一下你的评论吧 !