数字秒表的组成及主要设计步骤介绍

电子说

1.4w人已加入

描述

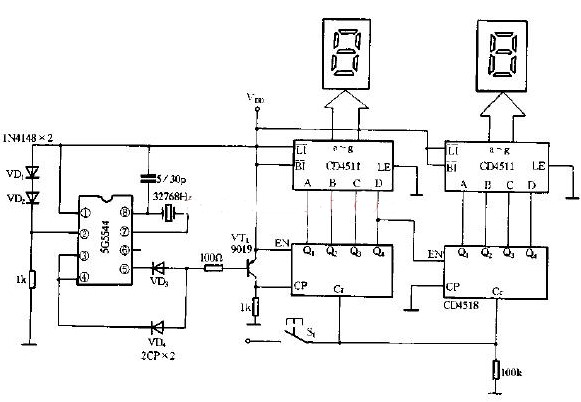

数字秒表由计数显示电路、复位电路、控制电路与电源电路组成。通过计数电路、译码电路在显示器上输出,以上部分组成计数显示电路;通过电源清零电路和反馈清零电路实现复位功能,构成复位电路;利用启动开关和停止开关控制触发器产生启动/停止信号,实现秒表的启动和停止动能,构成控制电路;在整个秒表中,电源电路是采用外接电源来实现的。经过布线、焊接、调试等工作,数字秒表成形。在秒表电路中利用一个译码器译出计数器所计时间并经LED显示器显示出来,利用控制电路对秒表进行启动/停止控制。当计时结束后,利用复位电路对其进行复位。

在整个秒表中最关键的是如何获得一个精确的100HZ计时脉冲,除此之外,数字秒表需有清零控制端,以及启动控制端、保持保持,以便数字时钟能随意停止及启动。数字秒表显示由时(12或24进制任选)、分(60进制)、秒(60进制)、百分之一秒(一百进制)组成,利用扫描显示译码电路在八个数码管显示。

设计内容及步骤:

1、根据电路持点,用层次设计概念。将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口,同时加深层次化设计概念;

2、软件的元件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的同一设计,如何熔合;

3、适配划分前后的仿真内容有何不同概念,仿真信号对象有何不同,有更深一步了解。熟悉了CPLD/FPGA设计的调试过程中手段的多样化;

4、按适配划分后的管脚定位,同相关功能块硬件电路接口连线;

5、所有模块尽量采用VHDL语言设计。

推荐阅读:http://www.elecfans.com/dianlutu/187/20180201628251_2.html

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于CD4033的数字秒表的设计2018-05-11 7926

-

数字秒表2012-10-15 9347

-

数字秒表纠错2018-12-27 3044

-

SDH数字微波通信技术的组成、特点及应用介绍2019-06-18 4320

-

怎么设计一种基于FPGA的数字秒表?2021-05-10 1886

-

分享一种数字秒表设计方法2021-05-11 1963

-

怎样去设计基于FPGA的数字秒表?2021-05-13 1482

-

基于单片机的数字秒表的设计简介2021-12-08 2142

-

数字秒表电路图2009-05-08 6979

-

基于CPLD的VHDL语言数字钟(含秒表)设计2015-11-04 927

-

一种基于FPGA的数字秒表设计方法2017-11-18 10805

-

基于8051单片机的数字电子秒表的设计2017-11-27 1998

-

使用51单片机实现秒表的程序免费下载2019-08-21 2131

-

基于单片机的数字秒表2021-11-25 1591

-

数字信号采集的主要步骤是什么2024-05-30 2724

全部0条评论

快来发表一下你的评论吧 !