超高速SerDes 在芯片设计中的挑战

电子说

描述

SerDes已经成为需要快速数据移动和有限I/O的芯片的主要解决方案,但随着速度不断提高以抵消数据的大量增加,这项技术变得越来越具有挑战性。

串行器/解串器用于将并行数据转换为串行数据,使设计人员无需增加引脚数即可加速数据通信。但随着数据量的增加,以及随着越来越多的设备连接到Internet并最终连接到云,越来越需要更快地移动更多数据。这反过来又使SerDes设计变得越来越复杂。

对高速SerDes的大部分需求来自大型数据中心,目前最先进的吞吐量为100 Gbps。最近开始想400Gbps进发。甚至人们已经开始探路800 Gbps的支持。

因此,IEEE和光互联网论坛的标准在单个通道上定义越来越高的数据速率,这允许将数据聚合到更大的系统。然后,为了将SerDes技术提升到更高的性能水平,其中一项重大进步是采用了高于28Gbps的PAM4信令。

Rambus业务运营高级主管Sunil Bhardwaj说:“随着串行数据速率达到每通道100多Gbps,带宽增加引起的信号损伤促使采用PAM4或4级脉冲幅度调制。” “与NRZ(不归零)相比,PAM4通过在每个符号中传输两位来将给定数据速率的带宽减半。这允许在通道中加倍比特率而不会使所需带宽加倍。例如,使用PAM4信令,56-Gbps比特率以28 GBauds传输,并具有14 GHz的奈奎斯特频率。利用NRZ信令,56 Gbps比特率以56 GBauds传输,奈奎斯特频率为28 GHz。

但有一个权衡。“多个符号级别使PAM4对振幅噪声比NRZ更敏感,”他解释说。“与NRZ相比,PAM4引入了9.6dB的损耗,工作在相同的奈奎斯特频率。然而,在这些高频率下,以NRZ奈奎斯特频率的一半运行的能力使PAM4成为低损耗替代方案。与NRZ一样,PAM4信号受抖动,信道损耗和符号间干扰的影响。此外,三个眼图的测量因新的接收器行为而变得更加复杂,例如三个限幅器阈值,单个限幅器时序偏移,均衡以及时钟和数据恢复。不出所料,PAM4信号分析从为分析NRZ的抖动和噪声而开发的技术中借鉴了很多。此外,许多NRZ技术适用于PAM4。

另一个复杂因素是高速设计越来越容易受到电磁串扰问题的影响,ANSYS半导体业务部产品营销经理Annapoorna Krishnaswamy指出。

电磁交叉耦合问题变得越来越重要的一些关键因素包括:

频率升级,片上信号频率超过2 GHz,远高于6 GHz范围,进入5G应用的毫米波频段。

快速提高数据速率和使用高速接口来支持多个通道彼此接近的数据传输,这增加了串扰问题的风险。

更高的集成度和布局密度(SoC)。通过将高性能数字内核与敏感的模拟和RF构建模块集成。

封装小型化,大量使用再分配层(RDL)。

2.5D / 3D封装技术。

随着时钟速度的提高,先进的封装类型以及减小面积的压力,设计和验证高速IC设计的传统方法已不再足够。

设计的所有方面 - 高速信号/时钟线,详细的电源和接地布线,无源器件,甚至封装层都需要进行详细建模和验证。需要对片内寄生效应进行精确建模,包括自感和互感(RLCk),以完全捕获从DC到毫米波频率的电气行为(适用于5G应用)。这对于分析由于通过电源/接地,基板或封装层的耦合而影响多个邻近区域的一个信号的不需要的电磁干扰是至关重要的。“

这就是为什么准确捕获电磁(EM)现象(包括电流分布,皮肤和邻近效应)对于降低EM串扰引起的性能降低和高速和低功耗片上系统故障的风险至关重要的原因。EM感知设计流程有助于减少过度设计,面积和成本,同时确保设计的卓越性能,质量和可靠性。

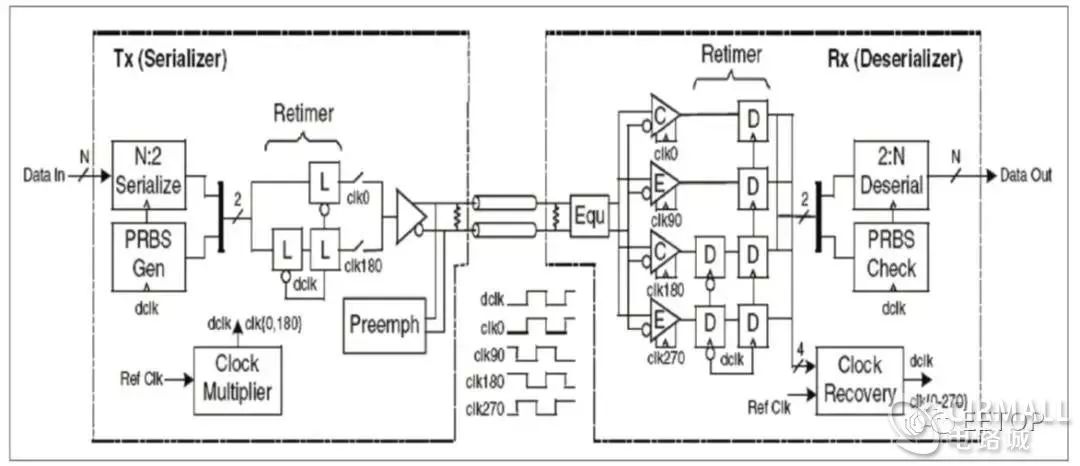

图1:典型的高速I/O架构

设计挑战

Adesto的工程师Martin Hujer表示,对于高速SerDes,挑战通常围绕功耗,时钟分配(模拟时钟树),所用封装类型以及寄生效应。“然后,PCB上有布线,支持测试模式和测试模式,以及快速数字逻辑。此外,还需要一种符合更高级别串行协议的数字控制器。在集成到定制芯片中时,必须考虑所有这些挑战。根据应用和客户要求,可能存在替代解决方案的潜力,您可以在一个或多个高速串行通道和速度较慢但仍然很快的并行总线之间进行权衡。“

-

基于FPGA的超高速FFT硬件实现2009-06-14 7935

-

MAX14978超高速USB模拟开关2019-05-27 1733

-

超高速大电流有源滤波器LDO控制器2020-03-19 2283

-

使用LT1394的超高速单电源比较器2020-04-10 2245

-

具有超高速控制的2MHz PWM 2A降压稳压器2020-08-10 1947

-

请问超高速SerDes在芯片设计中的挑战是什么?2021-06-17 1974

-

教你如何去挑选一个超高速的ADC?2021-06-22 1695

-

超高速电机控制方式讨论2021-08-27 1281

-

超高速频率合成器方案的设计与实现2009-03-01 1736

-

超高速雷达数字信号处理技术2009-10-21 2186

-

超高速充电电池2009-11-28 1009

-

超高速采样技术2016-12-28 1056

-

超高速电路设计面临的挑战与广义信号完整性(GSI)内涵和走势2023-03-27 2400

-

如何检测复杂的超高速调制光信号?2023-10-30 1320

-

超高速工业相机的应用2025-02-24 2012

全部0条评论

快来发表一下你的评论吧 !