MOS管的正确用法

功率器件

描述

学过模拟电路,但都忘得差不多了。重新学习MOS管相关知识,大多数是整理得来并非原创。如有错误还请多多指点!

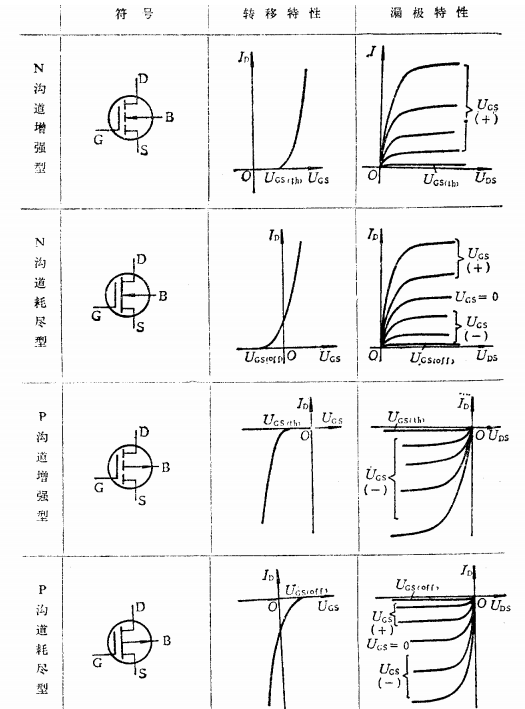

先上一张图

一句话MOS管工作原理

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到一定电压(如4V或10V, 其他电压,看手册)就可以了。

PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。

在使用MOS管设计开关电源或者马达驱动电路的时候,大部分人都会考虑MOS的导通电阻,最大电压等,最大电流等,也有很多人仅仅考虑这些因素。这样的电路也许是可以工作的,但并不是优秀的,作为正式的产品设计也是不允许的。

1,MOS管种类和结构

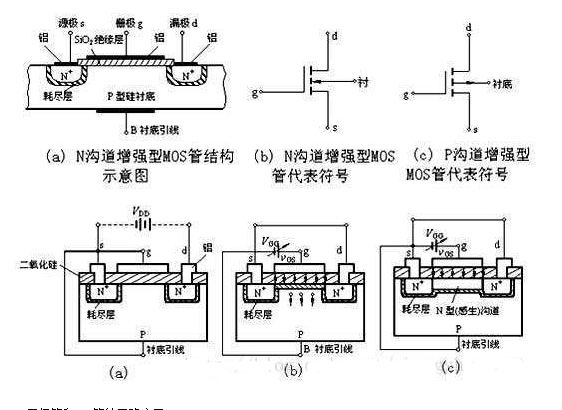

MOSFET管是FET的一种(另一种是JFET),可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,但实际应用的只有增强型的N沟道MOS管和增强型的P沟道MOS管,所以通常提到NMOS,或者PMOS指的就是这两种。

至于为什么不使用耗尽型的MOS管,不建议刨根问底。

对于这两种增强型MOS管,比较常用的是NMOS。原因是导通电阻小,且容易制造。所以开关电源和马达驱动的应用中,一般都用NMOS。下面的介绍中,也多以NMOS为主。

MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的。寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免,后边再详细介绍。

在MOS管原理图上可以看到,漏极和源极之间有一个寄生二极管。这个叫体二极管,在驱动感性负载(如马达、继电器),这个二极管很重要,用于保护回路。顺便说一句,体二极管只在单个的MOS管中存在,在集成电路芯片内部通常是没有的。

MOS管的正确用法

1 三极管和MOS管的基本特性

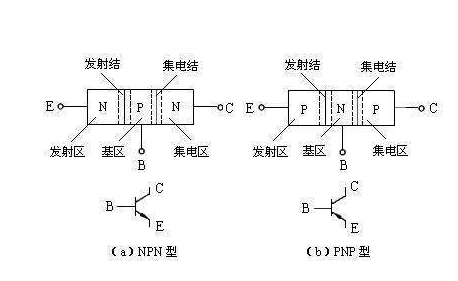

三极管是电流控制电流器件,用基极电流的变化控制集电极电流的变化。有NPN型三极管和PNP型三极管两种,符号如下:

MOS管是电压控制电流器件,用栅极电压的变化控制漏极电流的变化。有P沟道MOS管(简称PMOS)和N沟道MOS管(简称NMOS),符号如下(此处只讨论常用的增强型MOS管):

2 三极管和MOS管的正确应用

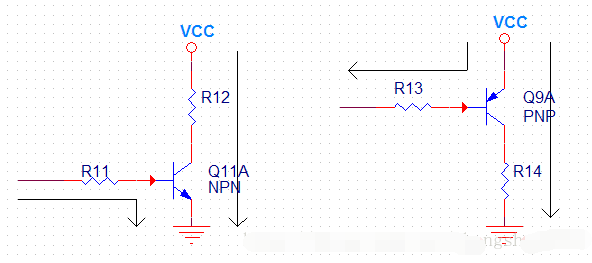

(1)NPN型三极管,适合射极接GND集电极接负载到VCC的情况。只要基极电压高于射极电压(此处为GND)0.7V,即发射结正偏(VBE为正),NPN型三极管即可开始导通。

基极用高电平驱动NPN型三极管导通(低电平时不导通);基极除限流电阻外,更优的设计是,接下拉电阻10-20k到GND;优点是,①使基极控制电平由高变低时,基极能够更快被拉低,NPN型三极管能够更快更可靠地截止;②系统刚上电时,基极是确定的低电平。

(2)PNP型三极管,适合射极接VCC集电极接负载到GND的情况。只要基极电压低于射极电压(此处为VCC)0.7V,即发射结反偏(VBE为负),PNP型三极管即可开始导通。

基极用低电平驱动PNP型三极管导通(高电平时不导通);基极除限流电阻外,更优的设计是,接上拉电阻10-20k到VCC;优点是,①使基极控制电平由低变高时,基极能够更快被拉高,PNP型三极管能够更快更可靠地截止;②系统刚上电时,基极是确定的高电平。

所以,如上所述

对NPN三极管来说,最优的设计是,负载R12接在集电极和VCC之间。不够周到的设计是,负载R12接在射极和GND之间。

对PNP三极管来说,最优的设计是,负载R14接在集电极和GND之间。不够周到的设计是,负载R14接在集电极和VCC之间。

这样,就可以避免负载的变化被耦合到控制端。从电流的方向可以明显看出。

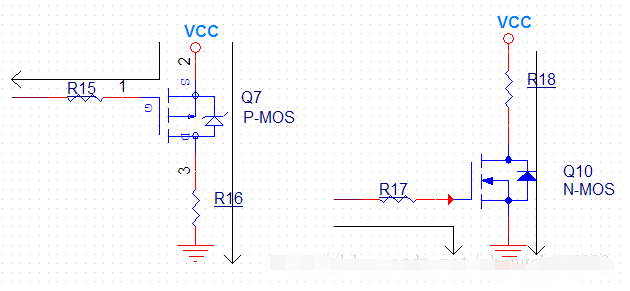

(3)PMOS,适合源极接VCC漏极接负载到GND的情况。只要栅极电压低于源极电压(此处为VCC)超过Vth(即Vgs超过-Vth),PMOS即可开始导通。

栅极用低电平驱动PMOS导通(高电平时不导通);栅极除限流电阻外,更优的设计是,接上拉电阻10-20k到VCC,使栅极控制电平由低变高时,栅极能够更快被拉高,PMOS能够更快更可靠地截止。

(4)NMOS,适合源极接GND漏极接负载到VCC的情况。只要栅极电压高于源极电压(此处为GND)超过Vth(即Vgs超过Vth),NMOS即可开始导通。

栅极用高电平驱动NMOS导通(低电平时不导通);栅极除限流电阻外,更优的设计是,接下拉电阻10-20k到GND,使栅极控制电平由高变低时,栅极能够更快被拉低,NMOS能够更快更可靠地截止。

所以,如上所述

对PMOS来说,最优的设计是,负载R16接在漏极和GND之间。不够周到的设计是,负载R16接在源极和VCC之间。

对NMOS来说,最优的设计是,负载R18接在漏极和VCC之间。不够周到的设计是,负载R18接在源极和GND之间。

3 设计原则

为避免负载的变化被耦合到控制端(基极Ib或栅极Vgs)的精密逻辑器件(如MCU)中,负载应接在集电极或漏极。

-

MOS管的正确选择指南2025-01-10 2388

-

MOS管如何正确选择?2024-10-09 1879

-

MOS管的普遍用法,你知道么?2023-10-12 5615

-

MOS体二极管的妙用2022-11-18 3964

-

三极管和MOS管驱动电路的正确用法2022-02-11 2689

-

如何正确挑选MOS管?2021-03-15 1686

-

如何正确的选择MOS管2021-02-10 7260

-

MOS管正确选择的步骤介绍2020-07-10 1908

-

如何正确选择mos管?飞虹厂家告诉你!2019-11-21 3313

-

MOS管防反接用法2019-07-08 27419

-

MOS管耐流讨论2018-11-21 3096

-

低压mos管的正确选型?2018-10-19 7190

-

mos管的基本用法2017-09-14 3214

-

MOS管正确选择的步骤2012-11-02 14630

全部0条评论

快来发表一下你的评论吧 !