D触发器转为为SR型,JK型和T型

模拟技术

描述

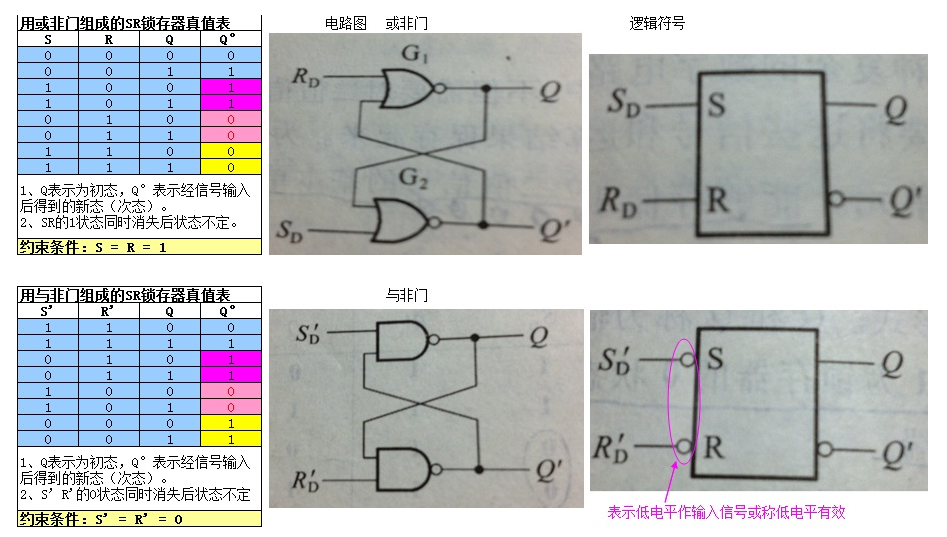

能够存储1位二值信号的基本单元电路统称为触发器(Filp-Flop)

触发器是构成时序逻辑电路的基本逻辑部件。它有两个稳定状态:“0”和“1”。在不同的输入情况下,它可以被置0状态或1状态,当输入信号消失后,所置成的状态能够保持不变。所以触发器可以记忆1位二值的信号。根据逻辑功能的不同,触发器可以分为SR触发器、D触发器、JK触发器、T和T‘触发器。按照结构形式的不同,又可分基本SR触发器、同步触发器、主从触发器和边沿触发器。

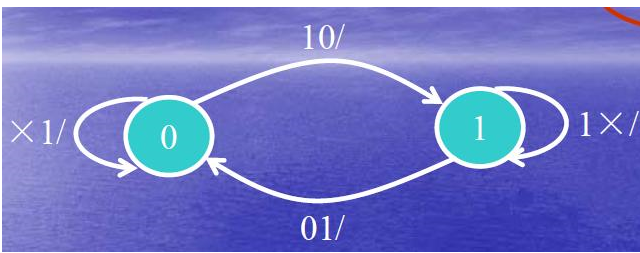

其状态图:

a、当触发器处在0状态,即Q = 0,若S’R‘ = 10或11时,触发器仍为0状态。若S’R‘ = 01,触发器翻转成为1状态。

b、当触发器处在1状态,即Q = 1,若S’R‘ = 01或11时,触发器仍为1状态。若S’R‘ = 10,触发器翻转成为0状态。

约束条件是S’R’不能同时为0。

D触发器如何转为为SR型,JK型和T型?

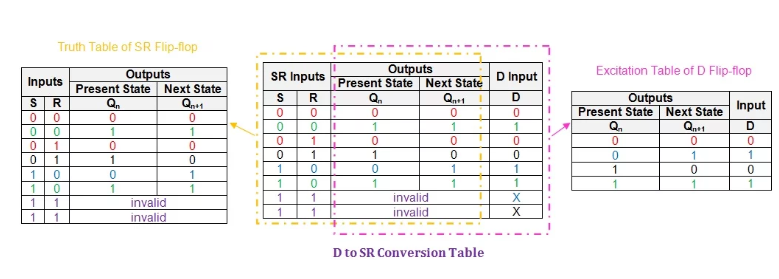

将D转换为SR触发器

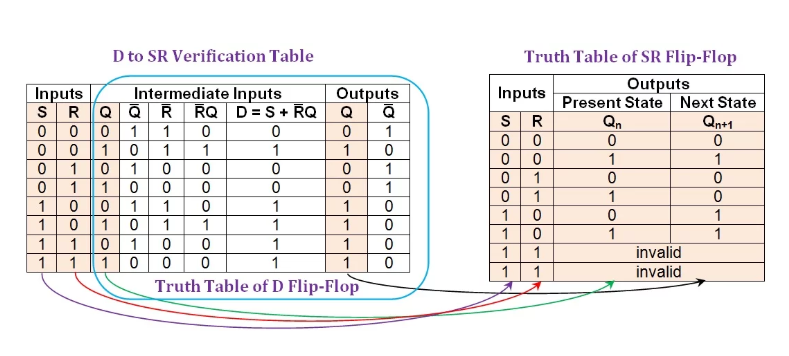

将给定D触发器转换为SR型的过程通过获得表来启动,该表表示存在于SR触发器的真值表中的信息以及由D的激励表传达的信息。拖鞋。这样的表称为D-to-SR转换表,如图1所示。

图1: D-to-SR转换表。

这里我们注意到转换表的最后两行在“D Input”列中有X(Do not Cares)。这是因为使用SR触发器时,S = R = 1的输入组合无效(因为输出将是不可预测的)。

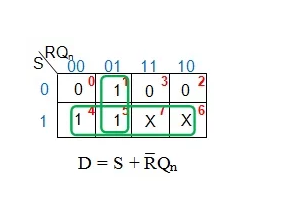

我们的下一步是根据所需触发器S和R的输入以及当前状态Q n获得给定D触发器输入的逻辑表达式。但是,在这样做时,我们需要使用合适的简化技术(例如K-map ICfans)尽可能地简化布尔表达式。这里详细介绍了卡诺的方法。

图2: D输入的K-map简化

从图2中,对于d输入的简化的逻辑表达式被发现是S + RQ Ñ。这意味着,为了使给定的D触发器表现得像所需的SR触发器,我们需要AND Q n否定用户定义的输入R然后将结果与用户定义的输入进行或运算S.

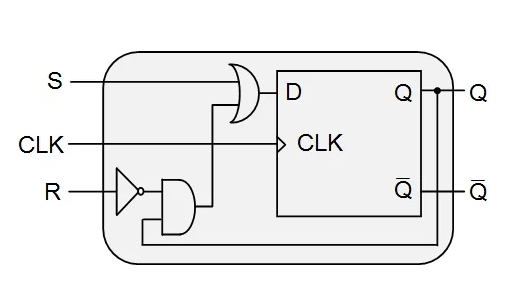

因此,所需的附加组合电路将是一个NOT门,一个AND门和一个OR门。使用这些组件设计的最终系统如图3所示。

图3: D触发器表现为SR触发器

完成转换过程后,我们需要继续进行验证过程。在这里,我们需要为设计的系统编写真值表,并将其条目与SR(所需)触发器的真值表中的条目进行比较。

图4: D-to-SR验证表与SR触发器的真值表之间的比较。

该图显示D-to-SR验证表的第一,第二,第三和第八列(以米色阴影显示)中的所有条目与SR触发器的真值表中存在的条目一致。最后两行看起来有所不同,但它们可以被认为是等效的,因为SR触发器的输出可能由于无效输入组合而为高或低。实际上,我们设计了一个比SR触发器更好的系统,因为当两个输入都很高时它具有可预测的输出行为。

验证表表明转换过程是成功的:给定的D触发器在功能上等效于所需的SR触发器。

将D转换为JK触发器

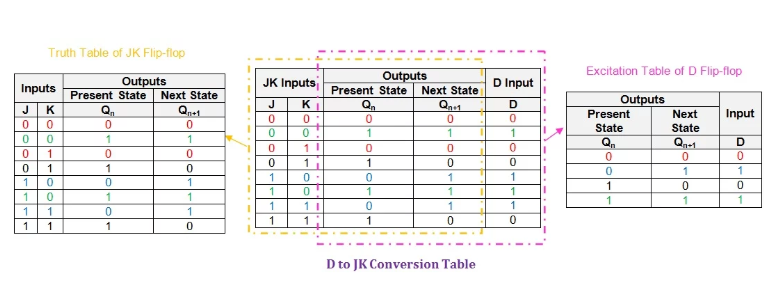

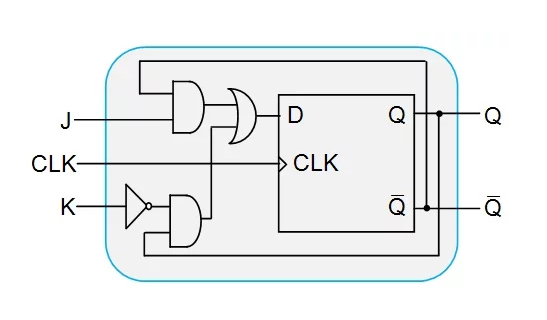

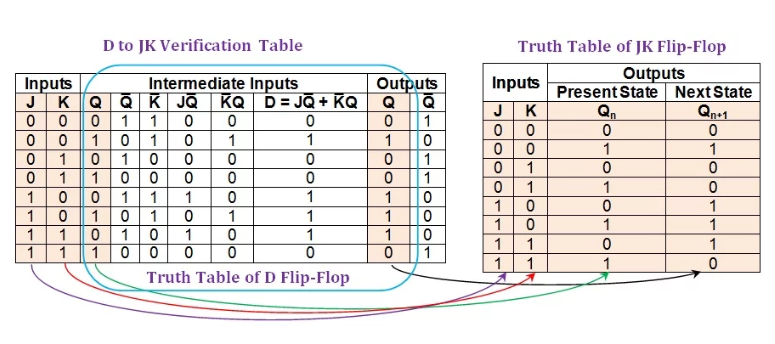

通过使用D-to-JK转换表,可以将给定的D触发器转换为JK触发器,如图5所示。该表共同表示JK触发器的真值表和D触发器的激励表。

图5: D-to-JK转换表。

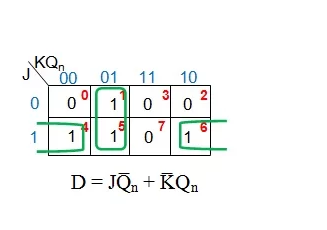

在此之后,我们需要根据J,K和Q n简化D输入的表达式。我们将再次采用K-map技术。

图6:根据J,K和Q n对D输入进行K-map简化

图6显示,为了将D触发器转换为JK触发器,其D输入需要由双输入OR门的输出驱动,其输入为

Ĵ相与本-状态Q的否定Ñ(即Q Ñ)

K(K̅)的否定与当前状态Q n相关

这表明我们需要

一个NOT门 - 否定K.

两个与门,一个获得JQ ñ和其他获得KQ ñ

一个或门,以获得由JQ给出的d输入Ñ + KQ Ñ

因此,得到的系统如图7所示。

图7: 设计用作JK触发器的D触发器

最后,让我们验证我们设计的系统是否像我们期望的那样使用D-to-JK验证表,如图8所示。

图8: D-to-JK验证表与JK触发器的真值表之间的比较。

图8显示D-to-JK验证表的第一,第二,第三和第九列(以米色阴影显示)具有与JK触发器真值表的列中的条目相同的条目。这表明给定的D触发器对于每个输入组合和当前状态的行为与JK触发器完全相同。

因此,我们可以得出结论,转换过程是成功的。

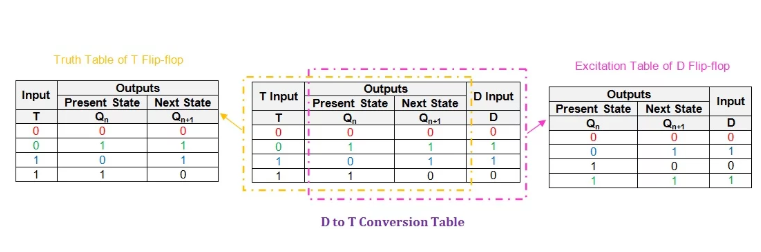

D转换为T触发器

为了将给定的D触发器转换为T型,我们需要获得相应的转换表,如图9所示。这里,D触发器的激励表中的信息作为一部分插入T触发器的真值表。

图9: D-to-T转换表。

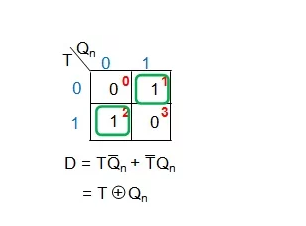

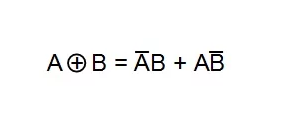

在获得的转换表,接下来的步骤是表达输入,d,在T和Q的术语Ñ。

图10: D的K-map简化,以T和Q n表示

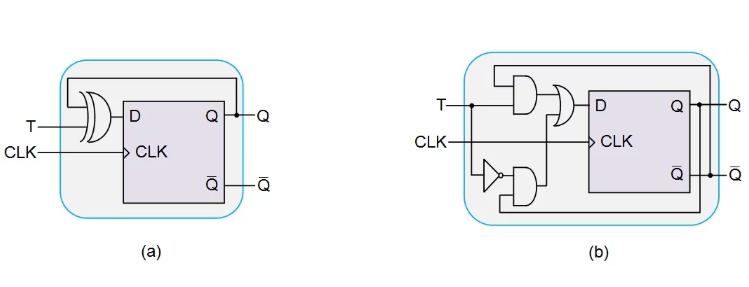

从图10中可以看出,为了将给定的D触发器转换为T型,我们需要通过输入为T和Q n的XOR门的输出驱动其输入引脚(D)。这将导致新的数字系统如图11(a)所示(半导体社区)。

如果我们必须将自己仅限于NOT,OR和AND门,我们将需要遵循以下步骤:

使用AND门来AND用户定义的输入T,以及触发器当前状态Q n的否定。

使用另一个AND门来触发触发器的当前状态,并取消T(作为NOT门的输出获得)。

或者使用双输入“或”门将两个AND门的输出连接在一起。

这导致了图11(b)所示的数字系统。

图11:设计为使用(a)XOR门和(b)仅NOT,OR和AND门的T触发器的D触发器。

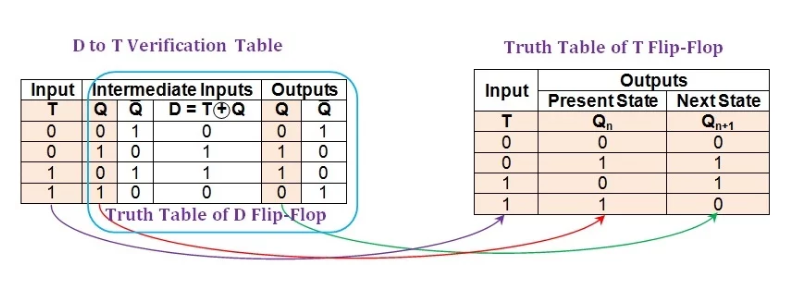

下一步也是最后一步是使用D-to-T验证表验证转换过程,如图12所示。

图12: D-to-T验证表与T触发器的真值表之间的比较。

从图中可以看出,D-to-T验证表的第一,第二和倒数第二列(以米色为阴影)与T触发器的真值表中的列相同。这表明转换过程成功,即给定的D触发器的行为与T触发器完全相同。

虽然我们已经验证了图11(a)中设计的系统,但结论对于图11(b)所示的设计也是有效的,因为

-

把jk触发器转换为t的方法2024-08-28 3832

-

d触发器和jk触发器的区别是什么2024-08-22 4757

-

t触发器和jk触发器的区别和联系2024-02-06 7592

-

双D型触发器-HEF4013B2023-02-15 841

-

图文并茂:D型触发器电路设计教程2021-02-03 13394

-

JK触发器基本教程,讲的超详细!!2021-02-01 17286

-

JK触发器逻辑符号_jk触发器的特性方程2019-11-08 96543

-

主从jk触发器工作原理2019-08-05 43562

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 192157

-

D触发器组成T和J-K触发器电路图2010-09-20 21873

-

JK触发器,JK触发器是什么意思2010-03-08 7413

-

74LS112型双JK触发器芯片引脚图管脚图2009-02-14 82910

全部0条评论

快来发表一下你的评论吧 !