浅析CPLD的工作原理

可编程逻辑

1395人已加入

描述

CPLD(复杂可编程逻辑器件),它是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

它的工作方式和原理与FPGA(现场可编程门阵列)相类似,都是使用硬件描述语言VHDL/Verilog描述逻辑电路功能,然后将代码进行综合,布局,布线等操作,生成比特流文件来描述这些逻辑电路信息,再加载入芯片。因此它也属于硬件开发范畴。

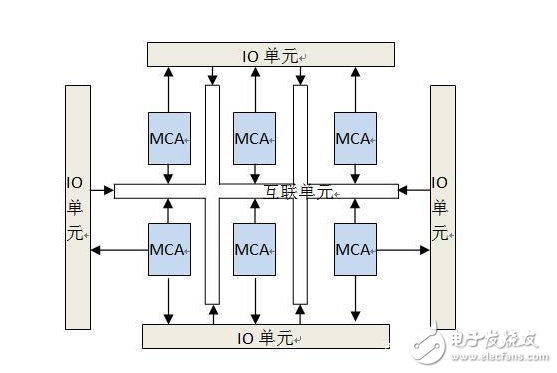

但是CPLD与FPGA的内部组成结构是不同的,它由可编程逻辑宏单元阵列(MCA),可编程互联矩阵单元,可编程IO单元组成。

宏单元结构又由与阵列,或阵列,可编程触发器和多路选择器等电路组成。

图中乘积项阵列是一个与阵列,该阵列的每一个交叉点都是一个可编程熔丝,如果导通就是与逻辑,乘积项选择矩阵是一个或阵列,两者一起完成组合逻辑,后面再跟一个可编程触发器,组成整个最小可编程逻辑单元。

通过编程逻辑单元的比较,可以看出CPLD与FPGA的实现组合逻辑的机制存在本质的区别,前者使用可编程与阵列和或阵列实现,后者使用sram保存逻辑真值表来实现,并且前者一个逻辑单元中只包含一个可编程触发器,而后者一个逻辑单元包含“8”个触发器。

我们知道触发器是实现时序逻辑电路的基本器件,CPLD有丰富的组合逻辑资源(与/或阵列),FPGA有丰富的时序逻辑资源(触发器),因此它们各有所适用的场景。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

感光太阳能灯工作原理。#工作原理大揭秘jf_24750660 2022-11-07

-

FPGA/CPLD同步设计若干问题浅析2009-04-21 4436

-

Kubernetes NetworkPolicy在Calico上的工作原理介绍2019-06-11 1205

-

FPGA与CPLD怎么区分2019-07-01 2600

-

FPGA与CPLD该怎么区分?2019-08-08 2042

-

LED点阵显示控制系统结构及工作原理是什么2021-04-30 2948

-

FPGA与CPLD的辨别和分类2010-10-18 1085

-

浅析三极管三极管工作原理2017-04-17 1657

-

cpld的基本工作原理2017-10-24 22342

-

根据结构特点和工作原理来辨别FPGA与CPLD的区别2020-03-24 6286

-

浅析集成电路的工作原理2023-07-20 3501

-

浅析智能家居照明系统工作原理及应用2023-11-02 969

-

浅析板框压滤机类型构造和工作原理2023-11-03 594

-

浅析工业低功耗红外气体浓度传感器和常规钨丝灯气体浓度传感器的工作原理及其区别2023-12-13 1807

-

浅析干式变压器的工作原理、应用和选型2024-02-18 7270

全部0条评论

快来发表一下你的评论吧 !