边沿触发器工作原理及电路结构

模拟技术

描述

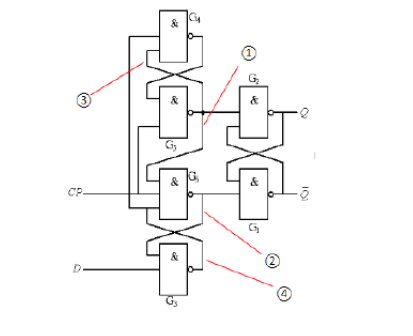

边沿D触发器

触发器是一种时钟控制的记忆元件,触发器具有一个控制输入讯号(CLOCK),CLOCK讯号是触发器只在特定时刻才按输入讯号改变输出状态。若触发器只在时钟由L到H(H到L)的转换时刻接受输入,则称这种触发器是上升沿(下降沿)触发的。

边沿D触发器也称为维持-阻塞边沿D触发器。负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

①为阻塞复位线,②为维持复位线,③为维持置位线,④为阻塞置位线。触发器输出为1时,利用维持置位线和阻塞复位线,保持输出不变。触发器输出为0时,利用维持置位线和阻塞复位线,保持输出为复位状态。

边沿触发器的类型很多,有利用CMOS传输门的边沿触发器、维持阻塞型触发器,有利用门电路传输延迟时间的边沿触发器等。不管哪种类型的边沿型触发器,都能实现触发器的次态仅仅取决于CP时钟脉冲的下降沿(或上升沿)到达时刻输入信号的状态,而与其他时刻触发器输入信号的状态无关。因此,边沿型触发器大大提高了工作的可靠性,增强了抗干扰能力。下面利用门电路传输延迟时间的边沿触发器为例,介绍边沿触发器的工作原理。

工作原理

1)CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。 2)当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5=D,Q4=Q6=D。由基本RS触发器的逻辑功能可知,Q=D。 3)触发器翻转后,在CP=1时输入信号被封锁。这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。因此,该触发器常称为维持-阻塞触发器。总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度。

1、电路结构和工作原理

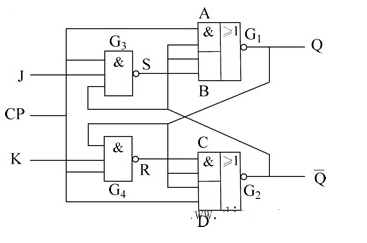

图1所示为利用门电路传输延迟时间的边沿JK触发器。

图1 边沿JK触发器

由图1可知,该电路由两个与或非门G1、 G2和两个与非门G3、G4组成。其中G1、 G2组成基本RS触发器,G3、G4组成输入控制电路。G3、G4门的传输延迟时间大于基本RS触发器的翻转时间。

当CP=0时,G3、G4门被锁定在高电平,输入信号J、K被封锁,即R=S=1。同时与门A、C被封锁,基本RS触发器通过与门B、D传输。此时由于R=S=1,因此基本RS触发器状态保持不变。即CP=0时,无论输入端J、K状态如何,触发器保持原态不变。

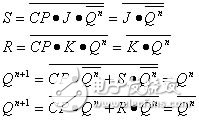

当CP=1时,G3、G4、A、C门均被打开,此时各门电路的输出为

(1)

(1)

可见,当CP=1时,不论输入端J、K状态如何,触发器保持原态不变。

当CP的上升沿到达时(CP从0跳转为1的瞬间),门A、C首先被打开,由于G3、G4、传输延迟的存在,输入端J、K的变化不影响G3、G4的输出,S、R仍为1,此时触发器状态仍然保持原态。当延迟过后,触发器仍然保持原态不变,分析过程同CP=1时。因此,当CP为上升沿时触发器保持原态不变。

当CP的下降沿到达时(CP从1跳转为0的瞬间),由于CP直接加在G1、G2和门外侧的两个与门A、C上,门A、C首先被封锁,其外侧的两个与门B、D的输入端S、R则需要经过一个传输延迟时间才能随CP=0而变为1。因此,在S、R没有变为“1”之前,仍然保持CP下降前的值,即

设CP的下降沿到达前,触发器的状态为Qn=0, =1,输入端J=1,K=0,此时G3、G4的输出为S=0,R=1。当CP的下降沿到达的瞬间,G1门的两个与门A、B各有一个输入为零,故此时G1门的输出Qn+1=1。G1门的输出反馈到G2的两个输入上,与门C的两个输入均为“1”,使G2门的输出

=1,输入端J=1,K=0,此时G3、G4的输出为S=0,R=1。当CP的下降沿到达的瞬间,G1门的两个与门A、B各有一个输入为零,故此时G1门的输出Qn+1=1。G1门的输出反馈到G2的两个输入上,与门C的两个输入均为“1”,使G2门的输出 。G2门的输出

。G2门的输出 又反馈到G1门的输入端。由于G3门的传输延迟时间足够长,可以保证在S消失低电平之前,

又反馈到G1门的输入端。由于G3门的传输延迟时间足够长,可以保证在S消失低电平之前, 的低电平已经反馈到了B门的输入端,使G1门的输出仍然保持高电平。当G3、G4门延迟之后,G3、G4被封锁,输入端J、K的变化不再影响输出,其输出S=R=1,因此基本RS触发器保持原态不变。

的低电平已经反馈到了B门的输入端,使G1门的输出仍然保持高电平。当G3、G4门延迟之后,G3、G4被封锁,输入端J、K的变化不再影响输出,其输出S=R=1,因此基本RS触发器保持原态不变。

当输入端J、K取其他状态的值时,其分析方法相同,请读者自行分析。

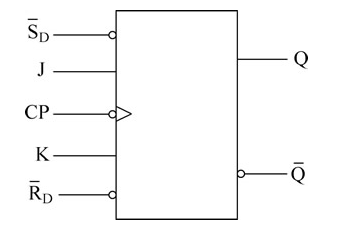

利用上述分析方法,可以得到图6-2-8 所示边沿型JK触发器的特性表如表1所示。其逻辑图形符号如图2所示。

图2 边沿JK触发器的图形符号

根据触发时刻的不同,边沿型触发器又分为上升沿和下降沿触发器两种类型。如果触发器是在时钟脉冲CP的下降沿触发,即为下降沿边沿触发器,逻辑符号中时钟脉冲CP靠边框处的圆圈表示下降沿触发,符号“》”表示边沿触发类型。如果触发器是在时钟脉冲CP的上升沿触发,即为上升沿边沿触发器,逻辑符号中时钟脉冲CP靠边框处没有圆圈表示上升沿触发。

2、动作特点

从上面的分析可知,边沿触发器的次态仅仅取决于时钟脉冲CP的下降沿(或上升沿)到达时输入端的逻辑状态,而与其他时刻输入端的状态无关。这就是边沿触发器的动作特点。这一特点大大提高了触发器的工作稳定性和抗干扰能力,在数字电路中得到广泛的应用。

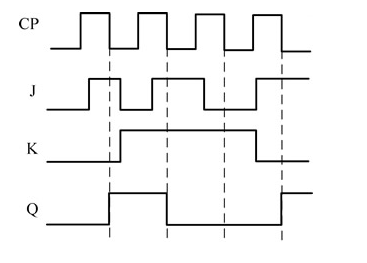

例1 在图3所示的下降沿边沿JK触发器电路中,已知时钟脉冲CP的波形和触发器输入端J、K的波形如图3所示。试画出触发器输出端Q的波形。设触发器的初始状态为0。

图3 例1图

-

同步触发器和边沿触发器的区别2024-08-12 4087

-

边沿触发器的类型有哪些2024-08-11 2405

-

边沿触发器的状态变化由什么控制2024-08-09 2198

-

什么是触发器 触发器的工作原理及作用2019-12-25 5685

-

什么是边沿触发器_边沿D触发器介绍2018-01-31 73474

-

jk边沿触发器工作原理2018-01-30 38776

-

JK触发器工作原理详细介绍2010-03-08 54996

-

CMOS触发器在CP边沿的工作特性研究2009-10-17 2455

-

施密特触发器工作原理2008-01-21 12249

全部0条评论

快来发表一下你的评论吧 !