扰码器(二)串行扰码器综述及设计思路

今日头条

1188人已加入

描述

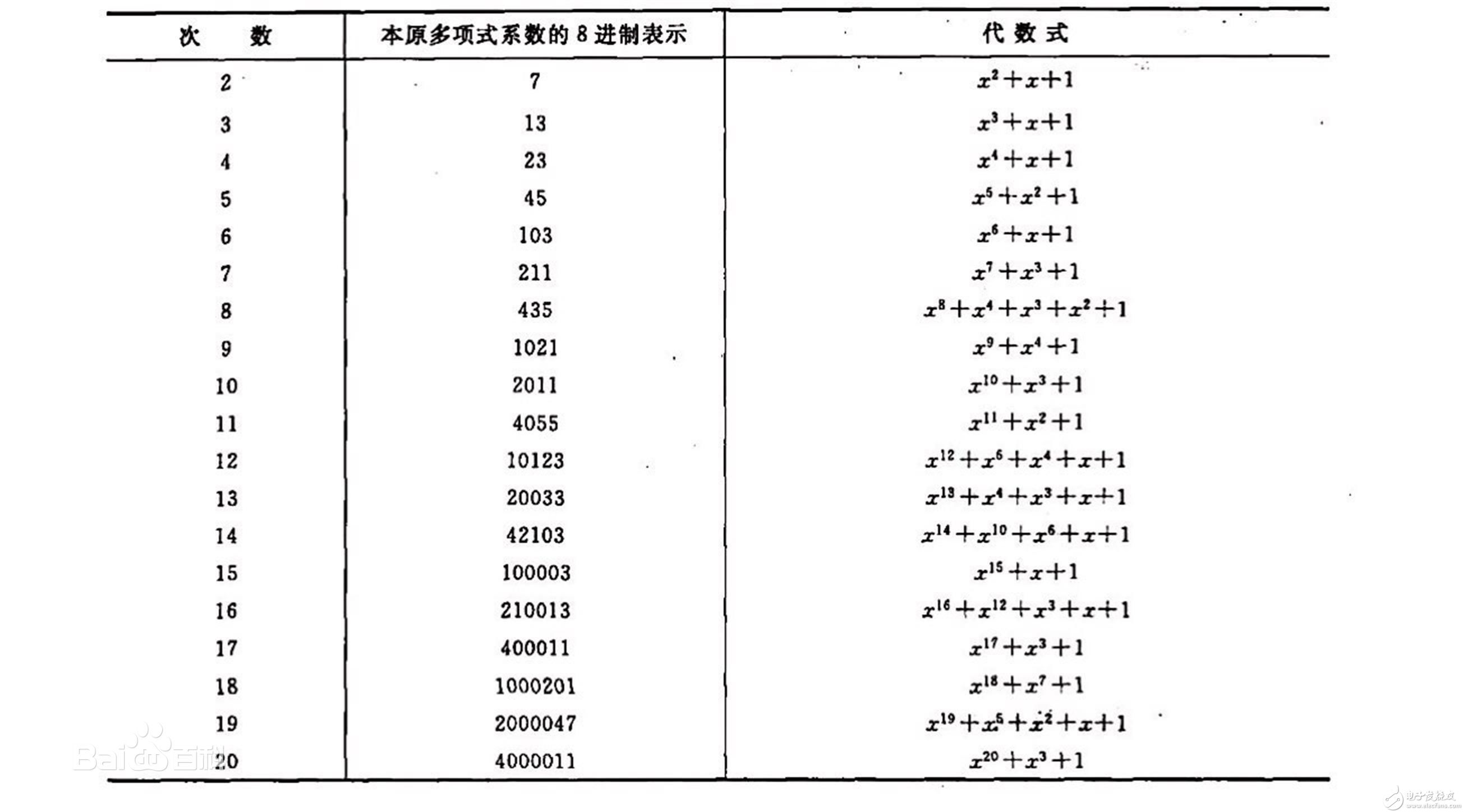

首先扰码器的作用就是用来将有序数据流变成随机(无序)数据流。而且不是简单的无序,是要求扰码之后的数据流是类白噪声数据流。而且扰码器扰码之后,解扰器要解的开,恢复得回去。这就需要我们常说的本原多项式了。这些都是原理性内容不再一一阐述了。

如果要想做扰码器,首先要知道自己的扰码器最长周期是多少位的。例如在我们的工程中,由于扰码只是其中的一个部分,他需要承接上面发送数据的格式,这样一来,根据相关标准中指定的扰码多项式选择这样的一个扰码多项式。如果单纯的去做一个扰码器可以选择其他周期较短较简单的扰码多项式。

确定扰码多项式之后,下一个工作就是设计。

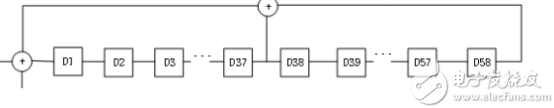

扰码的规则就是根据本原多项式系数为一的项的指数进行扰码。简单话说,扰码当前状态输出的扰码数值,是由当前状态和之前发送状态数值进行模二加法运算(异或)将结果输出。而具体是之前的那个状态呢?就是本院多项式中系数为一的项,如我们上面的例子中系数为1的项指数为39和58,那么我们就要将当前状态和前第39项与58项进行模二加法运算,算出来的值输出。示意图如下。

有些小机灵鬼可能已经发现这个图不就是是个电路图吗?没错,它确实也是一个电路图。由于扰码器每一项输出都与之前的状态有关,我们使用移位寄存器逐项存储扰码后的数据值,对应本原多项式中的系数为1的项数值与输入数值进行模二运算输出为当前数据,并将它存储进移位寄存器中供后面扰码时使用。

就这样串行扰码器就设计出来了

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

全部0条评论

快来发表一下你的评论吧 !