扰码器(三)并行扰码器综述及设计思路

今日头条

1188人已加入

描述

经历了串行扰码器的设计后,我们今天来认真讨论一下扰码器的并行化。

在许多工程项目中,在通信接口的设计中,通信协议对于扰码器的工作频率要求非常高,但是由于串行扰码器是1bit进行的,如果再要求频率过高的话,FPGA是无法实现如此高频率的。所以我们要对其进行并行化处理,以此达到高速的要求。

并行扰码器设计基于串行扰码器,其对应的本原多项式依然是,而其输入输出关系可以由上述扰码器输入输出的逻辑关系推导而出。按规则规范,扰码器与解扰器数据位的输入输出均为64位宽。

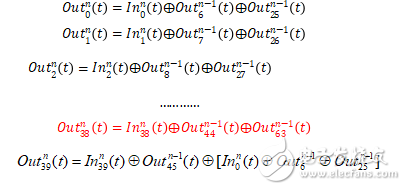

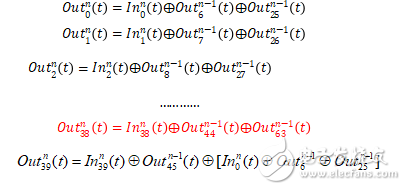

在上述的扰码器中,将反馈移位寄存器中零时刻存储值为为,扰码器输入与移位寄存器中数据与或的结果,即下一时刻输入至第一个寄存器的数据为,输入数据为scram_in。表示第S为寄存器在N时刻的存储值。由扰码器的输入输出关系可推导出在下一时钟到来时,各级寄存器中存储的数值满足以下关系:

(1)

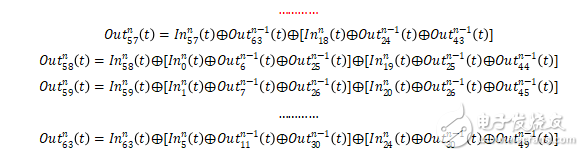

以此类推,在第39个时钟到来时,第39位寄存器寄存器中已经是,故将公式中迭代为该公式,即可进行下次运算。

并行扰码结构就是由上述扰码多项式经过严格推演并进行处理,其结果推导为下式,推导出扰码结果的每一位输出都与当前输入以及在此之前的输出相关。由于后电路的要求,每一位一个扰码输出保持到下一次的扰码操作,作为下一次扰码的前一次输出参与下一轮的扰码操作,保持了扰码的连续性。由于扰码/解扰过程与本原多项式都有关,且扰码过程中每一位的输出都与其对应的寄存器数据位有关,故扰码解码实现时必须选择相同的本原多项式和初始值。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- FPGA设计

全部0条评论

快来发表一下你的评论吧 !