简谈PCIe的软件配置方式

描述

大家好,又到了每日学习的时间了,今天我们来聊一聊PCIe的软件配置方式。

关于PCIe的软件配置和初始化

PCIe设计出来考虑了和pci兼容问题。所以PCIe的软件配置方式可以沿用PCI的配置方式。当然,由于特殊性,也有自身独特的配置方式。所以PCIe模块的访问方式有如下两种:

1、 PCI 兼容的配置方式。

2、 PCI Express enhanced 配置机制。

PCI兼容方式是在PCI章节已经提过,PCIe与其完全兼容。这里主要描述PCIE高级配置机制。

PCIe的配置空间

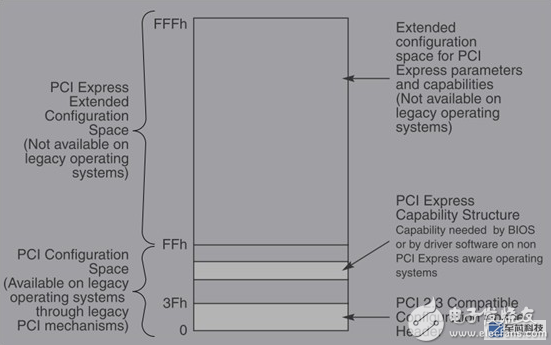

PCIe的配置空间是兼容PCI的,但是在PCI的基础上增加了不少register。从256增加到4Kbytes的大小。如下图所示,PCIe的配置空间。

其中,PCIe的配置空可以分成PCI兼容部分和扩展部分。PCI兼容部分在前面256byte区域,完全可以使用PCI配置机制来访问。而扩展部分的register,使用PCI配置方式无法实现,则可以通过PCIe 高级配置方式完成。

PCIe高级配置机制

PCIe enhanced configuration mechanism的主要原理是将pcie的所有4K bytes 映射到memory地址上,这样,通过访问memory的方式即可读写PCIE的配置空间。当然,通过此方式读memory时候,最好考虑到4字节对齐的问题,否则有可能出错。

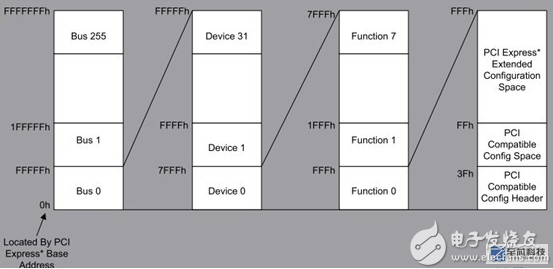

在正常的访问过程中,可以访问这一部分的memory来配置pcie,而这部分memory在哪里呢?芯片组中会定义一个base address,而base address开始的256MB的空间内则是总线上所有PCIe设备的配置空间对应的register。

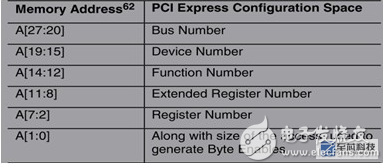

上图是PCIE总线高级配置结构图,很明显可以看出是PCIE配置空间映射的memory空间为[XbaseAddress +0 àXbaseAddress +FFFFFFFh]。那么实际的地址线如何对应呢?如下图所示:

在程序中的表达和操作是这样的:

1、计算出PCIe设备配置空间中寄存器的地址:Register address = PCIe_Base + (BusNO * 1MB) + (DeviceNO * 32KB) + (FuncNO* 4KB) + (Reg).

2、使用memory 读写周期完成register的读写。

PCIE配置空间register

详细的register解读,请阅读PCIe spec或者参考一份X86架构的芯片组datasheet。

今天就聊到这里,各位,加油。

- 相关推荐

- 热点推荐

- F

-

如何选择适合的PCIe配置2024-11-26 2375

-

图解PCIE原理(从软件角度)2021-12-17 1836

-

pcie2019-11-11 2938

-

PCIe总线的复位方式是什么?2019-10-16 4126

-

PCIe总线的两种复位方式2018-12-30 24751

-

简谈PCIe的软件配置方式2018-07-27 4235

-

PCIE MSI中断的配置2018-06-21 4042

-

简谈PCB设计软件对比2018-06-20 5911

-

关于dm8168的PRCM使能pcie寄存器区域,需要PRCM配置打开pcie,为什么配置之后还是不能访问pcie的寄存器?2018-05-25 2510

全部0条评论

快来发表一下你的评论吧 !