VIO比chipscope有多大优势?

描述

debug,尤其是通信芯片的debug,可以有很多的方法。一个数据帧从进入到输出,可以在通路上的关键节点处设置监测如各种计数器等,可通过VIO(xilinx)定时上报实时状态。可以把VIO的各个信号线设置成类似于CPU总线的结构,监测计数器或者状态寄存器编成相应的地址,轮询读取回PC,在PC上通过TCL或者其它语言捕获数据。甚至可以将多个FPGA芯片都通过VIO进行调试,远程操作,效率也可以大大提升。另外,也可以设置专门的测试帧,在里面打各种不同大小的闭环,层层检测,发现问题。

这个VIO比chipscope有多大优势?

原理是一样的,不同的就是可以方便操控,可以写脚本抓取数据,还可以远程操控。VIO有输入也有输出,可以实时的配置寄存器。http://xilinx.eetrend.com/blog/11987,VivadoVIO (virtual input output)虚拟IO使用;

一、使用方法概述

一般情况下VIO用在设计中,可以提供模拟IO(我们主要用到模拟输出接口的功能)。如图1所示,红框内vio_0模块的两个输出probe_out[0:0]和probe_out[7:0]都可以接到其他模块直接使用,但是我们不需要用到板子上的实际接口(比如按键)。那么为什么我们在电脑上点一点鼠标,就可以将数据传递到FPGA内部呢?数据是通过什么传输到FPGA内部?答案是JTAG,电脑上的VIVADO软件可以通过JTAG软件与FPGA实现通信,这就是VIO模块在FPGA内部模拟IO引脚的原理。

图1 VIO IP核

1、VIO IP核的配置

下面用实际例子说明VIO IP核的配置过程:

在某设计中,需要使用按键出发,但是板子上没有设计按键,所以需要使用VIO模拟按键输入还有其他信号的输出。具体过程如下:

(1)例化VIO IP核 ;

(2)参数配置,配置输入探针数量和输出探针数量,如图2所示。分别可以设置0-256个。(一般输入探针用不到,最常用的是输出探针,在这里这两种探针都在图里体现了)。

图2 探针数量设置

(3)配置输出探针数据位宽及初始值

输出探针的数据位宽,及初始化数据(in hex)配置如图3所示

图3配置输出探针数据位宽及初始值

3、 VIO IP核的例化

VIO IP核代码实例化如下图所示。

ILA_wrapper ILA(

.clk ( ),

.probe0 (),

.probe1 (),

.probe_out0 (),

.probe_out1 (),

.probe_in0 ()

);

4、 VIO IP核的使用

在hw_vio界面加入输出探针,并且配置对应的参数,此时FPGA内部的输出探针就会相应地发出信号,如图4所示。

图4 VIO IP核的使用

二、使用VIO实现大量寄存器读写

1、背景

在FPGA调试中,如果没有CPU接口及操作系统,但同时希望能够有一种类似于有CPU且可以实时在线读写FPGA内部状态寄存器或者配置FPGA内部寄存器的功能,就可以采用VIO来实现一个模拟的CPU接口,以下进行详细的介绍。

2、 原理框图及VIO字段定义

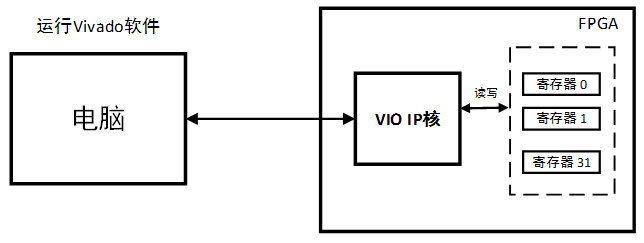

在Vivado 2016.2 软件环境,Zedboard硬件平台下,实现了一个示例工程,该工程的功能是,电脑运行Vivado软件,并通过Jtag与zedboard相连,利用VIO模拟CPU接口,实现寄存器读写功能(寄存器数量为32个,位数为32位),如图5所示。

图5原理框图

其参数配置说明如下:

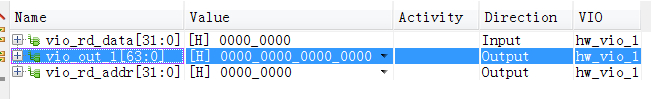

如图6所示,vio_out_1的前32位是写地址,后32位是写数据;

图6 VIO 写地址与写数据

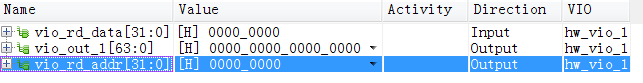

如图7所示,vio_rd_addr代表读地址;

图7 VIO 读地址

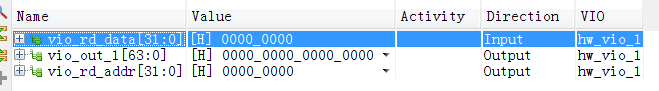

如图8所示,vio_rd_data代表读数据

图8 VIO读数据

3、操作示例

这里给出一个寄存器读写的例子,在这里不用tcl脚本,直接用图形界面,使用更加方便。

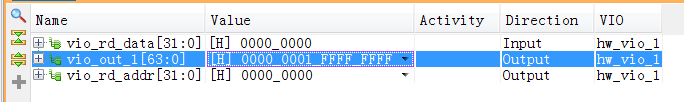

(1)给地址为1的寄存器写入数据32'hffff_ffff,即配置vio_out_1[63:0]为64'h0000_0001_FFFF_FFFF,如图9所示。

图9 VIO 写入数据

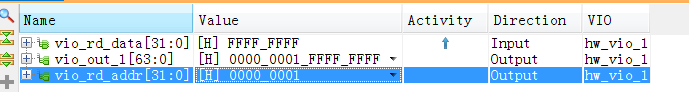

(2) 将读地址设置为1,观察读数据变化,如图10所示。

图10 VIO读数据

观察图10可以发现,配置读地址vio_rd_addr为32'h0000_0001后,读数据vio_rd_data[31:0]由图9中的32'h0000_0000变为图10中的32'hffff_ffff,与写入的数据相同,寄存器读写操作成功。

三、源代码

1、约束文件源码

set_property PACKAGE_PIN Y9 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

上述源码及约束文件适用于Xilinx的Zedboard开发板,已上板验证。另外,上面仅是原理性的简单演示,可以把寄存器应用于自己设计中的各个内部关键模块中,调试的过程中,实时的从VIO接口获取数据,或者动态的配置FPGA内部的寄存器,使其按照寄存器约定的功能运行。虽没有CPU,却等效有了CPU,可大大提高FPGA调试的效率。VIO占用资源情况与chipscope类似。

-

XILINX FPGA Debug with VIO and TCL2012-03-08 5191

-

ISE VIO的使用2019-04-27 7384

-

使用VIO IP在ISE Design SUite软件中调试时遇到以下错误该怎么办?2019-08-02 2803

-

Chipscope中的ILA,VIO和ATC2有什么区别?2020-03-31 2905

-

FPGA调试工具-chipscope2009-03-23 1108

-

Chipscope学习教程2011-05-10 1056

-

CHipScoPe使用2015-11-23 732

-

Chipscope的使用2016-03-21 689

-

ChipScope使用示例2016-06-07 703

-

Xilinx FPGA ChipScope的ICON/ILA/VIO核使用2017-02-09 1684

-

ise中chipscope的使用2017-09-15 980

-

SDK和ChipScope配合工作2017-11-22 3603

-

chipscope使用教程以及FPGA在线调试的方法2018-03-02 1351

-

Vivado之VIO原理及应用2021-09-23 11789

-

VIO在chipscope上的使用2022-06-12 3810

全部0条评论

快来发表一下你的评论吧 !