PCB设计中通过叠层计算阻抗控制时需要注意的四个问题

描述

阻抗控制PCB

在高频应用中,信号不会因为它们在PCB中的路径而降级。

在PCB设计中通过叠层计算阻抗控制时需要注意的四个问题

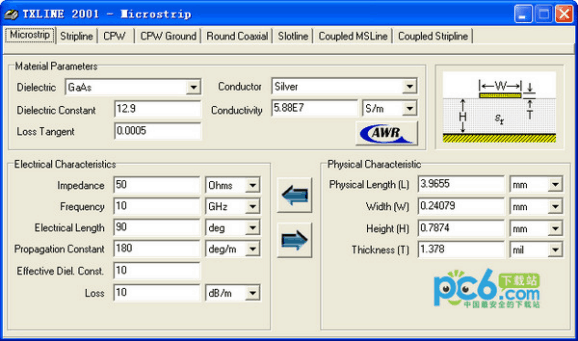

在高速PCB设计过程中,堆栈设计和阻抗计算是迈向顶端的第一步。阻抗计算方法非常成熟,不同软件的计算方法也没有差别。阻抗计算和过程之间的一些“权衡”相对麻烦。主要目的是实现我们的阻抗控制目的,同时也确保处理方便,并最大限度地降低处理成本。

下面我们总结一下设计时阻抗计算的一些注意事项PCB层叠起来可以帮助您提高计算效率。

线宽相当宽,不太好。

因为在这个过程中有一个很薄的限制,所以宽度没有限制,所以如果你为了调整阻抗调整的线宽而稍后达到极限,那么要增加它会很麻烦成本或放宽阻抗控制。因此,计算的相对宽度意味着目标阻抗略低,例如,单线阻抗为50欧姆。我们可以计算到49欧姆,并尽量不计算到51欧姆。

整体呈现趋势

整体呈现出一种趋势。在我们的设计中我们可能有多个阻抗控制目标,所以整体太大或太小,所以不要看起来类似于100欧姆太大,90欧姆太小而不能大而小。

考虑残余铜率和胶水量

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- pcb

- PCB设计

- 可制造性设计

- 华强pcb线路板打样

- 华秋DFM

-

在PCB设计中需要注意哪些方面以抑止电磁辐射呢?2023-11-23 1739

-

PCB设计主要需要注意哪些方面2023-04-07 1637

-

高频PCB设计需要注意的细节2022-08-08 2788

-

PCB设计要注意什么2020-07-12 1837

-

PCB阻抗控制和叠层设计2019-05-30 2009

-

PCB设计中叠层算阻抗时需注意哪些事项?2019-05-16 3687

-

PCB设计中叠层设计和阻抗计算需要注意的4点2018-12-01 4338

-

总结了PCB设计叠层算阻抗的4大注意事项 帮助提高计算效率2018-01-22 6694

-

PCB叠层设计及阻抗计算2016-06-02 20282

-

PCB叠层设计2016-05-17 4652

-

高速PCB设计的叠层问题2009-05-16 867

-

pcb设计中需要注意哪些问题?2009-03-20 1751

全部0条评论

快来发表一下你的评论吧 !