边界扫描与电路板测试技术

测量仪表创意

描述

引言

电子器件的生产商和电子产品的制造商都在倾向于采用最新的器件技术,如BGA、CSP(芯片规模封装)、TCP(倒装芯片封装)和其它更小的封装,以提供更强的功能、更小的体积,并节省成本。电路板越来越密、器件越来越复杂、电路性能要求越来越苛刻,越来越难的接入问题导致了工业标准IEEE 1149.1——边界扫描的诞生。边界扫描测试BST是一种可测试结构技术,它是在芯片的I/O端上增加移位寄存器,把这些寄存器连接起来,加上时钟复位、测试方式选择以及扫描输入和输出端口,而形成边界扫描通道。每个IEEE 1149.1兼容的器件,都包括一个4线或5线的测试端口(TAP)、一个状态机(TAP控制器)和由边界扫描单元构成的边界扫描移位寄存器。其中TAP控制器用于控制边界扫描测试的执行。边界扫描描述语言(BSDL-Boundary-Scan Description Language)是VHDL语言的子集。测试软件开发系统使用BSDL文件进行测试生成、分析、故障诊断和在系统编程。

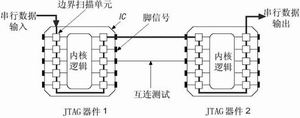

图1 边界扫描用于互连线测试

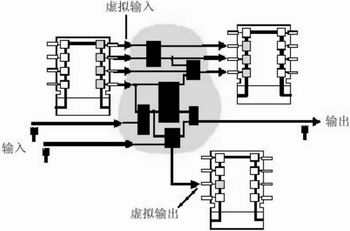

图2 集群测试

边界扫描在板级测试中的应用

边界扫描在板级测试中,主要是对PCB上器件间互连线和管脚的故障进行检测和隔离,对在系统编程器件进行编程。测试边界扫描板的通用测试策略是:

?执行板级边界扫描基本结构完整性测试。

?使用Extest指令,施加激励和检测响应,进行边界扫描器件间互连的测试,测试时将非边界扫描器件设置到安全状态。

?对非边界扫描器件进行测试,如集群测试、RAM测试等。

在正常工作模式,带边界扫描功能的IC好像没有实现其特定功能。然而,当要进行测试或在系统编程时,器件的扫描逻辑被激活,通过菊花链将多个具有JTAG接口的器件串联起来,组成一个扫描链,使用单组测试向量实现对整个电路板的完整测试,如图1所示。

边界扫描测试对于采用复杂表面贴装技术的电路板功能测试也是一种较好选择,它能快速剔除产品的制造故障,让功能测试真正进行功能性故障的查找。当前的主流在线测试和飞针测试设备也都兼有边界扫描测试功能。

尽管很多使用中的器件可以使用BST技术,但仍有部分电路没有边界扫描功能。Teradyne公司的边界扫描测试软件VICTORY,可在其在线测试ATE上运行,其中模块VCCT (Virtual Component and Cluster Test 虚拟器件和集群测试)的工作原理是:VCCT将边界扫描器件的扫描单元作为一个虚拟的ATE测试通道,去驱动激励非边界扫描逻辑电路,然后测试响应。VCCT可以组合虚拟通道和真实的ATE通道进行驱动和检测。用VCCT进行单个器件或集群(Cluster)测试时,关键的任务是定义测试目标的输入和输出,如图2所示。

JTAG接口在FPGA中的应用

FPGA中的JTAG接口,除支持边界扫描测试外,还具有在系统编程(ISP)和逻辑分析功能(SignalTap)。

ISC和ISP

ISC(在系统配置)或ISP是IEEE 1149.1的主要新应用。如Altera公司的MAX7000系列EPLD就具有在系统编程功能,可用在线测试设备(ICT)或下载电缆,通过JTAG接口在板级对可编程器件进行在线测试和编程,简化制造流程。

SignalTap

在Altera公司的Stratix、Excalibur、APEX II等器件中,通过JTAG接口,实现了SignalTap II嵌入式逻辑分析仪功能。SignalTap II是二次生成(second-generation)的系统级调试工具,能捕获和显示SOPC中的实时信号特性,由软IP核、编程硬件和分析软件构成,通过JTAG接口下载FPGA配置数据和上载捕获的信号数据。通过实时板级测试,减少功能验证时间。

JTAG接口在DSP器件中的应用

在DSP器件中,使用JTAG接口主要有两种工作模式:边界扫描模式和仿真模式。例如TMS320C6000系列中的JTAG端口由7到17个信号组成,其中5个信号为IEEE 1149.1标准信号,仿真信号EMUn用于选择芯片的工作模式。芯片具有两个TAP,一个用于边界扫描,一个用于仿真。

关于边界扫描的DFT问题

器件选择

?选择IEEE 1149.1兼容的器件:当前一些大规模的集成电路都带有JTAG接口,采用1149.1兼容的器件,能增加边界扫描测试的覆盖率。

?双功能的JTAG端口:尽量避免选择带双功能JTAG端口的器件。这些器件的双功能引脚,在上电时默认为内核功能模式,通过预定义的JTAG使能引脚,将双功能引脚切换到JTAG模式,因此,设计师必须确认在进行板级边界扫描之前,能够访问和控制JTAG使能脚。

?所有IEEE 1149.1兼容的器件必须支持强制的SAMPLE/PRELOAD,EXTEST和BYPASS指令,并最好也支持可选的HIGHZ和IDCODE指令。

?对于CPLD器件,建议采用IEEE 1532兼容器件,这样可使来自不同厂家的CPLD器件同时进行配置。

扫描链布局

?JTAG控制信号的连接:TCK、TMS和可选的TRST并行连接,TDI、TDO信号将边界扫描器件组成一个菊花链。

?分区:(1)为了满足第三方调试/仿真工具的要求,有些器件(如DSP)必须位于同一个分离链中。(2)为了使不同的FPGA和CPLD厂商的在系统配置软件工具同各自器件良好通信,不同公司的器件必须位于不同链中。(3)不同的逻辑系列器件(如ECL/TTL)放在不同的链中。(4)为有利于测试分区、诊断分辨率的提高或优化测试向量的执行,应对器件进行分区。(5)在系统环境中,提供到背板接口的器件应进行分区,这有利于进行板到板互连测试时优化测试向量的执行。

?尽可能将边界扫描链连接到边缘连接器,这样可不需要针床,避免因不清洁导致的接触不良,有利于背板环境下的系统级访问。

?对于高速的JTAG应用,如SDRAM测试、FLASH编程等,TCK的速度高于10MHz,建议使用一个阻抗匹配的RC网络端接(通常采用60-100Ω的电阻和100pF的电容串接),所有其它的输入使用一个弱的上拉电阻(10kΩ)。为了抑制反射,在菊花链的最后一个TDO引脚串接一个22Ω的电阻。

?通过放置一个0Ω的旁路电阻,可实现对边界扫描器件的物理旁路。有时由于上市时间的压力,边界扫描器件并未实现其功能和对其进行测试,如果它是扫描链中的一部分,将导致电路板上该链中的剩余器件无法进行边界扫描测试。这时可以使用旁路电阻对单个器件和多个器件进行旁路。

?最好对进入板上的所有IEEE 1149.1输入信号进行缓冲,以保证信号的完整性,特别是TCK和TMS。一个通用的规则是,如果电路板线长度相对较短,74244型缓冲器可扇出4~6个器件,如果缓冲器和边界扫描器件间导线较长(大于10cm),建议一个缓冲器扇出1~2个器件。

对非边界扫描器件的控制

?对非边界扫描逻辑控制信号的访问:为了防止测试时的信号竞争导致器件损坏或测试不可靠,非边界扫描器件的控制信号必须连到边界扫描单元,以实现对该器件的非使能控制。

?时钟信号的控制:有时需要对同步存储器读写的时钟信号进行控制,用测试时钟替代或将时钟关断。

?对连接器的测试,可将连接器的引脚接至边界扫描器件的扫描单元,通过在连接器上外接的短接器,实现直通测试。

对FPGA器件

?IEEE 1149.1只提供了静态测试能力,对于高速应用的BIST,可以充分利用FPGA对软IP内核的支持能力和可重新配置能力,在电路板装配阶段,将FPGA配置为带BIST功能的内核,实现全速自测试,在系统集成阶段和产品发运时,将FPGA配置为其原有的正常功能。

结语

IEEE 1149.1很好地解决了微型器件封装、高密度电路板探测等问题,是内置自测试(BIST)采用的主要技术。为提高电路板测试的故障覆盖率、降低测试成本,在电路板的设计初期,就应考虑电路板的测试策略,采用可测试性设计方法,借助测试软件进行可测试性分析、评估和优化,以提高TPS的开发效率,增强电路板的可测试性。

-

边界扫描测试技术介绍2022-02-17 1142

-

JTAG(四) 边界扫描测试技术2021-12-20 982

-

DSP电路板测试中的边界扫描技术研究综述2021-04-13 995

-

边界扫描测试解决方案的原理及应用分析2020-04-13 13625

-

一种新的PCB测试技术:边界扫描测试技术2018-09-10 2840

-

针对含DSP电路板的测试方法与诊断分析2018-09-05 9616

-

边界扫描测试的基本原理及其测试系统的设计2017-12-01 1307

-

边界扫描测试技术在带DSP芯片数字电路板测试中的应用解析2017-11-03 1552

-

简述BSDL边界扫描语言,BSDL边界扫描语言的应用2017-04-19 9354

-

基于边界扫描技术的板级测试分析2012-05-30 1391

-

基于边界扫描的电路板测试系统2011-05-18 2146

-

基于广义特征分析与边界扫描技术的混合信号测试系统2010-11-19 777

-

基于边界扫描的电路板快速测试系统设计2010-01-20 740

-

VXI边界扫描模块接口电路的设计2009-10-10 505

全部0条评论

快来发表一下你的评论吧 !

赚取积分