绝缘体上硅(SOI)驱动芯片技术优势及产品系列

描述

在之前的技术文章中,介绍了驱动芯片的概览和PN结隔离(JI)技术,本文会继续介绍英飞凌的绝缘体上硅(SOI)驱动芯片技术。

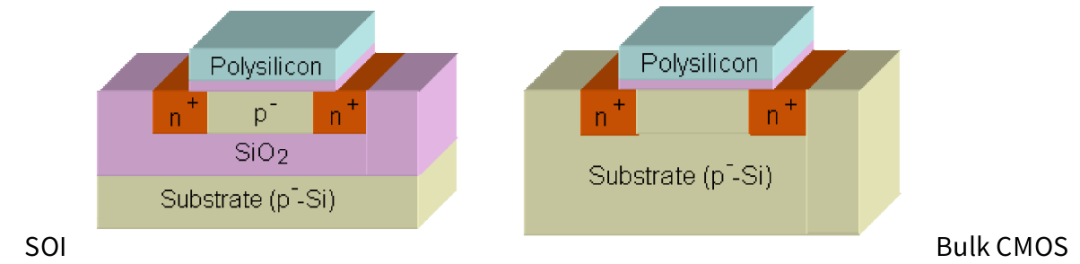

高压栅极驱动IC的技术经过长期的发展,走向了绝缘体上硅(silicon-on-insulator,简称SOI),SOI指在硅的绝缘衬底上再形成一层薄的单晶硅,相对于传统的导电型的硅衬底,它有三层结构,第一层是厚的硅衬底层,用于提供机械支撑,第二层是薄的二氧化硅层,二氧化硅是一种绝缘体,从而形成一层绝缘结构,第三层是薄的单晶硅顶层,在这一层进行电路的刻蚀,形成驱动IC的工作层。

图1.绝缘体上硅SOI(左图)与传统体硅(Bulk CMOS)(右图)结构的比较

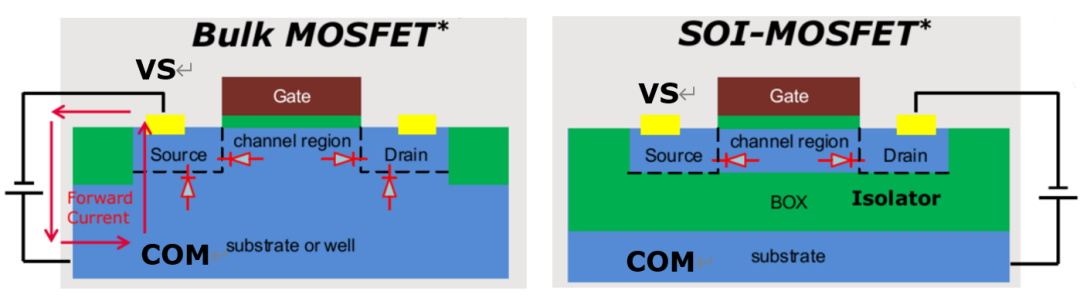

SOI在1964年由C.W. Miller和P.H. Robinson提出,经过几十年的发展,逐渐成熟。英飞凌采用了SOI的独特设计的栅极驱动IC,从设计上带来了诸多优势。其中,最大的优势在于,SOI的二氧化硅的绝缘层,能够彻底消除体硅(Bulk CMOS)结构中衬底中的寄生PN结,从而消除了闭锁效应,提高了驱动芯片耐受负压的能力。

图2.传统体硅(Bulk CMOS)(左图)与绝缘体上硅SOI(右图)寄生PN结的比较

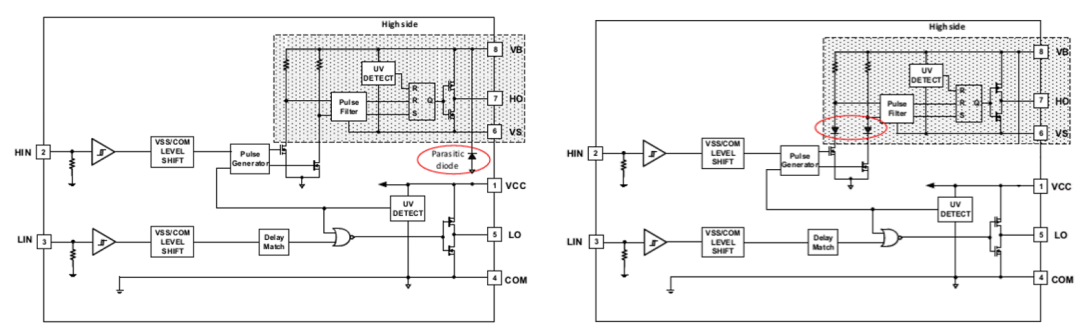

从栅极驱动IC的设计结构上,如图3所示,可以清楚的看到相关电路的影响,在体硅(Bulk CMOS)的设计中,对于高边电路,衬底连接COM电位,MOS的源极SOURCE连接VS电位,因为衬底与VS之间存在一个寄生二极管,从而在某些工况下,当COM的电位高于VS的电位时,寄生二极管会导通,产生无法控制的电流,从而对电路的可靠性产生影响。在绝缘体上硅SOI的驱动IC中,因为二氧化硅绝缘层的存在,消除了连接COM和VS的寄生二极管,从而极大提升了驱动IC的可靠性。

图3.传统体硅(Bulk CMOS)(左图)与绝缘体上硅SOI(右图)寄生PN结对设计的影响

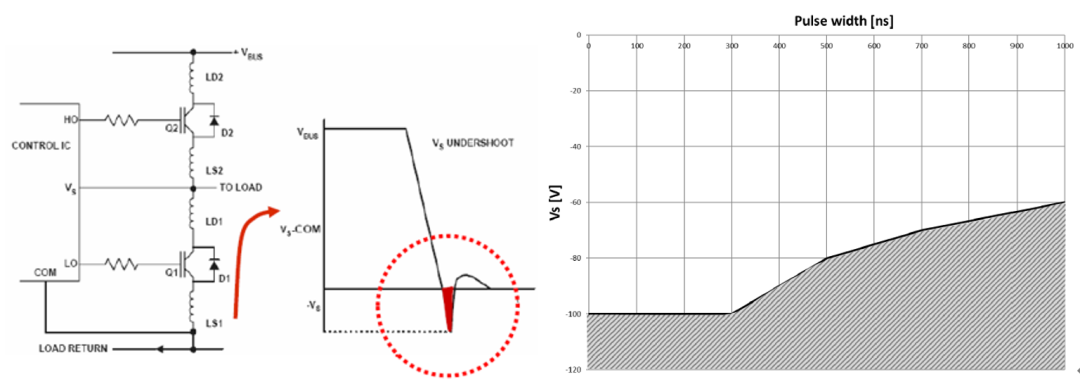

驱动芯片的耐受负压(VS的电压低于COM)的能力,对于电机驱动应用,或者桥式电路带感性负载的应用情况,都非常重要。如图4所示,当上管Q2关闭的时候,负载电流切换到下管D1,此时电流从负母线流向负载。考虑动态的情况,在D1上的电流逐步建立的过程中,在VS~COM之间,会产生由Ls1和Ld1的感生电压,以及Q1的二极管的导通电压,总的电压等于这三个电压的叠加,方向上电压在COM为正,VS为负。因为这类应用中,负压现象不可避免,所以驱动IC耐受这个负压的能力越高越好,图4的右图可以看出,英飞凌的SOI驱动IC,抗负压的能力可以达到-100V/300ns或者-60V/1000ns,这种抗负压的能力远远大于JI设计的驱动IC。

图4.桥式电路中负压的产生,及英飞凌的SOI驱动的负压耐受工作区

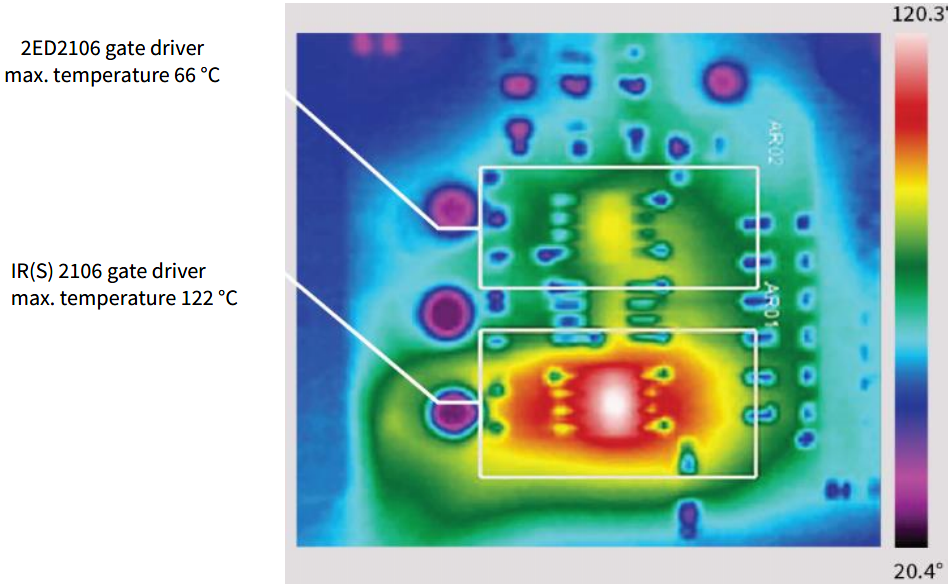

另外,SOI的结构中,因为寄生PN结的消失,器件的寄生效应减小,器件的开关损耗也可极大的降低,并且由于漏电流的减小,静态功耗也可以得到降低,从而使得采用SOI设计的驱动IC,工作频率能够更高,整体损耗更小。图5对比了300kHz的开关频率下,2ED2106(SOI设计)与IR2106(Bulk CMOS设计)的温升对比,可以看到,2ED2106的最高温度只有66°C,而IR2106的温度高达122°C。

图5.绝缘体上硅SOI与传统体硅(Bulk CMOS)的驱动IC的温升比较

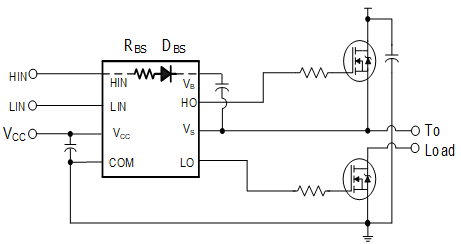

再次,SOI因为存在良好的介质隔离,更方便进行集成。英飞凌的SOI的驱动IC集成了自举二极管,从而能够节省掉以前需要外加的高压自举二极管,从而节省系统成本。

图6.绝缘体上硅SOI集成自举二极管示意图

综上所述,绝缘体上硅SOI是栅极驱动器的一次技术飞跃,具有负压耐受能力强、损耗低、集成自举二极管等一系列的优异特性。

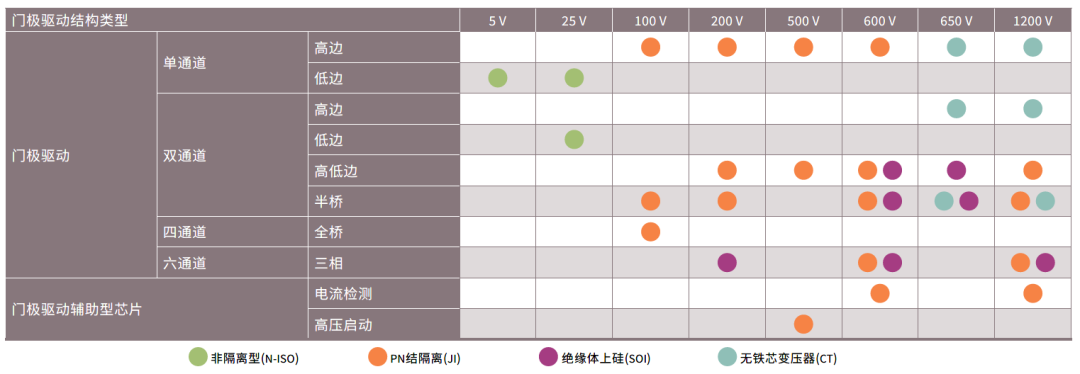

英飞凌已经推出了大量的绝缘体上硅SOI的驱动IC,电压覆盖200V至1200V,结构有高低边驱动、半桥及三相桥。可以点击文末“阅读原文”,查询相关的型号。

-

AGM Micro推出STM32兼容MCU产品系列2023-12-29 0

-

AGM Micro发布兼容STM32的MCU产品系列2023-12-29 0

-

9.3 绝缘体上的单晶硅薄膜SOIjf_75936199 2023-06-24

-

用SOI技术提高CMOSSRAM的抗单粒子翻转能力2010-04-22 0

-

SOI技術介紹2011-07-06 0

-

常见几种SOI衬底及隔离的介绍2012-01-12 0

-

FD-SOI(全耗尽型绝缘层上硅)2016-04-15 0

-

无线测量系统的技术优势2019-07-22 0

-

绝缘体上硅有什么优点?2020-03-19 0

-

UWB的技术优势是什么?2021-05-28 0

-

基于FD-SOI的FPGA芯片有哪些技术优势及应用?2021-06-26 0

-

英飞凌的SOI驱动芯片有哪些优点?2019-07-24 5002

-

绝缘体上硅(SOI)驱动芯片技术优势及产品系列2022-04-13 3767

-

无磁芯变压器(CT)隔离驱动芯片技术优势及产品系列2022-04-20 833

全部0条评论

快来发表一下你的评论吧 !