技术资讯 | 开关稳压电路中的寄生噪声

描述

所有的PCB 布局都有寄生因素,但这些因素并不会总是给您的电路带来重大问题。在某些电路中,它们可能非常麻烦,并且需要一些额外的电路来防止由寄生因素引起的噪声问题。典型的例子是开关稳压电路,它在组件和 PCB 布局中需要考虑重要的寄生参数。寄生效应在开关稳压电路的 PCB 布局中的以下区域中特别突出:

开关 MOSFET 的端子和主体中的电感和电容

反馈回路和高 dI/dt 回路中的回路电感(输入和输出)

PCB布局中开关节点和其他导体之间的互电容

本文向大家介绍一些可用于控制源自这些寄生效应的噪声问题的电路设计和布局策略。

开关稳压电路中的寄生问题

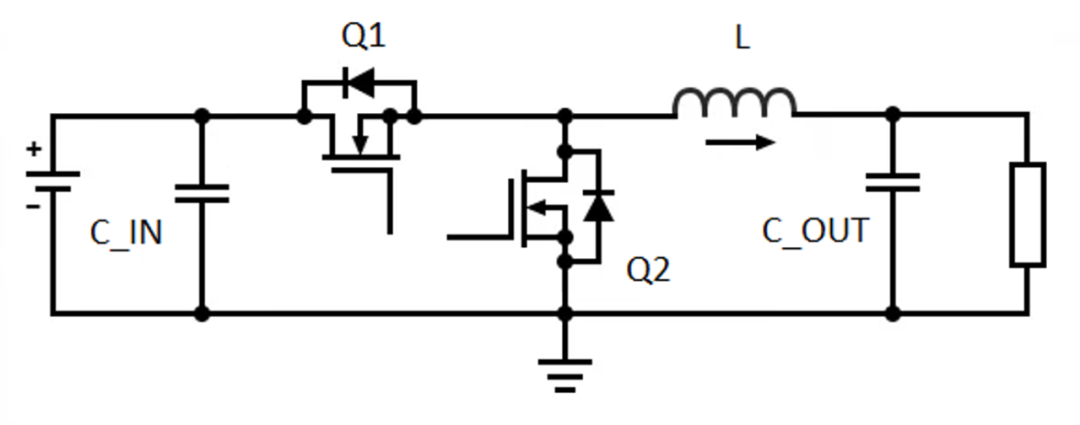

如果将开关稳压电路原理图与这些器件的 PCB 布局进行比较,很容易看出 PCB 布局中可能存在寄生效应。在这些设计中,寄生电容和电感会产生上述噪声问题,但一些简单的设计策略可以帮助抑制这些噪声问题。在接下来的示例中,我们将使用以下降压转换电路来说明这些原理,相同的方法也适用于其他拓扑结构。

标准降压转换器拓扑

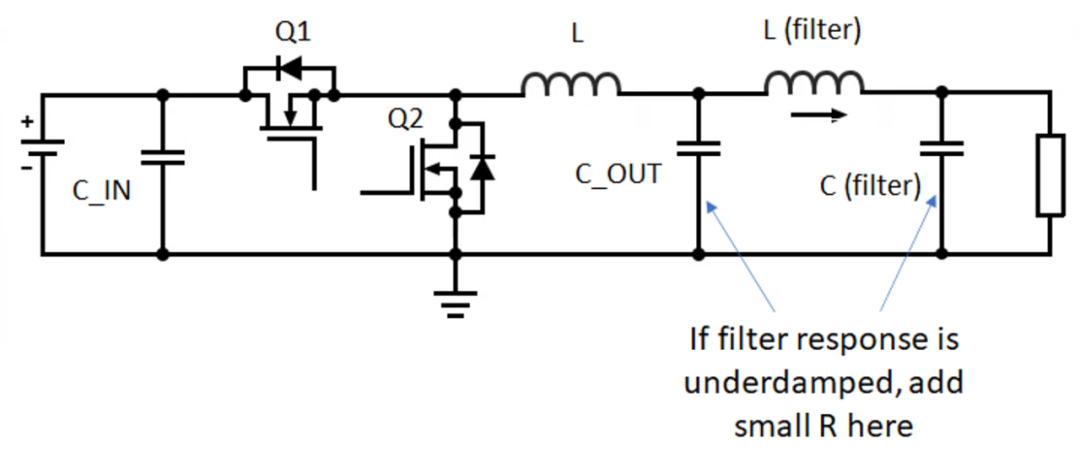

(一)、设计输出滤波器降低开关噪声的一种方法是在输出端放置一个滤波电路。这通常用于输出级联的 LC 电路,如下所示。在本例中,电容器将具有一些有效串联电阻 (ESR),通常远小于 1 Ω。

降压转换器输出滤波器示例。

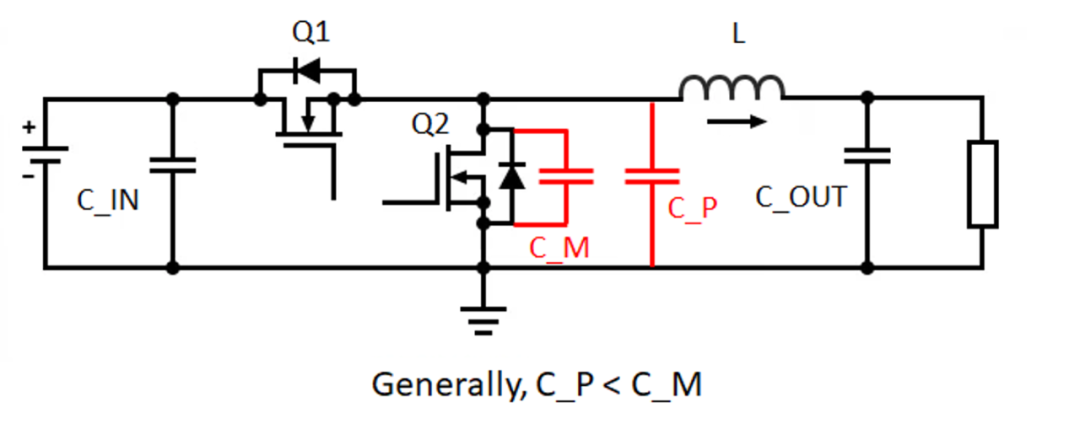

这种设计的挑战是需要确保新的滤波器元件不会为电路的传递函数增加一个额外的极点,这会导致时域中的欠阻尼振荡(振铃)。抑制任何瞬态响应的最简单方法是使用更大的电容器,并在电容器上串联一个小电阻器(仅几 Ω)。这里需要进行一些实验和仿真,以确保没有过多的瞬态振荡,并确保适当地抑制开关噪声。(二)正确设计交换节点准确估计开关节点的电容,以确保电容与高端和低端 MOSFET 电容相比不会太高。作为一般规则,开关节点必须足够大,以流通所需的电流,但又要足够小,以具有低电容。如果开关节点电容太大,则可能需要将其尺寸缩小,以确保电流限制在开关 MOSFET 中,而不是通过寄生电容耦合。

开关负载电容与低端 MOSFET 电容。

值得庆幸的是,与上面示例降压转换器中所示的低端 MOSFET 电容相比,开关节点电容通常非常小。

- 开关节点电容:约 24 pF/sq。mm(假设基板 Dk = 4,厚度 = 0.1 mm,边缘因子为 4)

- l MOSFET DS 电容:大约 1-10 nF

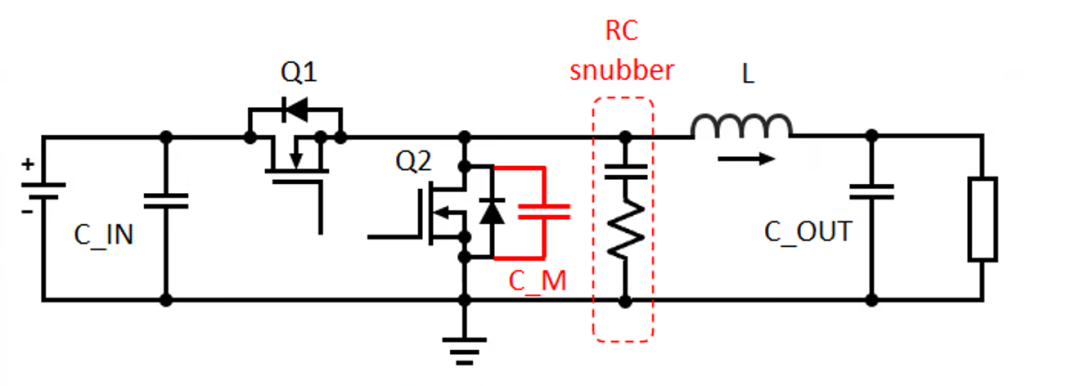

这意味着,对于具有高电容的物理大型 MOSFET,开关节点至少需要 40 平方毫米,以允许噪声绕过低侧 MOSFET 并到达接地网络。因此,我们通常可以忽略开关节点对 GND 的电容。更重要的是与其他电路的互电容,它允许在高 dV/dt 摆幅下进行噪声耦合。使接地更靠近开关节点有助于减少这种互电容。(三)、RC 缓冲器当我们在开关稳压器方面提到 RC 缓冲器时,它被放置在低端 MOSFET 上,如下所示。

RC 缓冲器放置在开关稳压器电路中。

如果 RC 支路具有足够高的阻抗(在 MOSFET 的固有频率下通常为几 Ω),则可以抑制 MOSFET 的开关瞬态响应。此 RC 支路的设计和仿真需要一个精确的 MOSFET 电路模型,其中必须包括寄生效应,以便正确计算和仿真。总结

与往常一样,在实施解决 PCB 布局或电路设计中的寄生问题的解决方案时,请务必仿真您的想法。在这种情况下,所需的仿真包括瞬态分析和频率扫描,以评估附加电路部分将如何作用于您的开关稳压器电路。

总的来说,下面这些 PCB 设计和布局建议可以帮助您抑制电源调节器电路中的噪声:

1. 使地更靠近开关节点

2. 使用更小的交换节点

3. 如果MOSFET振铃太大,请使用 RC 缓冲电路

4. 使用具有临界阻尼响应的输出滤波器来降低开关噪声,而不会产生新的瞬态振铃问题

当您需要设计和仿真您的开关稳压器电路并验证寄生电容的影响时,Cadence的PSpice是业界最佳的电路设计和仿真工具。PSpice 用户可以访问强大的 SPICE 模拟器以及专业设计功能,如模型创建、图形和分析工具等等。

- 相关推荐

- 热点推荐

- 电路

-

开关稳压电源--原理、设计与实用电路2025-06-24 552

-

[分享]高频开关型稳压电源的电磁噪声问题2009-03-11 3582

-

开关稳压电源的设计与应用2016-06-11 11695

-

开关稳压电源和线性稳压电源2018-10-12 2940

-

降压稳压器电路中影响EMI性能和开关损耗的感性和容性寄生元素2020-11-03 2180

-

开关式稳压电路的工作原理2021-11-12 2328

-

线性稳压电源和开关稳压电源的不同2021-11-16 2518

-

开关型稳压电源的原理电路2009-07-25 1592

-

开关稳压电源电路设计及应用2011-11-11 1689

-

开关稳压电路与串联稳压电路分别是什么2018-05-15 18882

-

开关稳压电源的原理、设计与实用电路2021-03-18 1642

-

串联直流稳压稳压电路2021-08-31 1333

-

LM2576开关稳压电源电路设计及应用2021-09-18 2574

-

开关稳压电路和串联稳压电路的区别2023-08-18 2759

-

技术资讯 I 如何识别同步开关噪声2026-02-13 167

全部0条评论

快来发表一下你的评论吧 !