2022 Sigrity SPB 17.4 版本更新 I SystemSI 支持 MIPI-C 仿真与合规检查分析

描述

Allegro 和 Sigrity 软件最新发布了一系列的产品更新(SPB17.4 QIR4 release)。我们将通过实例讲解、视频演示让您深入了解 Allegro PCB Editor、Allegro System Capture、Allegro Package Designer Plus(本期内容)、Sigrity Aurora、Sigrity SystemSI(本期内容)、Sigrity SystemPI 等产品的新功能及用法,助力提升设计质量和设计效率。

Cadence Sigrity SystemSI 的模块化设计允许用户方便地搭建任意拓扑,支持最新的 IBIS/Spice/ TouchStone/IBIS-AMI 模型。

Sigrity SystemSI 可以对高速串行通道进行眼图和误码率分析,对系统中的任意参数进行扫描,得到最优化配置,并且集成了 PCI-E、SATA 等工业标准,直接对仿真结果进行判别。

Sigrity SystemSI 可以对整个 DDR 系统进行准确的 SSN 分析,集成 JEDEC 标准,自动为用户量测 SI 参数,并以此为基础,进行自动化时序分析。

Sigrity SystemSI

系统信号仿真亮点——

1# 支持MIPI-C仿真与合规检查分析

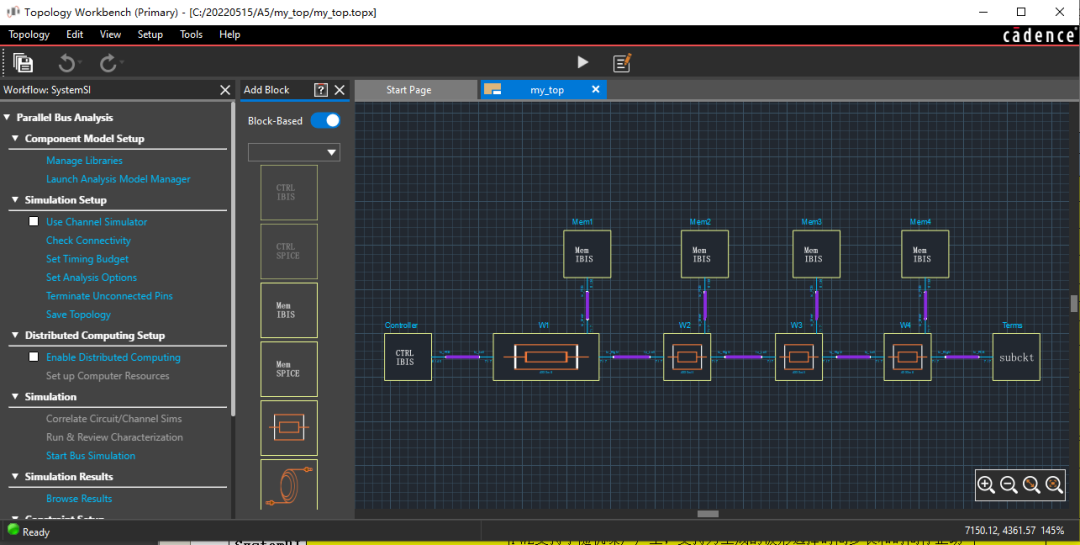

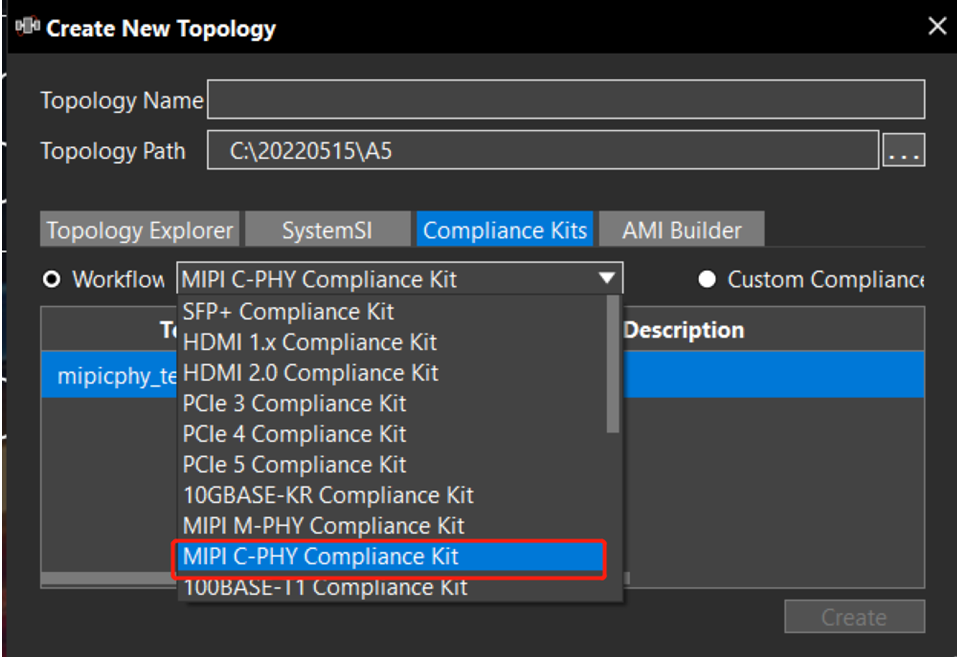

Wbench_SPB17.4_QIR4 更新之后,Sigrity SystemSI 可以支持 MIPI-C 仿真与合规检查分析,支持信号链路拓扑互连及仿真。

1►

实例讲解 · 视频版

建议在WIFI环境下观看,并注意调整音量

2►

实例讲解 · 图文版

1

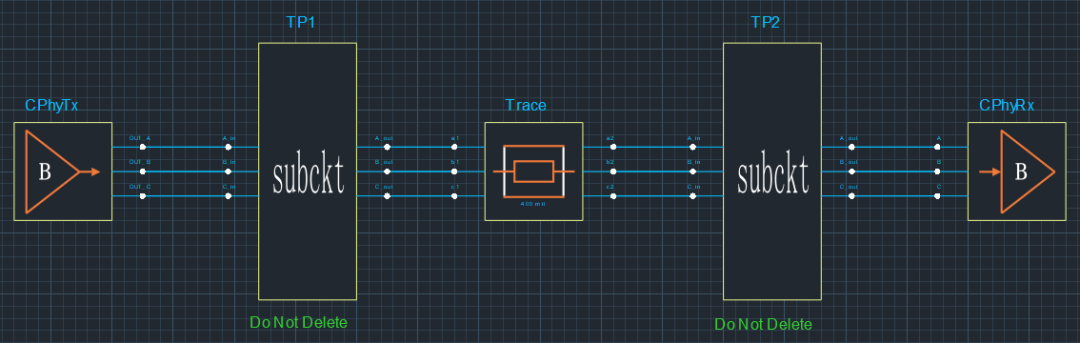

使用 MIPI-C PHY 合规包可以生成 MIPI-C 信号互连模型,CPhyTx 是合规包信号发送端口,CPhyRx 是合规包信号接收端口,TP1、TP2 是合规信号观测点。

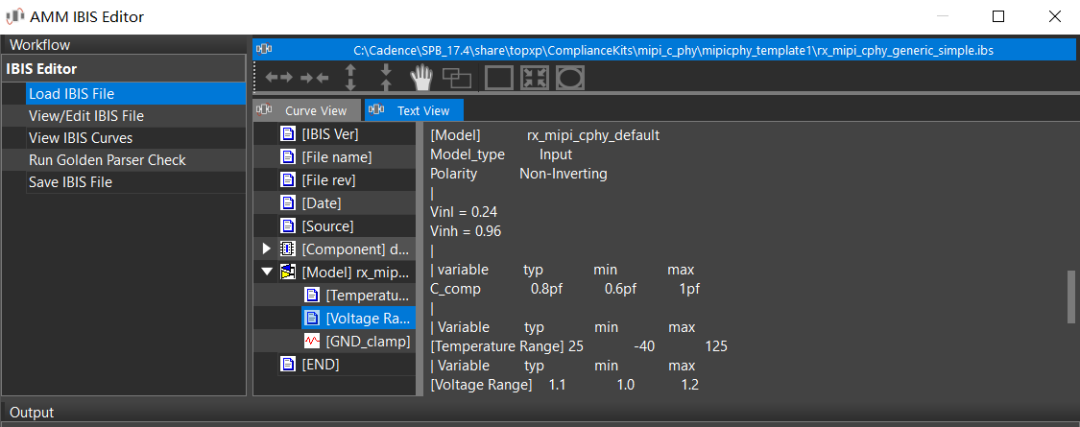

2

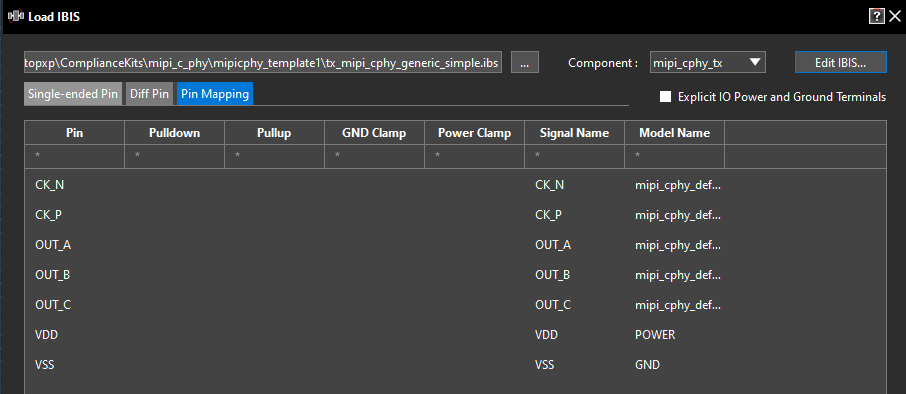

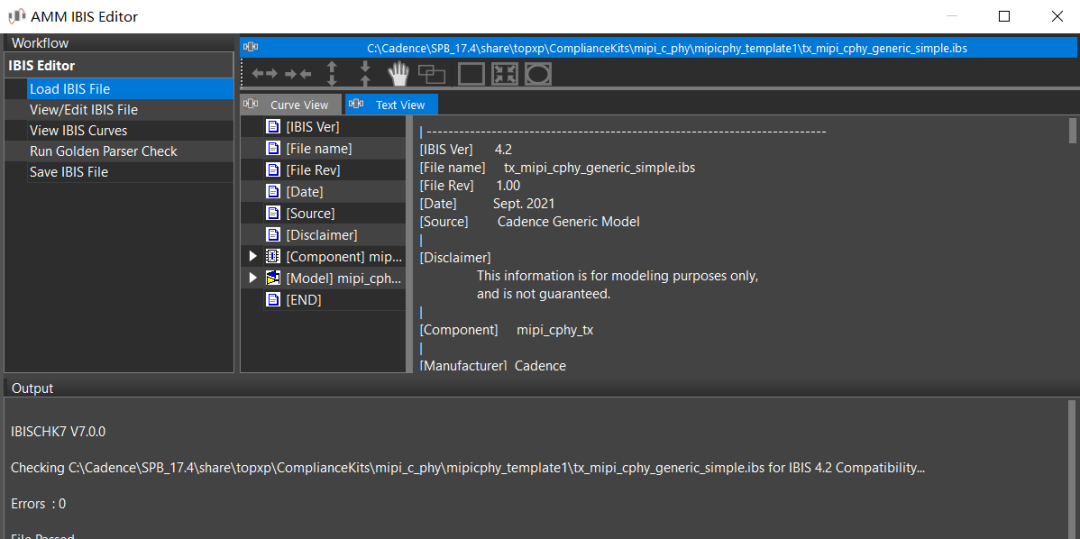

利用框架模板生成的 TX 发送信号 IBIS 模型数据及路径。

3

利用框架模板生成的 TX 发送信号 IBIS 模型数据。

4

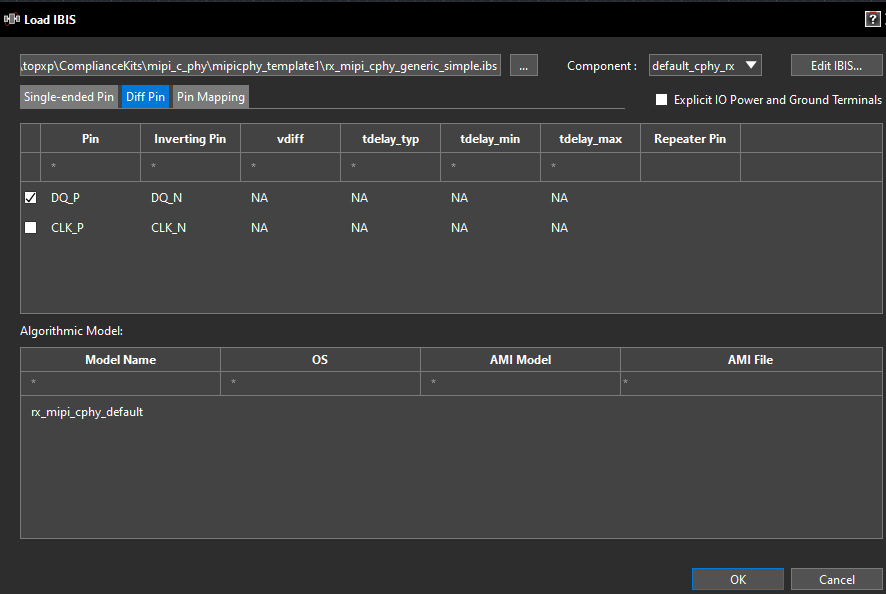

利用框架模板生成的 RX 接收信号 IBIS 模型数据及路径。

5

利用框架模板生成的 RX 接收信号 IBIS 模型数据。

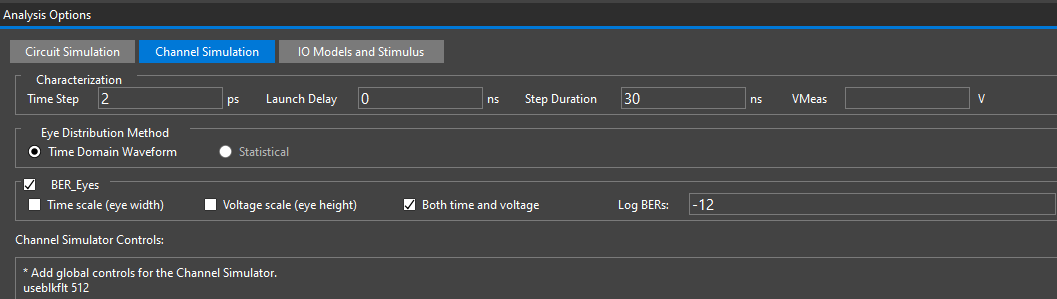

6

MIPI-C信号互连通道仿真参数设置。

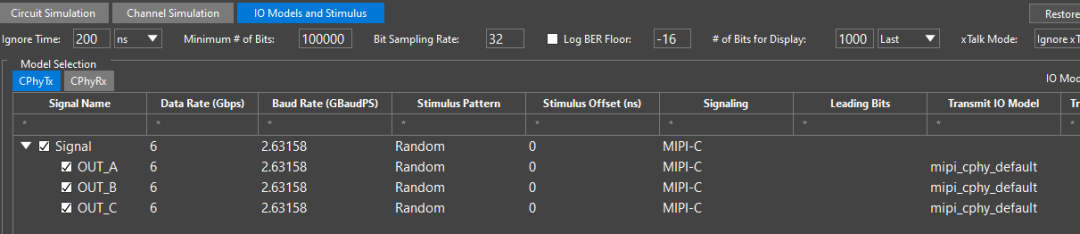

7

MIPI-C 发送模型参数设置及激励数据的设置。

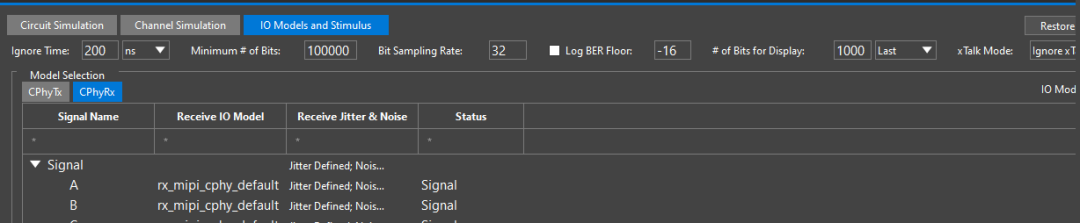

8

MIPI-C 接收模型参数设置及抖动参数设置,激励码数据设置。

9

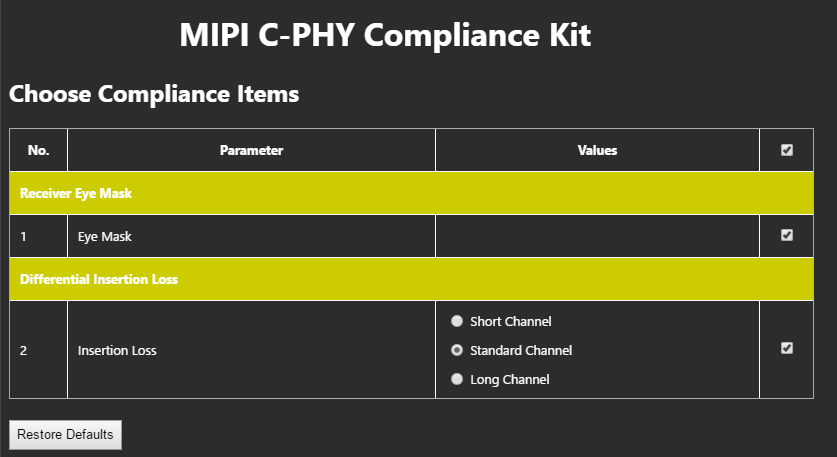

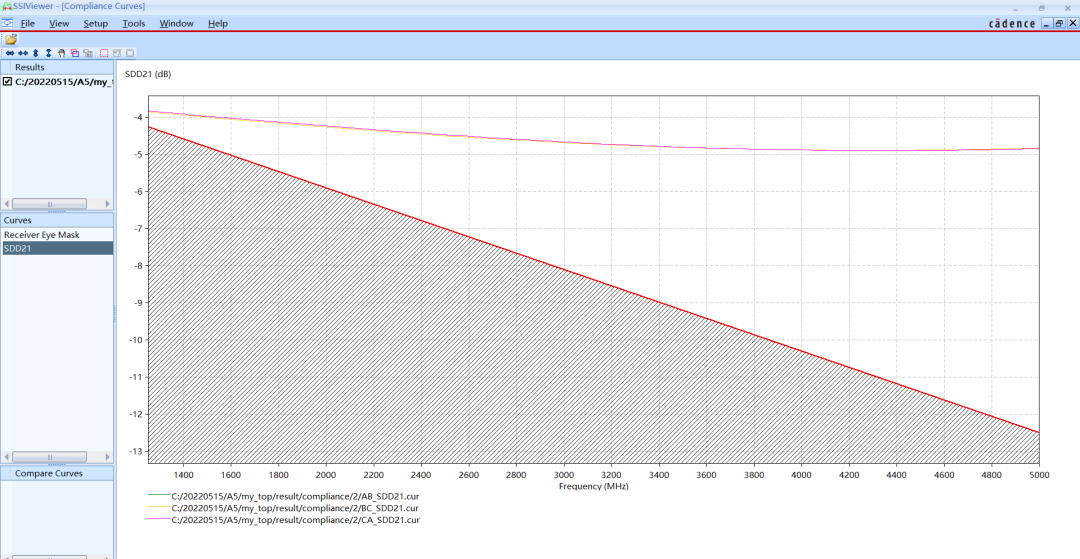

MIPI-C 合规包分析检查项选择,眼图分析和差损数据分析。

10

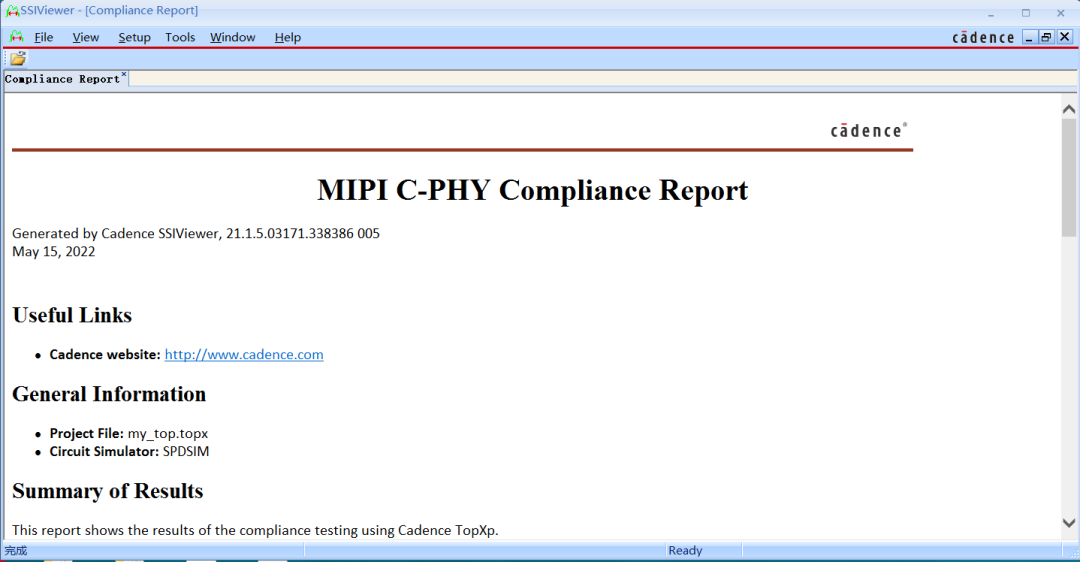

MIPI-C 合规包分析仿真结果。

11

MIPI-C 合规包分析仿真结果。

12

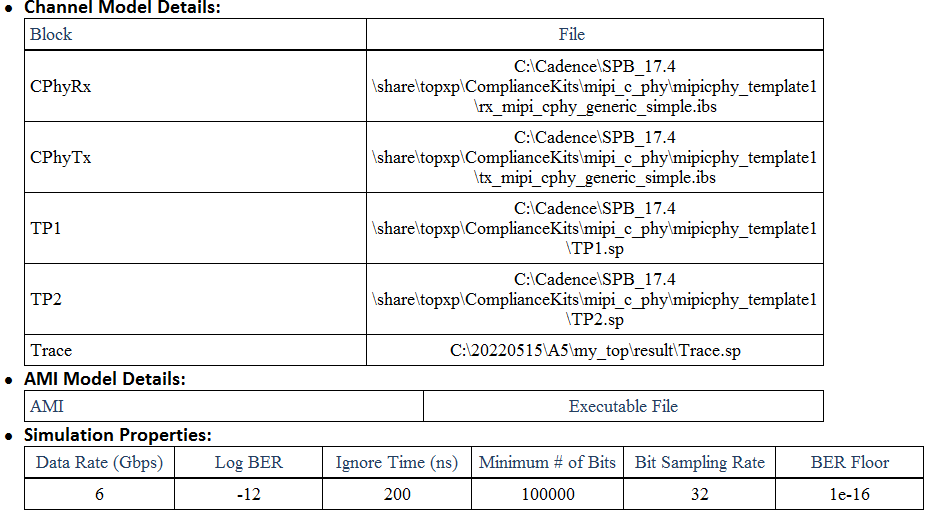

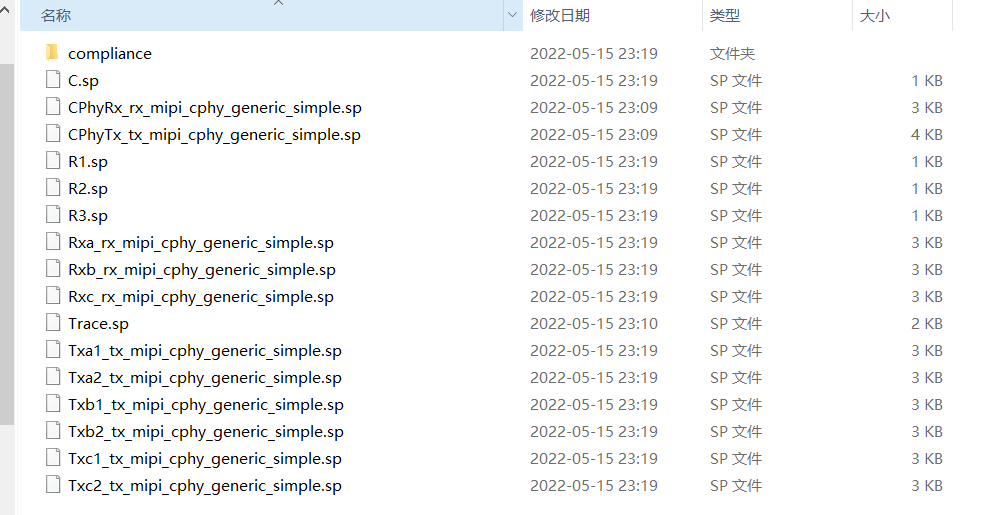

MIPI-C 合规包分析仿真结果,通道的模型数据。

13

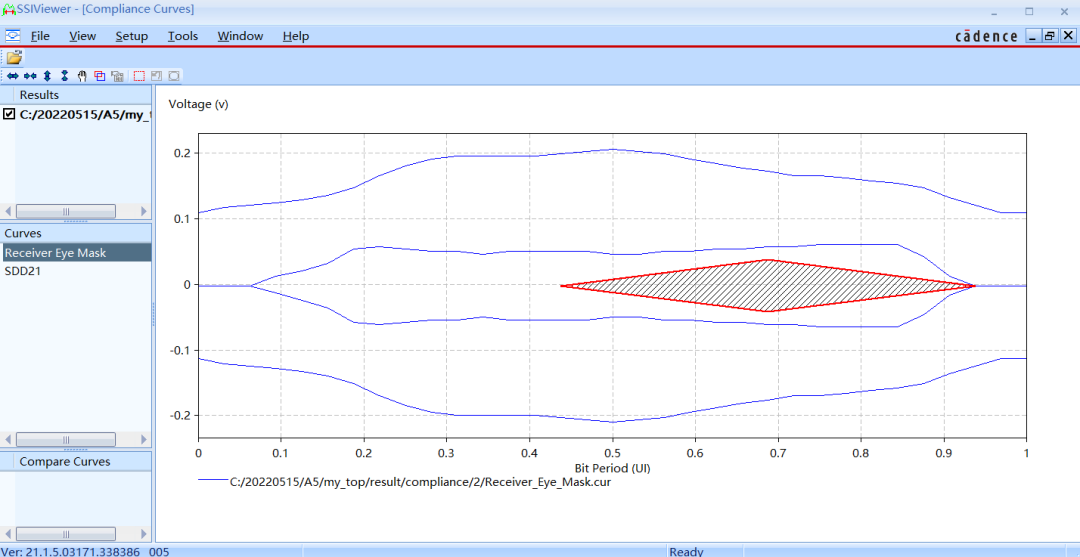

合规包接收眼图信号分析。

14

合规包通道插损结果。

15

MIPI-C 合规检查的结果及波形数据。

- 相关推荐

- 仿真

-

candence 17.4 DRC检查问题2022-09-21 0

-

candence 17.4 DRC检查不了2022-09-21 0

-

电子束炉变压器的故障检查分析2009-12-12 545

-

Cadence SPB 17.4的安装步骤教程详细说明2020-04-10 7571

-

版本更新 | 2022 Allegro SPB 17.4 版本更新——亮点概要2022-06-13 3677

-

Cadence SPB17.4新特性 | OrCAD Capture2022-08-15 1809

-

2022 Sigrity Aurora SPB 17.4 版本更新 I 对未布线网络的拓扑提取及建模2022-08-24 676

-

2022 Sigrity Aurora SPB 17.4 版本更新 I 支持 Clarity 和 PowerSI 引擎直接集成2022-08-28 1391

-

2022 Sigrity Aurora SPB 17.4 版本更新 I IR Drop 直流电压降仿真支持自动剪切功能2022-09-13 1071

-

2022 Sigrity Aurora SPB 17.4 版本更新 I 支持生成同轴电缆和双绞线模型并进行仿真2022-09-19 897

-

2022 Sigrity SPB 17.4 版本更新 I SystemSI 为GDDR6接口增加基于JEDEC自动化分析功能2022-10-09 1585

-

2022 SPB 17.4 版本更新 I Sigrity SystemPI 允许自定义搭建链路进行系统级PDN和电源纹波分析2022-11-17 2155

-

2022 SPB 17.4 版本更新 I SystemPI 允许自定义搭建链路进行系统级电压降仿真分析2022-11-17 631

-

利用Sigrity Aurora进行PCB布线后的仿真分析-阻抗及寄生参数析2024-02-26 1260

全部0条评论

快来发表一下你的评论吧 !