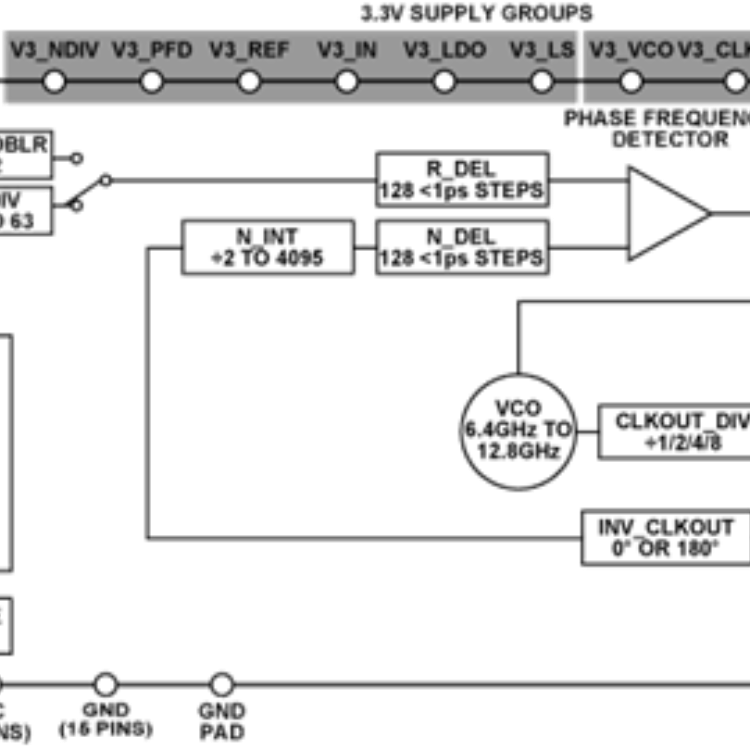

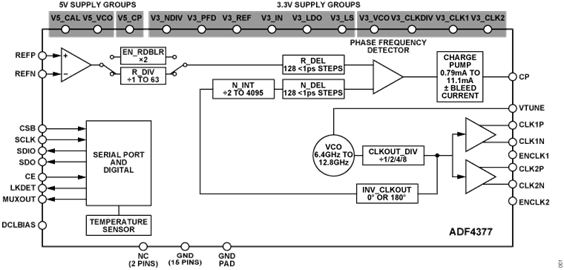

具有集成式压控振荡器 (VCO) 的整数 N 锁相环 (PLL),非常适合数据转换器和混合信号前端 (MxFE) 时钟应用。高性能 PLL 具有 −239 dBc/Hz、超低 1/f 噪声和高相位频率检测器 (PFD) 频率的优点,可实现超低带内噪声和集成的抖动。ADF4377 的基本 VCO 和输出分频器可产生 800 MHz 至 12.8 GHz 的频率。ADF4377 集成了所有必需的电源旁路电容器,可节省紧凑板上的板空间。

对于多个数据转换器和 MxFE 时钟应用,通过对输出同步特性实现自动基准,对过程、电压和温度特性的输出延迟实现匹配的基准,并对输出延迟调整功能特性实现低于 ±0.1 ps 的无抖动基准,ADF4377 简化了其他时钟解决方案所需的时钟对齐和校准程序。

这些特性支持可预测和精确的多芯片时钟和系统基准 (SYSREF) 对齐。通过将 ADF4377 与分配基准和 SYSREF 信号对的集成电路 (IC) 配对,支持 JESD204B 和 JESD204C 子类 1 解决方案。

应用

- 高性能数据转换器和 MxFE 时钟

- 无线基础设施 (MC-GSM, 5G)

- 测试和测量

- 输出频率范围:800 MHz 至 12.8 GHz

- 抖动 = 18 fsRMS(集成带宽:100 Hz 至 100 MHz)

- 抖动 = 27 fsRMS(ADC SNR 方法)

- 宽带本底噪声:12 GHz 时为 −160 dBc/Hz

- PLL 规格

- −239 dBc/Hz:归一化带内相位本底噪声

- −147 dBc/Hz:归一化带内 1/f 噪声

- 鉴相器频率达 500 MHz

-

- 基准输入频率达 1000 MHz

- 典型杂散 fPFD:fOUT = 12 GHz 时为 −95 dBc

- 基准输入到输出延迟规格

- 套件间标准偏差:3 ps

- 温度系数:0.03 ps/°C

- 调整步长:< ±0.1 ps

- 多芯片输出相位对齐

- 3.3 V 和 5 V 电源

- 7 mm × 7 mm 48 引脚 LGA

ADF4377NEW

AD9546

LTC6952

AD9542

AD9543

AD9544

AD9545

AD9576

AD9530

LTC6951

LTC6951-1

AD9531

HMC7044

AD9528

AD9574

AD9578

MAX31180

AD9525

AD9577

AD9523-1

AD9550

AD9523

AD9524

AD9553