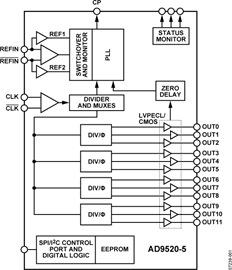

AD9520-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO使用。

AD9520-5串行接口支持SPI和I2C端口。封装内EEPROM能够通过串行接口进行编程,其可存储用于上电和芯片复位的用户定义寄存器设置。

AD9520-5具有12路LVPECL输出,分为四组。任何一路1.6 GHz LVPECL输出都可以重新配置为两路250 MHz CMOS输出。若应用需要LVDS驱动器而非LVPECL驱动器,请参考AD9522-5。每组3路输出具有一个分频器,其分频比(从1至32)和相位失调或粗调时间延迟均可设置。

AD9520-5提供64引脚LFCSP封装,可以采用3.3 V单电源供电。外部VCO的工作电压可高达5.5 V。独立的输出驱动器电源可以为2.375 V至3.465 V。

AD9520-5的额定工作温度范围为−40°C至+85°C标准工业温度范围。

应用

- 低抖动、低相位噪声时钟分配

- SONET、10Ge、10GFC、同步以太网、OTU2/3/4的时钟产生和转换

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

- 宽带基础设施

- 低相位噪声锁相环(PLL)

- 可选外部3.3 V/5 V VCO/VCXO至2.4 GHz

- 1路差分或2路单端基准输入

- 支持最高250 MHz的CMOS、LVDS或LVPECL参考

- 参考输入接受16.62 MHz至33.3 MHz晶振

- 可选参考时钟倍频器

- 参考监控功能

- 自动/手动参考保持和参考切换模式,恢复式切换

- 参考间无毛刺切换

- 从保持模式自动恢复

- 可选数字或模拟锁定检测

- 可选零延迟工作

- 12路1.6 GHz LVPECL输出分为4组

- 每组3路输出,共享一个带相位延迟的1至32分频器

- 加性输出抖动低至225 fs rms

- 分组输出的通道间偏斜 < 16 ps

- 可以将每路LVPECL输出配置为2路CMOS输出(fOUT ≤ 250 MHz)

- 上电时所有输出自动同步

- 提供手动输出同步

- SPI和I2C兼容型串行控制端口

- 64引脚LFCSP

- 非易失性EEPROM存储配置设置

ADF4377NEW

AD9546

LTC6952

AD9542

AD9543

AD9544

AD9545

AD9576

AD9530

LTC6951

LTC6951-1

AD9531

HMC7044

AD9528

AD9574

AD9578

MAX31180

AD9525

AD9577

AD9523-1

AD9550

AD9523

AD9524

AD9553