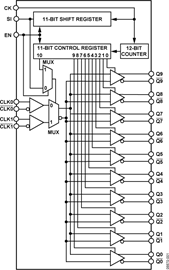

ADN4670是一款低压差分信号(LVDS)时钟驱动器,可以将一路差分时钟输入信号扩展为十路差分时钟输出。这款器件可以通过简单的串行接口进行编程,以便选择两路时钟输入之一(CLK0/CLK0 或CLK1/CLK1) ,以及使能或禁用(三态)任何一路差分输出(Q0/Q0至Q9/Q9) 。ADN4670设计用于50 Ω传输线路环境。

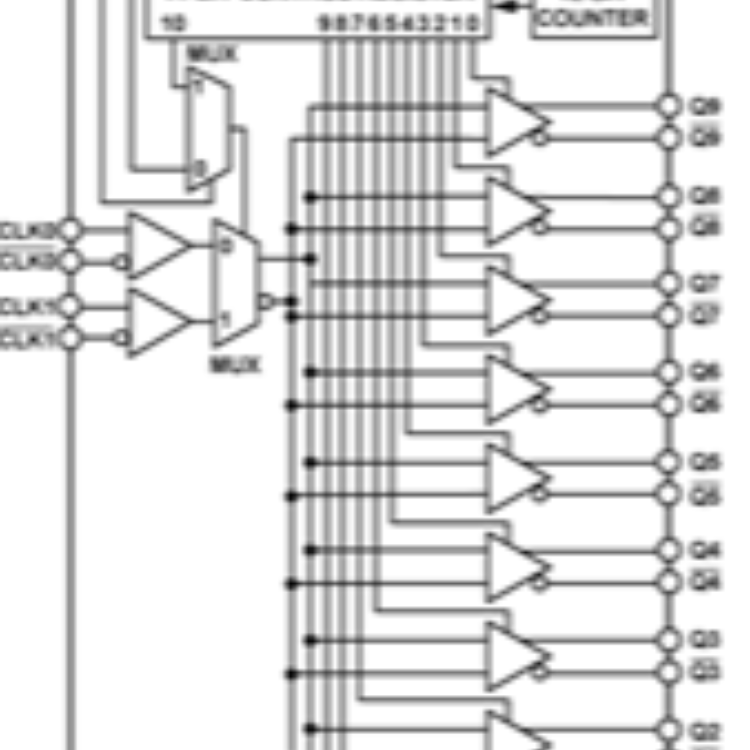

当使能输入EN为高电平时,可以通过将11个数据位输入移位寄存器中来实现对器件的编程。前10位决定哪些输出使能(0 = 禁用,1 = 使能),第11位选择时钟输入(0 = CLK0,1 = CLK1)。第12个时钟脉冲将数据从移位寄存器传输到控制寄存器。

ADN4670的额定温度范围为工业温度范围,提供32引脚LFCSP封装。

应用

- 时钟分配网络

- 低输出偏斜:<30 ps(典型值)

- 从1路差分时钟输入提供10路LVDS时钟输出

- 可编程:可以选择两路差分时钟输入之一(CLK0或CLK1),以及使能或禁用各路差分时钟输出

- 信号速率最高达1.1 GHz(典型值)

- 电源电压范围:2.375 V至2.625 V

- 差分输入阈值:±100 mV

- 轨到轨输入共模范围

- 掉电期间I/O引脚具有故障安全特性: VDD = 0 V

- 提供32引脚LFCSP封装

- 工业温度范围:−40℃至+85℃

ADCLK905

ADCLK907

ADCLK925

AD9513

AD9515

AD9514

MAX3841

MAX9392

MAX9393

MAX9394

MAX9390

MAX9176

MAX9389

MAX9388

MAX9321

MAX9321B

MAX9180

MAX3783

MAX9155

MAX9152

MAX3840