M31 PCIe 2.1 PHY IP

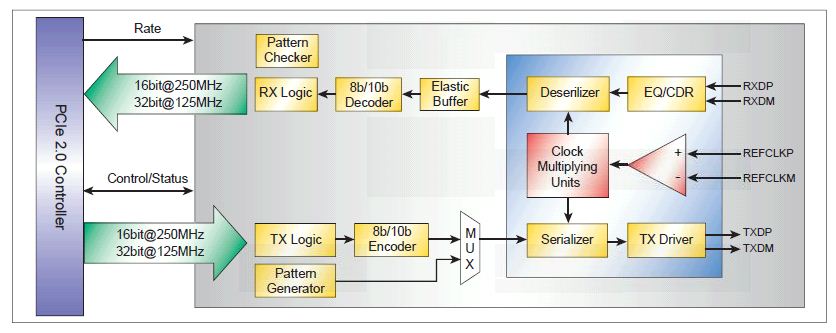

M31 PCIe 2.1收发器IP提供了一系列完整的PCIe 2.1基本应用程序。它符合PIPE 3.0规范。该IP集成了高速混合信号电路,以支持5Gbps的PCIe 2.1流量,并与2.5Gbps的PCIe 1.1数据速率向后兼容。它针对最小的管芯面积和低功耗进行了优化。通过支持TX和RX均衡技术,PCIe 2.1 IP可以满足不同信道条件的要求。

- 增强型电源/面积减少50%

- 完全符合PCI Express Base 2.1和PCI Express Base 1.1电气规范

- 符合PIPE 3.0(PCIe)规范

- 支持PIPE 3.0规范中定义的所有节能模式(P0、P0s、P1、P2)

- 使用CLKREQ支持L1 PM变电站#

- 使用CLKREQ支持L1时钟电源管理(CPM)#

- 支持独立参考SSC(SRIS)体系结构

- 可访问的寄存器控制允许用户特定地优化关键参数(例如,TXPLL带宽、TX去加重级别、CDR带宽和EQ强度)

- 集成高性能PLL,为PCIE相关应用提供各种独立时钟输出

- 支持用于大规模生产测试的强大BIST功能

- 有12nm、14nm、16nm、22nm、28nm、40nm和55nm工艺可选