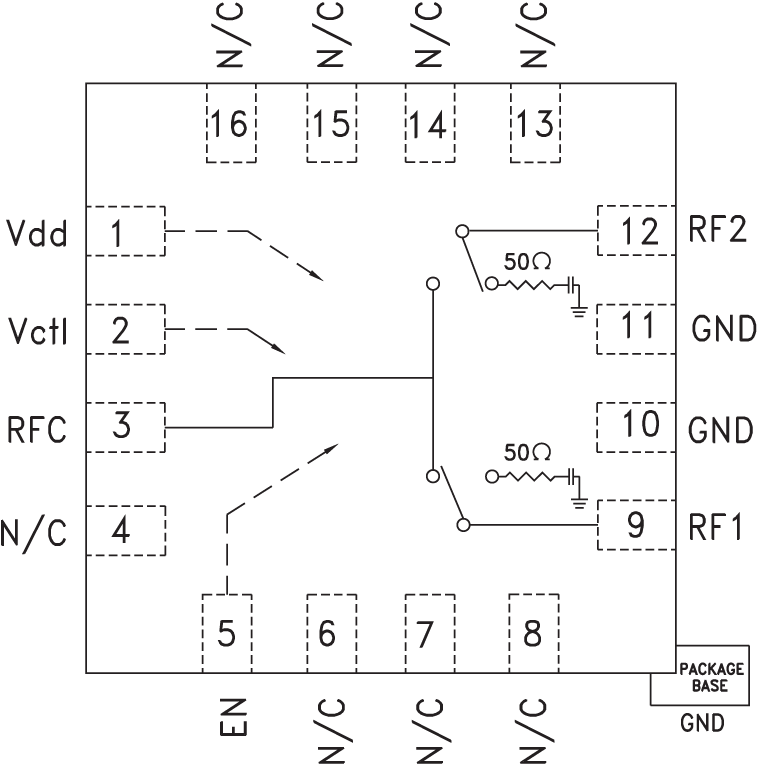

HMC849ALP4CE是一款高隔离非反射DC至6 GHz GaAs pHEMT SPDT开关,采用低成本无引脚表贴封装。 该开关非常适合蜂窝/WiMAX/4G基础设施应用,实现高达60 dB的隔离、0.8 dB的低插入损耗和+52 dBm的输入IP3。 在最高5 - 6 GHz WiMAX频段内,该器件具有很高的功率处理能力,另外提供+31 dBm的P1dB压缩点性能。 片内电路可在极低直流电流下实现0/+3V或0/+5V单正电压控制。 使能输入(EN)设为逻辑高电平可将该开关置于“全关”状态。

HMC849ALP4CE 应用

- 蜂窝/4G基础设施

- WiMAX、WiBro与固定无线

- 汽车远程信息系统

- 移动无线电

- 测试设备

The AD9737A/AD9739A are 11-bit and 14-bit, 2.5 GSPS high performance RF DACs that are capable of synthesizing wideband signals from dc up to 3 GHz. The AD9737A/AD9739A are pin and functionally compatible with the AD9739 with the exception that the AD9737A/AD9739A do not support synchronization or RZ mode, and are specified to operate between 1.6 GSPS and 2.5 GSPS.

By elimination of the synchronization circuitry, some nonideal artifacts such as images and discrete clock spurs remain stationary on the AD9737A/AD9739A between power-up cycles, thus allowing for possible system calibration. AC linearity and noise performance remain the same between the AD9739 and the AD9737A/AD9739A.

The inclusion of on-chip controllers simplifies system integration. A dual-port, source synchronous, LVDS interface simplifies the digital interface with existing FGPA/ASIC technology. On-chip controllers are used to manage external and internal clock domain variations over temperature to ensure reliable data transfer from the host to the DAC core. A serial peripheral interface (SPI) is used for device configuration as well as readback of status registers.

The AD9737A/AD9739A are manufactured on a 0.18 µm CMOS process and operate from 1.8 V and 3.3 V supplies. They are supplied in a 160-ball chip scale ball grid array for reduced package parasitics.

AD9739ABBCZ Product Highlights

Ability to synthesize high quality wideband signals with bandwidths of up to 1.25 GHz in the first or second Nyquist zone.

A proprietary quad-switch DAC architecture provides exceptional ac linearity performance while enabling mixmode operation.

A dual-port, double data rate, LVDS interface supports the maximum conversion rate of 2500 MSPS.

On-chip controllers manage external and internal clock domain skews.

Programmable differential current output with an 8.66 mA to 31.66 mA range.

AD9739ABBCZ Applications

Broadband communications systems

DOCSIS CMTS systems

Military jammers

Instrumentation, automatic test equipment

Radar, avionics