OpenHW

CORE-V(OpenHW Group)CV32E40P 详细解读

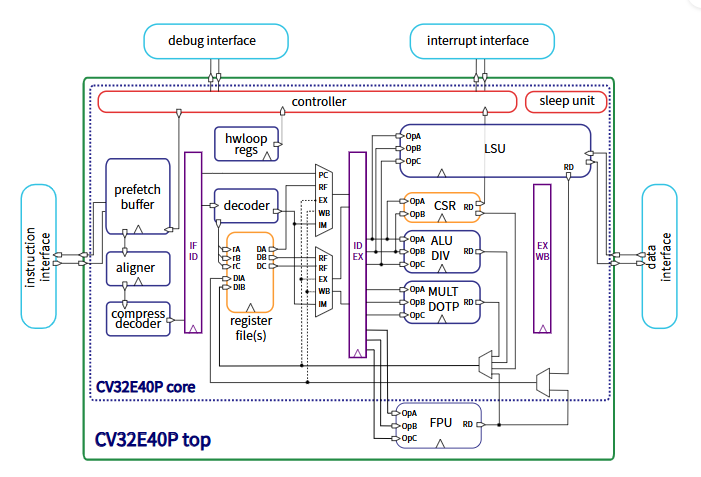

CV32E40P 是 OpenHW Group 推出的开源 RISC-V 处理器 IP 内核,基于 PULP 平台的 RI5CY 内核演进而来,专为高效嵌入式系统设计。以下从技术架构、性能特性

2025-04-10 15:44:33

开源的AI MPU

(2) CORE-V(OpenHW Group) 特点 :开源RISC-V处理器家族,支持AI加速扩展(如DSP/向量指令)。 代表IP :CV32E40P(支持自定义AI协处理器)。 适用场景 :低功

2025-04-02 17:44:40

《RISC-V能否复制Linux 的成功?》

对RISC-V硬件生态系统的参与者进行了调查,包括OpenHW集团、RISC-V International、恩智浦半导体、Andes Technology、英伟达和西部数据,描述了开源软件的相似性、使用的障碍

OPENHW开源CORE-V-MCU移植RT-Thread

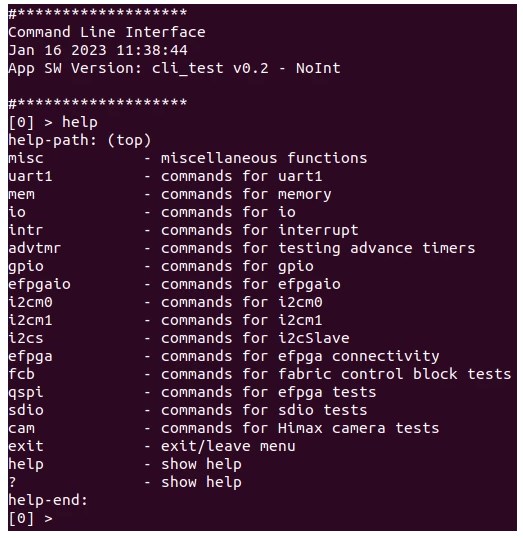

本次实验验证的平台是PLCT提供的QEMU,在Linux下的QEMU可以使用上述的笔者编译好的,也可以使用自己尝试编译PLCT提供的源码。

2023-10-13 14:58:58

OPENHW开源CORE-V-MCU移植RT-Thread的流程

项目背景OpenHW Group 是一个以协作方式开发开源硬件和相关软件的非营利组织,致力于开发、验证和提供开源处理器内核。OpenHW Group的开源项目致力于开发和验证基于免费和开放

OPENHW开源CORE-V-MCU移植RT-Thread

OPENHW提供了基于FreeRTOS的示例工程,由于使用的是PLCT提供的QEMU,所以IDE中自带的工程并不能直接使用,为了避免不必要的麻烦,本文采用PLCT提供的示例工程。

2023-02-01 10:05:43

首席技术官Alessandro Piovaccari近期接受行业媒体的专访时,分享了对于RISC-V发展的观点

和Andes;完全开源的,如OpenHW组织(OpenHW Group)和LowRISC。Silicon Labs是OpenHW组织的创始成员之

详析RISC-V处理器微架构的具体设计

的具体设计。当前,有几种实现方法,商业化的设计,如Si-Five和Andes;完全开源的,如OpenHW组织(OpenHW Group)和LowRISC。Silicon Labs是

2020-06-08 16:48:05

UltraSoC开源RISC-V追踪实现技术,以推动真正的开源开发

UltraSoC将通过与OpenHW集团(OpenHW Group)合作以提供其业界领先的RISC-V追踪编码器的开源项目。

2019-12-11 17:54:20

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览