ARM Cortex-M0+处理器的功能性能如何?

搭载ARM芯片架构的设备数量是英特尔的25倍。全世界99%的智能手机和平板电脑都采用ARM架构。

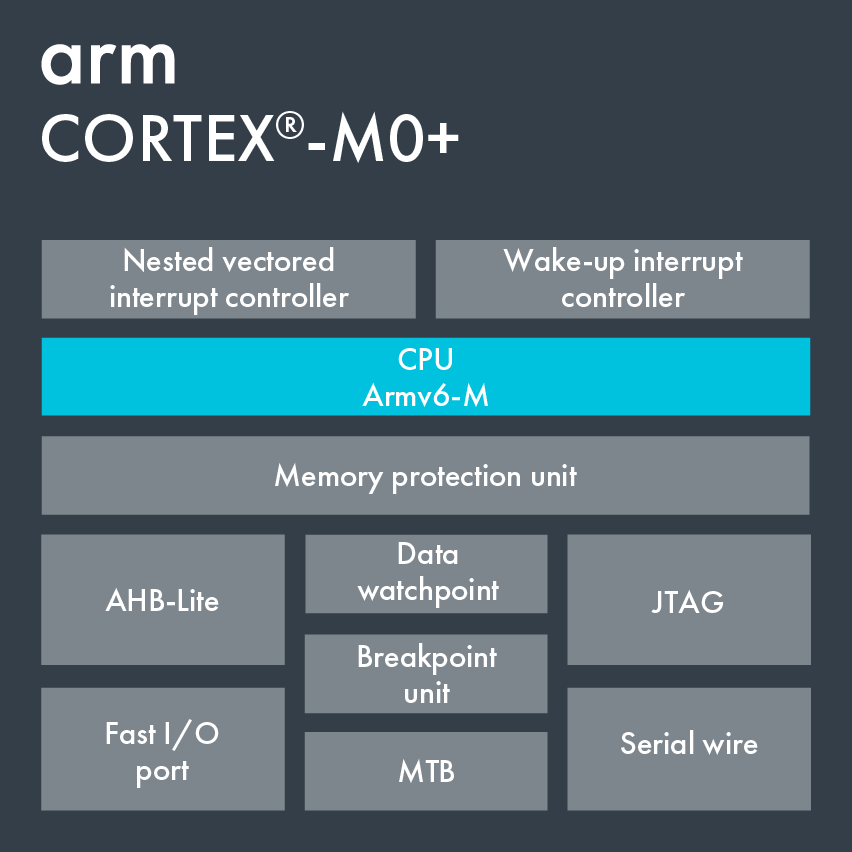

ARM Cortex-M0+ 处理器是一款面向超低功耗和成本敏感型应用的32位微控制器内核,其功能和性能特点可以用以下几个方面概括:

核心定位与设计目标

-

超低功耗 (Ultra-Low Power):

- 核心设计简洁: 采用精简的 ARMv6-M 架构 (Von Neumann),流水线仅有2级,硬件逻辑非常简单。

- 优化的时钟门控: 处理器内部有精细的时钟门控机制,可以关闭不使用的逻辑模块的时钟。

- 极低漏电流设计: 针对漏电流进行了特别优化,在深度睡眠模式下功耗极低(微安甚至纳安级别),非常适合电池供电或能量采集的应用。

- 快速唤醒: 从睡眠模式唤醒所需的时间非常短,有助于降低整体平均功耗。

-

高能效比 (Energy Efficiency):

- 在完成相同任务时,相较于同性能的8位或16位处理器(在相同制造工艺下),Cortex-M0+ 通常能实现更低的功耗和更短的执行时间,即单位能量完成的工作更多。其代码密度也优于8/16位处理器。

- 得益于其32位架构,在处理复杂数据结构、地址计算、状态机控制等任务时效率更高。

-

成本优化 (Cost-Effective):

- 芯片面积小: 逻辑门数在ARM Cortex-M系列中最小(仅约12K门),使得包含它的MCU芯片尺寸很小,晶圆成本低。

- 存储器需求低: 其精简指令集 (Thumb/Thumb-2的子集) 代码密度高,意味着完成同样功能需要的Flash程序存储空间更少,可以选用更小容量、更便宜的Flash。同时所需的最小SRAM也相对较小。

- 低引脚数: 由于其精简特性,MCU可以用更少的引脚封装,进一步降低成本。

功能与特性

-

32位处理能力:

- 提供32位数据路径和地址空间,克服了传统8位/16位处理器在地址空间限制、数据宽度、计算能力和处理效率上的瓶颈。

- 统一的线性4GB地址空间。

-

精简但高效的指令集 (ARMv6-M):

- 继承自Thumb指令集,仅支持56条指令(其中大多数是16位编码,少量是32位)。

- 支持所有通用寄存器和常用操作(算术、逻辑、移位、位操作、分支、访存)。

- 关键增强: 相较于最早的M0,M0+加入了几个关键且实用的新指令(通过少量增加面积实现性能大幅提升):

- 硬件单周期32位x32位乘法器。

- 支持

Unaligned(非对齐) 内存访问: 大大简化编译器工作,提升访存效率。 - 新增多条高效指令: 如

MOVW/MOVT(加载大立即数)、REV/REV16/REVSH(字节序转换)、CPSID I/CPSIE I(快速开关中断) 等。 - 向量表重定位 (VTOR): 灵活配置中断入口地址。

- 没有硬件除法器: 需要软件库实现,除法运算速度较慢。

- 没有硬件浮点单元 (FPU): 需要软件浮点库支持浮点运算。

-

中断处理能力 (NVIC - Nested Vectored Interrupt Controller):

- 集成标准的嵌套向量中断控制器 (NVIC),支持多达32个中断源(具体实现由芯片厂商决定)。

- 支持可编程优先级(通常3-8位)。

- 支持中断嵌套和尾链优化(Tail-chaining),提供高效、低延迟的上下文切换(通常12-16个时钟周期)。

SysTick定时器内核对所有M系列通用。

-

存储接口 (AHB-Lite):

- 主要使用32位的

AHB-Lite系统总线。代码(I-Code/D-Code总线)和系统(System总线)访问分离(但共享同一总线矩阵)。 - 提供

PPB (Private Peripheral Bus)访问内核外设(NVIC, SysTick, Debug等)。 - 无缓存 (Cache)。

- 主要使用32位的

-

调试功能:

- 集成传统的ARM CoreSight调试和跟踪技术。

- 支持SWD (Serial Wire Debug) / JTAG调试接口(通常是SWD,成本更低)。

- 支持有限的软件断点、硬件断点、数据观察点。

- 提供指令跟踪的可选组件

ETM-M0+,但通常被简化或省略以降低成本/功耗。MTB (Micro Trace Buffer)是一种更低成本、小缓冲区的替代方案,用于捕获少量历史指令执行流。

性能指标 (典型范围)

- 时钟频率: 通常在 10 MHz 到 200 MHz 之间。常见MCU中多为 50 MHz - 100 MHz 范围。具体取决于芯片制造工艺(0.18um, 90nm, 55nm, 40nm等)和设计目标(平衡功耗、成本、性能)。

- 效率 (DMIPS/MHz): 约 0.95 DMIPS/MHz。比前代M0 (0.85 DMIPS/MHz) 有提升,但远低于更高性能内核(如M4约1.25-1.4+)。对于执行复杂算法或大量计算,性能是受限的。

- CoreMark/MHz: 约 2.0 - 2.5 CoreMark/MHz。提供一个更贴近实际应用场景的性能参考。

- 中断延迟: 12 - 16个时钟周期(最坏情况)。得益于优化的NVIC和硬件压栈机制,响应速度快。

- 功耗范围:

- 运行功耗: 低至 30-70 µA/MHz(取决于工艺和具体MCU实现)。

- 睡眠功耗: 低至 0.5 - 5 µA(甚至更低到纳安级别),是M0+最突出的优势之一。

总结

ARM Cortex-M0+ 处理器是一款在超低功耗、极低成本和小尺寸方面做到了极致的32位嵌入式处理器内核。其功能精简但高效,针对控制任务、状态机、传感器数据处理、人机交互(简单GUI)、基本通信协议(UART, SPI, I2C)等进行了优化。

最适合的应用场景

- 电池供电的IoT设备(传感器节点、可穿戴设备、智能标签)。

- 成本敏感的消费电子产品(小家电、玩具、遥控器)。

- 需要极致待机功耗的系统(电表、燃气表、烟雾报警器)。

- 作为较大SoC中的系统管理/控制协处理器。

- 替代传统8位/16位MCU以提升性能和开发效率,同时保持相近甚至更低的功耗与成本。

不适用的场景

- 需要处理复杂算法(如DSP/机器学习/图像处理)的任务。

- 需要大量浮点运算的应用(除非有协处理器且能接受软件浮点的低速)。

- 需要极高主频(>100MHz)和计算吞吐量的高性能应用(此时应考虑Cortex-M3/M4/M7/M33/M55等)。

总之,Cortex-M0+的核心价值在于其无与伦比的功耗效率和单位成本下的32位性能。 如果你需要一款针对低功耗和成本进行了极致优化的“基础款”32位MCU内核,它就是绝佳的选择。其庞大的生态系统和工具支持也大大降低了开发门槛。

基于Arm Cortex-M0+的MCU上的ADC增益误差和失调误差校准

电子发烧友网站提供《基于Arm Cortex-M0+的MCU上的ADC增益误差和失调误差校准.pdf》资料免费下载

资料下载

![]() 佚名

2023-09-25 10:08:47

佚名

2023-09-25 10:08:47

慕课嵌入式开发及应用(第三章.ARM Cortex-M0+内核定时器 (Systic)

慕课苏州大学.嵌入式开发及应用.第三章.基本模块.ARM Cortex-M0+内核定时器 (Systic

资料下载

![]() 佚名

2021-11-03 14:51:02

佚名

2021-11-03 14:51:02

慕课嵌入式开发及应用(第二章.ARM Cortex-M0+中断机制和中断编程步骤)

慕课苏州大学.嵌入式开发及应用.第二章.入门与软件框架.ARM Cortex-M0+中断机制和中断编程步骤0 目录2 入门与软件框架2.7

资料下载

![]() 佚名

2021-11-03 13:51:01

佚名

2021-11-03 13:51:01

ADSP-CM41x混合信号控制处理器,带ARM Cortex-M4/ARM Cortex-M0和16位ADC硬件参考

ADSP-CM41x混合信号控制处理器,带ARM Cortex-M4/ARM

资料下载

![]() 385288

2021-05-09 10:45:55

385288

2021-05-09 10:45:55

介绍易于使用的Arm Cortex-M处理器上的信号处理功能

耳机,智能扬声器和摄像头。我们看到这样的自主,智能和连接设备的惊人增长,而挑战在于它们必须在低功耗环境中运行。为了实现信号处理功能,这些应用程序

ARM Cortex-M0+中断机制和中断编程步骤

慕课苏州大学.嵌入式开发及应用.第二章.入门与软件框架.ARM Cortex-M0+中断机制和中断编程步骤0 目录2 入门与软件框架2.7

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 芯片的工作原理是什么?

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- dtmb信号覆盖城市查询

- 怎样挑选路由器?

- 华为芯片为什么受制于美国?

- 元宇宙概念股龙头一览

- type-c四根线接法图解

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- BLDC电机技术分析

- 复位电路的原理及作用

- dsp是什么意思?有什么作用?

- iphone13promax电池容量是多少毫安

- 苹果无线充电器怎么使用?

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 传感器常见类型有哪些?

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机