cadence lvs 错误

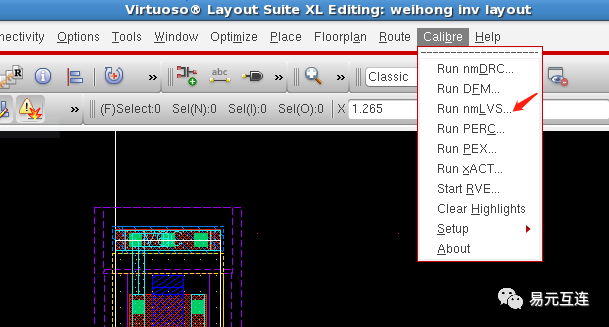

Cadence 工具(如 Virtuoso)在进行 LVS(Layout vs. Schematic)验证时遇到的错误,通常表示芯片物理版图(Layout)与电路原理图(Schematic)之间存在不一致。请提供具体的错误信息或错误代码,以便更精确地诊断问题。

不过,我可以先列出一些最常见的 LVS 错误类型及其一般解决方法(中文版):

1. 连接性错误(Connectivity Errors)

* **开路(Open/Open Net):**

* **现象:** 原理图中连接的两个点,在版图中没有用金属线真正连接起来(物理断开)。

* **原因:** 走线没画完、接触孔(Contact/Via)缺失或未对准、端口(Pin/Port/Label)缺失或位置/层次错误、层级连接关系(Global Net)定义错误。

* **解决:** 在版图编辑器中找到报告开路的网络(Net),检查路径上的所有线段、接触孔和端口是否完整、正确连接且标签无误。确保顶层端口与原理图匹配。

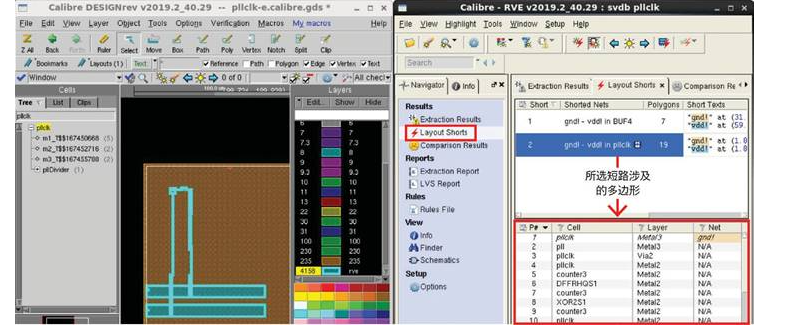

* **短路(Short/Shorted Net):**

* **现象:** 原理图中不该连接的两个或更多网络,在版图中意外地通过金属层或多晶硅等导体连接在一起了。

* **原因:** 金属线间距过小导致设计规则外的连接、不同网络的金属重叠、隔离(Nwell/Pwell/STI)不当、端口命名错误(不同网络用了相同端口名)。

* **解决:** 定位报告短路的网络和位置,仔细检查该区域是否有非预期的金属/多晶硅重叠或间距违规。检查端口标签是否正确且唯一。使用LVS工具提供的短路标记(Marker)功能精确定位。? 2. 器件错误(Device Errors)

* **器件缺失(Missing Instance):**

* **现象:** 原理图中存在的器件(如MOS管、电阻、电容等),在版图中找不到对应的物理结构。

* **原因:** 版图里确实漏画了这个器件、器件层次(Layer)错误导致LVS无法识别、层次属性(如电阻层、电容层)未正确定义、器件的端口连接错误使其不被识别为有效器件。

* **解决:** 核对原理图和版图器件列表,确认缺失的器件。找到它在版图上应有的位置,检查其图形层次、端口连接是否正确。确保LVS规则文件能识别该器件的层次组合。

* **器件多余(Extra Instance):**

* **现象:** 版图中存在物理结构(通常是无意中留下的图形),被LVS识别为一个器件,但原理图中没有对应的器件。

* **原因:** 绘图残留(比如画了器件形状但忘记删除)、层次组合意外形成了有效的器件结构(例如,多晶硅穿过有源区且两端有接触孔,无意中形成了一个MOS管)。

* **解决:** 查看报告的多余器件位置和类型,检查该区域的物理图形。如果是残留图形,删除它。如果是意外形成的器件,需要修改版图布局(如增加间距、断开路径)避免形成有效器件结构。

* **器件参数不匹配(Property Mismatch - e.g., Width, Length, Multiplier, Value):**

* **现象:** 版图器件和原理图器件类型匹配,但关键参数(如MOS管的W/L、电阻值、电容值、BJT的尺寸、二极管的面积/周长等)不一致。

* **原因:** 版图器件尺寸画错、原理图参数更新后版图未同步修改、LVS规则文件中器件参数的提取方式(如电阻长度宽度定义、电容面积周长计算)与预期不符、层属性(如电阻层、注入层)使用错误导致参数提取偏差。

* **解决:** 仔细核对原理图参数和版图器件的实际物理尺寸(用测量工具)。确保版图按照原理图要求绘制。检查LVS规则文件中的器件识别和参数提取语句是否合理(有时需要微调规则文件)。确认特殊器件(电阻、电容)使用的层次正确无误。3. 端口/引脚/标签错误(Pin/Port/Label Errors)

* **端口缺失(Missing Port):**

* **现象:** 原理图中定义的输入/输出端口,在版图顶层找不到对应的物理端口(Pin/Label)。

* **原因:** 版图顶层忘记放置端口标签、标签所在图层错误、标签名称拼写错误、标签位置未放在实际的金属线上。

* **解决:** 在版图顶层检查所有端口是否都存在且名称正确(区分大小写!)。确保端口标签放在正确的识别层(通常是顶层金属的Pin层或Text层),且物理位置覆盖了相应的金属线。

* **端口不匹配(Port Mismatch):**

* **现象:** 版图端口和原理图端口的名称不一致或数量不一致。

* **原因:** 端口名输入错误、原理图端口增减后版图未更新、多放了或少放了端口标签。

* **解决:** 仔细比对原理图端口列表和版图端口列表(名称和数量)。确保完全一致并且拼写/大小写匹配。

* **端口未连接(Unattached Port):**

* **现象:** 版图中的端口标签没有连接到任何实际的金属网络。

* **原因:** 端口标签悬空(下面没有金属线)、标签放错了层次(放在了非连通的层次上)。

* **解决:** 移动端口标签,确保它放置在正确金属层的实际连线上。? 4. 层次结构/模块错误(Hierarchy Errors)

* **子单元不匹配(Cell Mismatch):**

* **现象:** 顶层调用的子模块(Cell Instance),在版图和原理图中对应的底层单元(Master Cell)不一致或不兼容。

* **原因:** 版图底层单元画错或未完成、原理图底层单元修改后版图未更新(或反之)、版图底层单元LVS本身未通过、底层单元接口(端口)定义不一致。

* **解决:** 单独对报告不匹配的底层单元运行LVS,确保底层单元自身通过。检查顶层调用时该实例对应的底层单元名是否正确。确保底层单元的端口(Pin)名称、数量和位置在版图和原理图中完全一致。

* **全局信号问题(Global Net Issues):**

* **现象:** 全局信号(如VDD, VSS, CLK)在层次结构中连接不一致或识别错误。

* **原因:** LVS规则文件中全局信号名称定义(`GLOBAL`语句)与原理图/版图中的实际名称不符、版图中全局网络的标签或连接缺失、层级间全局信号连接断开。

* **解决:** 检查LVS规则文件中的`GLOBAL`定义是否包含了所有必要的全局网络名且拼写一致。检查版图中所有相关层次上的全局网络是否都有正确的标签(有时需要反复标)和完整连接。5. 规则文件或设置错误(Rule Deck/Setup Issues)

* **LVS规则文件错误/不匹配:**

* **原因:** 使用的规则文件与工艺不兼容、规则文件本身有语法错误、规则文件中器件识别层定义或参数提取方式与实际版图不符。

* **解决:** 确认使用的是针对当前工艺的正确且完整的LVS规则文件(`.calibre`或`.svs`等)。有时需要与工艺厂提供的文档核对或请求支持。检查规则文件是否有明显语法错误(LVS工具通常会报规则文件错)。

* **LVS运行设置错误:**

* **原因:** 运行LVS时指定的原理图源(如CellView)、顶层单元名、库路径、开关选项(如忽略某些属性)设置不正确。

* **解决:** 仔细核对LVS运行设置对话框中的所有选项,确保原理图源、顶单元名、库路径、层次分隔符等设置准确无误。确认勾选了正确的选项(如提取寄生?忽略电阻值?等)。? 通用排错步骤(强烈建议)

- 仔细阅读错误报告: 这是最重要的一步!LVS工具(如Calibre)生成的报告文件(

.lvs.report或.svs.log)通常会详细列出每一个错误,包括错误类型、涉及的网名(Net)、器件名(Instance)、单元名(Cell)、端口名(Pin)以及在版图中的物理坐标(X, Y)。重点关注错误描述和坐标位置。 - 利用可视化调试工具:

- Calibre RVE(Results Viewing Environment): 这是最强大的工具。在RVE中双击错误条目,它会自动在版图(Virtuoso)和原理图(Composer/Schematic)中高亮显示不一致的点,直观地定位问题所在。强烈依赖此功能!

- 版图高亮(Highlighting): 在Virtuoso版图中,根据报告中的网名或坐标,手动高亮(

H键)相关网络或器件,检查其连接性和形状。

- 逐层检查(Divide and Conquer): 对于复杂设计,先注释掉(Comment Out)大部分电路或模块,只保留一个非常小的、已知正确的子模块运行LVS。通过后再逐步取消注释,添加更多部分,直到找到引入错误的模块。对不匹配的子单元单独运行LVS。

- 检查基本要素:

- 端口(Pins/Labels): 顶层和关键子模块的端口是否齐全?名称是否正确(大小写敏感!)?是否放置在正确的金属层和物理位置上?是否真的连接到了线上?

- 连接(Connections): 在报告问题网络的坐标附近,放大仔细检查所有金属线、接触孔(Contact/Via)的连接是否有断开或短路?是否有多余的图形?

- 器件: 检查尺寸(W/L/S等)、层组合是否正确?参数是否匹配(MOSFET, R, C, D等)?是否遗漏或多余?特别检查电阻、电容等特殊器件的识别层。

- DRC先行: 确保版图已经通过了DRC(设计规则检查)! 很多LVS错误(尤其是短路、开路)是由违反DRC引起的(如间距太小导致短路)。

- 核对规则文件和设置: 确认使用的是最新、正确的工艺LVS规则文件。检查LVS运行设置(顶层单元名、库路径、选项开关等)。

- 寻求帮助: 查看工艺厂提供的设计手册或LVS规则说明文档。如果是常见问题或规则文件问题,同事、论坛(如EETOP)或Cadence支持可能有经验。

? 请务必提供具体的错误信息!

举例说明你需要提供的信息:

“错误报告显示:

INCORRECT NET 错误。网络 VSS 在原理图里有 15 个连接点,但在版图中只有 14 个。”“Calibre 报错:

DEVICE PROPERTY MISMATCH。实例 I123/M1 (NMOS): 原理图 W=2u, 版图提取 W=200n。坐标 (125.4, 78.9)。”“LVS 显示顶层端口

CLK_IN在版图上找不到。”“报告说子模块

ADC_DIGITAL的版图和原理图不匹配。”

有了具体的错误描述和代码(如果有),才能给出更精准的解决方案! 请尝试在你的LVS日志或报告中找到关键的错误信息片段贴上来。

希望这份中文指南能帮你定位问题!坚持检查,LVS通过是迟早的事!??

常见的lvs负载均衡算法

常见的lvs负载均衡算法包括轮询(RR)、加权轮询(WRR)、最小连接(LC)、加权最小连接(WLC)、基于局部性的最少链接(LBLC)、带复制的LBLC(LBLCR)、目标地址散列(DH)、源地址

2024-12-12 13:50:18

基于LVS+Keepalived实现高可用负载均衡

LVS 是一种预装在 Linux 系统中,基于四层、具有强大性能的反向代理服务器。ipvsadm 是 LVS 的命令行管理工具。

2024-04-09 12:30:51

Cadence Virtuoso设计的一个反相器LVS验证案例

一个版图设计好以后,产生的错误可能是多连了一根铝线造成的Short,或者是少连了几根铝线造成的Open,这样的低级错误对芯片来说都是致命的,因此编辑好的版图要通过

2023-10-02 15:08:00

基于Cadence软件DRACULA工具的LVS检查

基于Cadence软件DRACULA工具的LVS检查(村田电源技术(上海)有限公司深圳分公司)-基于Cadence软件DRACULA工具的

资料下载

![]() 佚名

2021-09-18 17:40:54

佚名

2021-09-18 17:40:54

Cadence的详细资料简介

本章将从Cadence的功能特点及发展历史讲起,介绍Cadence SPB 16.6的安装、界面、使用环境,以使读者能对该软件有一个大致的了解。

资料下载

![]() ah此生不换

2019-06-21 15:31:31

ah此生不换

2019-06-21 15:31:31

探讨一下std-cell在LVS的特殊处理

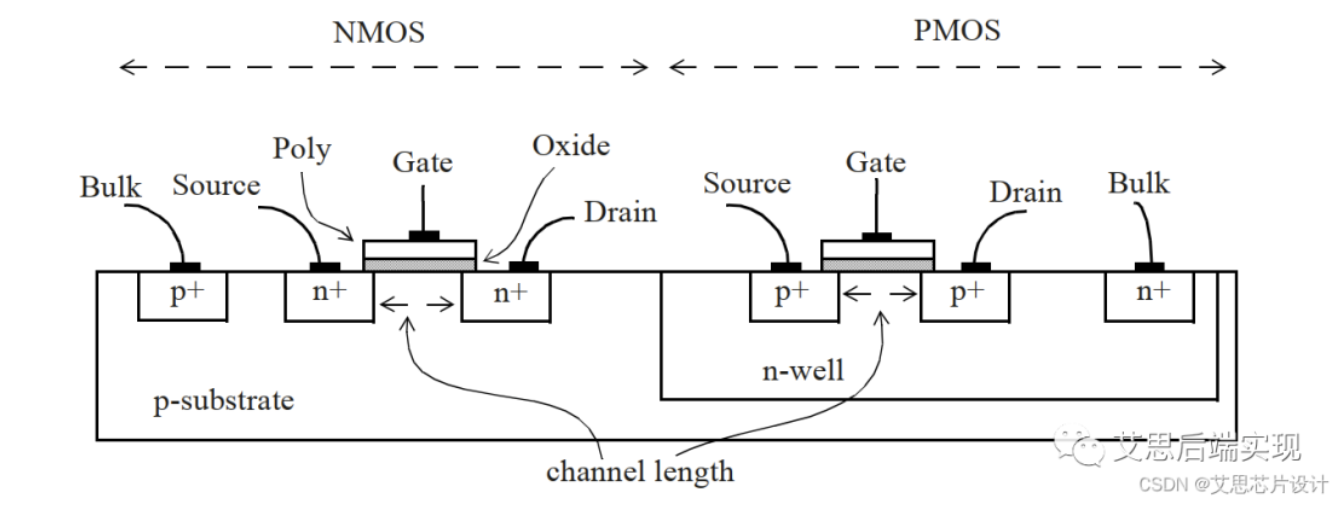

对于物理验证中的LVS,需要对各种物理器件进行SpiceVsGDS的比对,基于现在流行的std-cell的库的设计方法,LVS需要对CMOS器件多相应的处理

2023-06-27 09:27:17

物理验证LVS对bulk(体)的理解和处理技巧

对于物理验证中的LVS,需要对各种物理器件进行SpiceVsGDS的比对,基于现在流行的std-cell的库的设计方法,LVS需要对CMOS器件多相应的处理

2023-06-14 14:41:46

DS75LVS+T&R DS75LVS+T&R - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

电子发烧友网为你提供()DS75LVS+T&R相关产品参数、数据手册,更有DS75LVS+T&R的引脚图、接线图、封装手册、中文资料、英文资料,DS75

DS75LVS+ DS75LVS+ - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

电子发烧友网为你提供()DS75LVS+相关产品参数、数据手册,更有DS75LVS+的引脚图、接线图、封装手册、中文资料、英文资料,DS75LVS

实现有效且高效的LVS调试案例解析

简介 版图与电路图比较 (LVS) 验证是片上系统 (SOC) 设计周期中集成电路 (IC) 验证必不可少的组 成部分,但鉴于当今高密度且层次化的版图、不断提高的电路复杂性以及错综复杂的晶圆 代工厂

2021-01-30 10:58:00

cadence导入网表时出现错误

cadence导入网表时出现这样的错误,我的padpath,parampath,psmpath的路径都设置正确,但是我没有原理图,只有网表。

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机