vivado 和ise

好的,我们用中文来解释 Xilinx(现属于 AMD)的这两个重要 FPGA 开发工具:Vivado 和 ISE (ISE Design Suite)。

简单来说:

- ISE (Integrated Software Environment) 是较旧一代的 FPGA 设计工具套件。

- Vivado Design Suite 是新一代、当前主流的 FPGA 和 SoC(如 Zynq)设计工具套件。

以下是它们的主要区别和特点:

-

目标器件/年代:

- ISE: 主要用于 Xilinx 7系列之前的 FPGA 器件,例如:

- Spartan® 系列:Spartan-3, Spartan-3E, Spartan-3A, Spartan-6 等。

- Virtex® 系列:Virtex-4, Virtex-5, Virtex-6 等。

- CoolRunner™ II CPLD。

- 注意:ISE 官方支持已于2013年左右结束,不再更新,但对于维护旧项目或使用上述老器件仍然必要。

- Vivado: 专门为 7系列及以后的 Xilinx FPGA、SoC 和 ACAP 设计,例如:

- Artix®-7, Kintex®-7, Virtex®-7 (统称 7系列)。

- UltraScale™, UltraScale+™ (16nm/20nm)。

- Versal™ ACAP (Adaptive Compute Acceleration Platform)。

- Zynq®-7000 SoC, Zynq UltraScale+™ MPSoC。

- Vivado 是 Xilinx (AMD) 当前和未来的主力开发平台,持续更新和增强。

- ISE: 主要用于 Xilinx 7系列之前的 FPGA 器件,例如:

-

开发流程与架构:

- ISE: 基于传统工具链拼接,流程相对分散。核心综合工具是 XST (Xilinx Synthesis Technology)。用户界面 (Project Navigator/GUI) 和底层引擎的结合不如 Vivado 紧密。

- Vivado: 革命性的新一代架构。从头设计,核心是高度集成的、基于 IP 和系统为中心的设计流程。

- Vivado IP Integrator (IPI): 强大的图形化 IP 集成环境,方便构建复杂系统(尤其是包含处理器的 SoC 设计)。

- 统一的设计数据库: 整个设计过程(综合、实现、布线、分析)共享一个统一的数据库,大大提高了工具交互效率和设计迭代速度。

- Vivado Synthesis: 取代了 XST,提供更强大的综合能力。

- 智能设计流程: 内置更多自动化分析和优化策略。

-

用户界面:

- ISE: 主界面是 Project Navigator,功能相对基础。Tcl 脚本支持虽然存在,但 GUI 是其主要交互方式。

- Vivado: 现代、功能更丰富、更强大的图形用户界面 (GUI)。深度集成了 Tcl 控制台,GUI 上的几乎所有操作都对应 Tcl 命令,支持高度自动化和脚本化设计流程。界面设计更符合现代软件的使用习惯。

-

综合与实现引擎:

- ISE: 使用 XST 进行综合。布局布线引擎针对老架构优化,对新器件的性能潜力挖掘不如 Vivado。

- Vivado: 使用 Vivado Synthesis。布局布线引擎是全新开发的,针对 7 系列及后续器件的复杂架构(如 UltraRAM、高速收发器、时钟资源、异构资源)进行了深度优化,在时序收敛、资源利用率、性能功耗比方面有显著优势,特别是在设计规模大、时钟频率高时。

-

设计分析与调试:

- ISE: 提供基本的时序报告、资源报告等。

- Vivado: 提供更强大、更可视化的分析工具:

- 时序分析器: 更详细、直观的时序路径分析。

- 功耗分析器: 更精确的功耗估算和热分析。

- 设计布局查看器: 可视化器件的布局布线结果。

- 高层次综合: 支持使用 C/C++/SystemC 进行设计(通过 Vitis HLS)。

- 逻辑分析仪: 集成的 ILA (Integrated Logic Analyzer) 调试更方便。ChipScope 是 ISE 时代的类似工具。

-

性能和效率:

- Vivado 在以下方面具有显著优势:

- 编译速度: 对于大型设计,尤其是 7 系列以后器件,速度通常更快。

- 时序收敛能力: 先进的引擎和优化策略使其更容易达到高频率目标(Timing Closure)。

- 资源利用: 能更有效地利用新型器件中的专用资源。

- 增量编译: 支持功能强大得多的增量设计和编译,极大地加速设计迭代。

- 多线程支持: 更好地利用多核 CPU 进行并行处理。

- Vivado 在以下方面具有显著优势:

总结与选择建议:

- 如果你需要开发或维护基于 Xilinx Spartan-6, Virtex-6 或更早器件(Spartan-3, Virtex-4/5 等)或者 CoolRunner II CPLD 的项目,你必须使用 ISE。

- 对于所有 Xilinx Artix-7, Kintex-7, Virtex-7, Zynq-7000, UltraScale, UltraScale+, Versal 以及后续所有新型 FPGA、SoC 和 ACAP,你必须使用 Vivado Design Suite。

- 对于新项目: 强烈推荐使用 Vivado。它代表了当前和未来的方向,拥有更快的速度、更好的性能优化、更现代化的界面和更强大的功能(尤其是针对复杂系统和 IP 集成)。ISE 已经停止支持和发展。

一句话概括:ISE 是老功臣,用于旧芯片;Vivado 是新王者,用于主流和新芯片。 两者代表了 FPGA 设计工具发展史上两个重要的时代。

| 特性 | ISE (Integrated Software Environment) | Vivado Design Suite |

|---|---|---|

| 目标器件 | Spartan-6, Virtex-6 及更早器件 (S3, V4/V5) | Artix-7, Kintex-7, Virtex-7 (7系列), Zynq-7000, UltraScale, UltraScale+, Versal 及后续所有新型号 |

| 开发状态 | 已停产 (约2013年),仅用于维护老项目 | 当前主流开发套件,持续更新 |

| 核心架构 | 传统工具链拼接 | 革命性新架构:统一数据库,基于 IP 和系统中心设计 |

| 关键组件 | XST (综合), 传统布局布线引擎 | Vivado Synthesis, Vivado IPI (IP集成器), 全新优化布局布线引擎 |

| 用户界面 | Project Navigator (基础) | 现代化、功能丰富 GUI,深度集成 Tcl 脚本化控制 |

| 设计流程 | 相对分散 | 高度集成化、智能化 |

| 主要优势 | 兼容性 (旧器件必需) | 时序收敛能力更强, 编译速度更快 (尤其大型设计), 资源利用更优, 高级分析调试工具, 强大的增量编译支持 |

| 适用场景 | 必须用于 Spartan-6/Virtex-6 及之前的器件项目 | 必须用于 7系列及之后所有新器件的新项目 |

希望这个中文解释能帮助你理解 Vivado 和 ISE 的区别!你在使用中遇到具体问题了吗?比如兼容性切换或者功能对比之类的?

Tcl在Vivado中的应用

Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09

ISE工程升级到Vivado及板级信号调试

版本迁移的操作想必大家已经做过不少了,其中包括从ISE转换到vivado与vivado老版本迁移到新版本。郑智海同学给大家介绍了一下如何把工程从

2023-01-30 09:11:30

Tcl在Vivado中的基础应用

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2022-09-14 09:09:56

利用ISE的SDRAM设计的FIFO实验

利用ISE的SDRAM设计的FIFO实验(嵌入式开发转后端开发)-利用ISE的SDRAM设计的FIFO实验,适合感兴趣的学习者学习,可以提高自己的能力,大家可以多交流哈

资料下载

![]() 张文

2021-08-04 12:14:36

张文

2021-08-04 12:14:36

什么是Vivado?资料下载

电子发烧友网为你提供什么是Vivado?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

资料下载

![]() h1654155957.9921

2021-04-07 08:51:46

h1654155957.9921

2021-04-07 08:51:46

Vivado设计流程指导手册

Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado

资料下载

![]() 姚小熊27

2021-03-22 11:39:53

姚小熊27

2021-03-22 11:39:53

Vivado与ISE的开发流程以及性能差异

特性比较对 Vivado 和它的前一代设计套件,ISE 做一个组件功能上的平行比较和总结是很有用的。其目的是让那些具有在 ISE 下工作经验 (

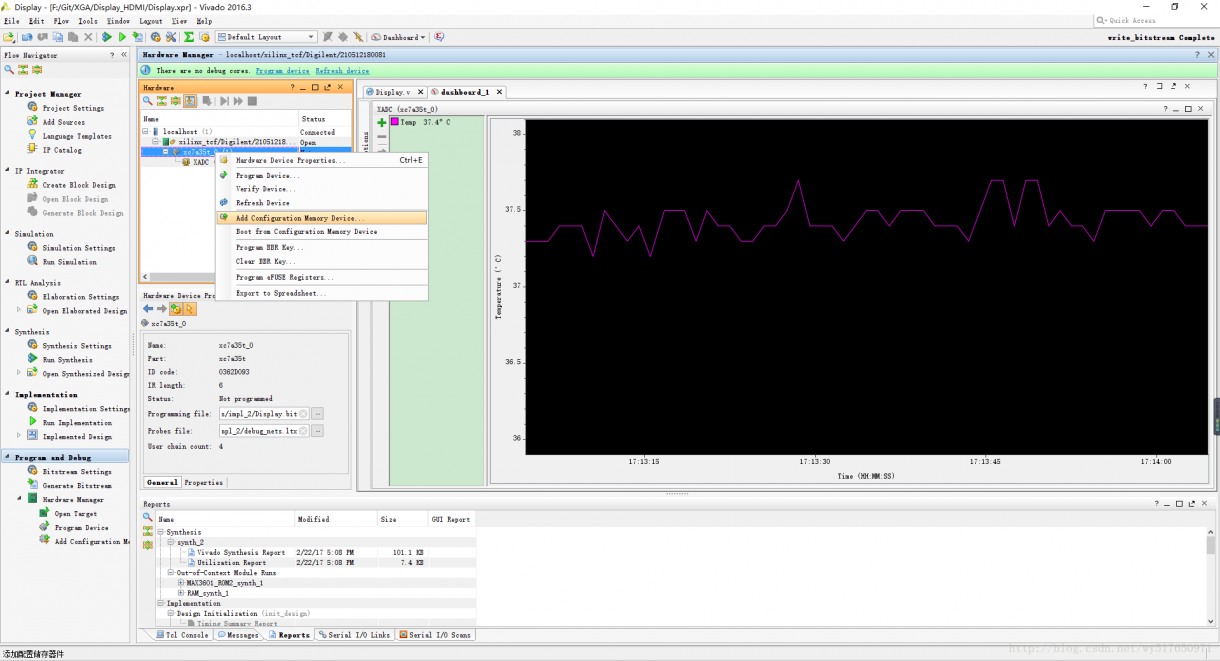

Vivado下载程序步骤和ISE差异问题

由于Vivado下载程序步骤和ISE有较大差异,特此写此文章,希望对大家有所帮助。 1,下载文件生成 在.bit文件生成后,在TCL中输入 write_cfgmem -format mcs

2021-01-02 10:45:00

使用vivado的过程如何清理/压缩不必要的文件

作者:材哥,玩儿转FPGA 前言 vivado和ISE的使用差别很大,Vivado是专门针对7系列和以后系列的FPGA/AP SOC进行高效设计

2020-12-25 14:53:36

如何将旧的ISE设计转移到Vivado 2014.1

你好我有一个新的vc707板。我可以将旧的ISE设计转移到Vivado 2014.1。使用Vivado,我可以通过USB电缆将我的比特流下载到电

是否有像ISE一样的vivado中的任何测试平台?

嗨, 我想知道是否有像ISE一样的vivado中的任何测试平台。在ISE中点击添加源我们得到vhd testbech module.but在

请问怎么从ISE中找到类似的vivado改变工具?

我发现vivado可以改变工具中的featuresaboutSynthesis - settings - Synthesis。但我在ISE中找不到类似的东西。如果有人知道设置在哪里。非常感谢你!

EDK和ISE设计新东西可以使用Vivado吗?

使用:System Generator,EDK和ISE设计新东西(或者Vivado,BTW:我可以使用Vivado吗?我看到它被说明在AR#51

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览