vivado 提高速度

在 Vivado 设计流程中提高运行速度(包括综合、实现和比特流生成)可以从以下几个关键方向优化,以下是具体的中文建议:

1. 硬件与系统优化

- 内存与CPU:

- 内存:确保 ≥ 32GB RAM(大规模设计需 64GB+),避免因内存不足触发磁盘交换。

- CPU:使用多核处理器(如 8 核以上),在设置中启用多线程(

tcl设置:set_param general.maxThreads 8)。

- 存储:

- SSD硬盘:将工程、源码和Vivado安装目录全部放在NVMe SSD上。

- 禁用杀毒软件:排除工程目录的实时扫描,减少I/O干扰。

2. Vivado 工程设置优化

- 增量编译(Incremental Compile):

- 仅对修改部分重新编译,适合迭代开发。

- 流程:

launch_runs impl_1 -to_step write_bitstream -jobs 8后续修改后:

launch_runs impl_1 -incremental -jobs 8

- Out-of-Context (OOC) 综合:

- 对稳定模块独立综合,避免重复处理。

- 操作:在源文件中右键模块 → Set as Out-of-Context for Synthesis。

- 综合与实现策略:

- 选择 Performance_ 策略(如

Performance_Explore)。 - 在

Run Settings中调整优化等级:set_property strategy Performance_Explore [get_runs synth_1] set_property steps.opt_design.args.directive Explore [get_runs impl_1]

- 选择 Performance_ 策略(如

3. 代码与约束优化

- RTL 代码:

- 避免跨时钟域的大规模逻辑(如

for循环生成深层次组合逻辑)。 - 使用寄存器分割关键路径(添加 pipeline 阶段)。

- 减少

generate语句的嵌套层次。

- 避免跨时钟域的大规模逻辑(如

- 约束(XDC):

- 精确约束时钟(避免过度约束导致工具耗时优化非关键路径):

create_clock -period 5 [get_ports clk] set_clock_groups -asynchronous -group [get_clocks clk1] -group [get_clocks clk2] - 使用

max_paths限制报告数量,缩短时序分析时间:set_max_paths 1000

- 精确约束时钟(避免过度约束导致工具耗时优化非关键路径):

4. 流程控制技巧

- 分步运行(Non-Project Mode):

- 直接使用 Tcl 命令分步骤控制,避免 GUI 开销:

synth_design -top top_module -part xc7k325tffg900-2 opt_design place_design route_design write_bitstream -file output.bit

- 直接使用 Tcl 命令分步骤控制,避免 GUI 开销:

- 跳过时序检查(谨慎使用):

- 在初期验证阶段可跳过耗时的时间检查:

route_design -no_timing_driven

- 在初期验证阶段可跳过耗时的时间检查:

5. 高级功能(适合 UltraScale+/Versal)

- 设计冻结(Design Freeze):

- 对已布局模块锁定(

lock_design -level routing),后续修改不影响其布局布线。

- 对已布局模块锁定(

- 部分重配置(Partial Reconfiguration):

- 仅修改部分模块,大幅缩短实现时间。

6. 维护与清理

- 清理临时文件:

- 定期删除工程目录下的

.cache、.ip_user_files等缓存。

- 定期删除工程目录下的

- 版本管理:

- 将输出文件(.bit/.ltx)与工程分离,避免版本控制拖慢 Vivado。

温馨提示

⚠️ 权衡优化目标:速度优化可能导致时序违例或功耗上升。完成优化后务必进行完整的时序验证(

report_timing_summary)。

推荐优先级:

graph LR

A[更换SSD + 内存升级] --> B[启用增量编译/OOC综合]

B --> C[调整综合/实现策略]

C --> D[优化RTL代码/约束]

D --> E[使用Non-Project模式]通过多维度优化,Vivado 流程速度可显著提升(尤其对大型设计,速度可能提升 2-5 倍)。

使用直接寻址方式提高速度

在嵌入式系统,特别是资源受限的环境中,尽量使用直接寻址方式来提高速度是一个有效的优化策略。以下是一些具体方法和示例,帮助你尽可能多地使用直接寻址的变量,从而提高系统性能。 直接寻址的优势 直接寻址

RH118:精确度、高速度业务放大器数据表 ADI

电子发烧友网为你提供ADI(ADI)RH118:精确度、高速度业务放大器数据表相关产品参数、数据手册,更有RH118:精确度、高速度业务放大器数据表的引脚图、接线图、封装手册、中文资料、英文资料

RH6200M-低Noise,高速度RIL-RIO-RAIL-AIL-AIL-OP

RH6200M-低Noise,高速度RIL-RIO-RAIL-AIL-AIL-OP

资料下载

![]() 吴湛

2021-05-26 21:12:26

吴湛

2021-05-26 21:12:26

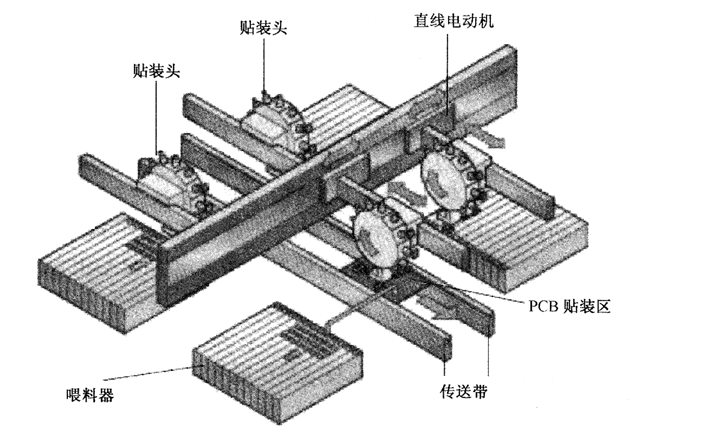

高速度高贴片机

高速度高贴片机主要采用复合式结构。复合式结构机器是从动臂式机器发展而来,它集合了转塔式和动臂式的特点,在动臂上安装有转塔式贴片头(又称转盘),组成转盘动臂式结构如图所示从而大大提高了单臂的吸嘴数量

2023-09-27 15:20:18

求提高速度的建议?

我无法从这段代码中获得所需的150 MHz。有没有人有任何关于提高速度的建议?assign idata_out = {temp_real_data [29],temp_real_data [26

BRAM的最高速度是多少

嗨,考虑到所有因素,设备BRAM的最高速度是多少,它是FPGA速度的25/50 / 75%?是的我知道外部延迟和路由将最终控制最大值,但有任何技术考虑因素表明BRAM只能以设备

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机