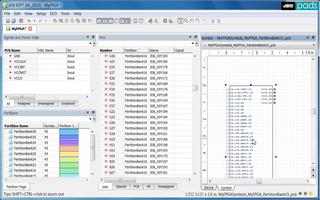

fpga pcb图

更多

理解您需要关于FPGA PCB设计的指导。以下是关键内容的中文详解(含核心要点及设计建议):

一、FPGA PCB设计核心要素

-

器件布局

- FPGA芯片:优先居中放置,缩短高速信号路径;预留散热空间(尤其大容量型号)。

- 电源电路:多电压域(如1.0V/1.2V/2.5V)需独立布局,磁珠/电感隔离避免干扰。

- 时钟发生器:靠近FPGA时钟输入引脚,缩短走线;避免穿越噪声区域(电源/数字接口)。

- 高速接口:DDR内存、GTX收发器等靠近FPGA对应Bank,优先使用阻抗匹配层。

-

叠层规划(6层板示例) 层序 功能 说明 L1 信号层 关键布线(时钟、差分对) L2 GND平面 完整参考地 L3 信号层 中低速信号 L4 电源平面 分割区域(VDCORE/VCCIO) L5 信号层 普通布线 L6 GND平面 底层屏蔽 -

高速信号设计

- 差分对(PCIe/SATA):严格等长±5mil内,对称平行走线;禁止跨越平面分割。

- DDR内存:地址/控制线分组等长,Fly-by拓扑优先;时序余量预留10%。

- 终端电阻:源端匹配(33Ω)用于单端信号;AC耦合电容靠近接收端。

-

电源完整性(PI)

- 多级滤波:每路电源入口→10μF陶瓷+0.1μF MLCC→0.01μF MLCC。

- 大电流路径:≥2oz铜厚;Core电源用铜箔填充+多过孔阵列(通流能力翻倍)。

- 动态响应:FPGA旁放置钽电容(100μF)应对瞬时电流。

二、设计避坑清单

- ⚡ 去耦电容:每个电源引脚<3mm放置,VCCINT/VCCIO优先。

- ?️ 散热:底部放置Thermal Pad + 4×过孔阵列(孔径≥0.3mm)传导至散热器。

- ? JTAG接口:串接22Ω电阻防震荡,远离高速信号线。

- ? 制造约束:阻抗控制线宽公差±10%,BGA区域禁用0.1mm以下过孔。

三、必备设计工具推荐

-

仿真验证

- HyperLynx:DDR时序/眼图分析

- SIwave:电源噪声与谐振点扫描

-

实用工具

# PCB走线阻抗计算工具(示例) def calc_impedance(w, t, h, εr): # w:线宽(mm), t:铜厚(um), h:介质厚度(mm), εr:介电常数 Zo = 87 / (εr**0.5) * (h / w) # 简化模型 return f"{Zo:.1f}Ω" print(calc_impedance(0.15, 35, 0.2, 4.2)) # 输出:49.8Ω

四、设计检查表(投板前必做)

| 项目 | 检查点 |

|---|---|

| 电气规则 | 电源/地短路检查;未连接网络 |

| 信号完整性 | 所有高速线阻抗仿真通过 |

| DFM | BGA阻焊桥 ≥4mil;丝印避让 |

| 热设计 | 芯片结温 < 85℃ (满负荷) |

如需以下扩展内容,请告知:

- 具体案例:Xilinx Zynq MPSoC的DDR4布局指南

- 进阶技巧:20Gbps高速收发器的背钻设计

- 开源参考:Lattice FPGA核心板PCB文件(GitHub链接)

请注意:实际设计需结合FPGA型号手册(尤其是Power Distribution Network章节)及PCB厂商工艺参数调整。

Xilinx 7系列FPGA PCB设计指导

由PCB制造商定义,这些直径限制了通孔之间的可用空间量与最大走线宽度。PCB制造限制限制了最小走线宽度和最小间距。 图4、12层

2024-07-19 16:56:37

在FPGA上为FPGA设计PCB的步骤详解

在 FPGA(Zynq™ UltraScale+™ MPSoC) 上的 Ubuntu 22.04 桌面映像上安装了各种 EE 设计应用程序(包括 KiCad),并用它设计 PCB。

2024-02-26 09:04:27

在PCB上设计大容量引脚FPGA

FPGA System Planner解决了设计一个或多个工程师时遇到的挑战PCB板上的更多大引脚数FPGA。

资料下载

![]() 姚小熊27

2021-03-16 16:56:15

姚小熊27

2021-03-16 16:56:15

7天热门专题

换一换

换一换

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机