i2c总线信号时序的分析介绍

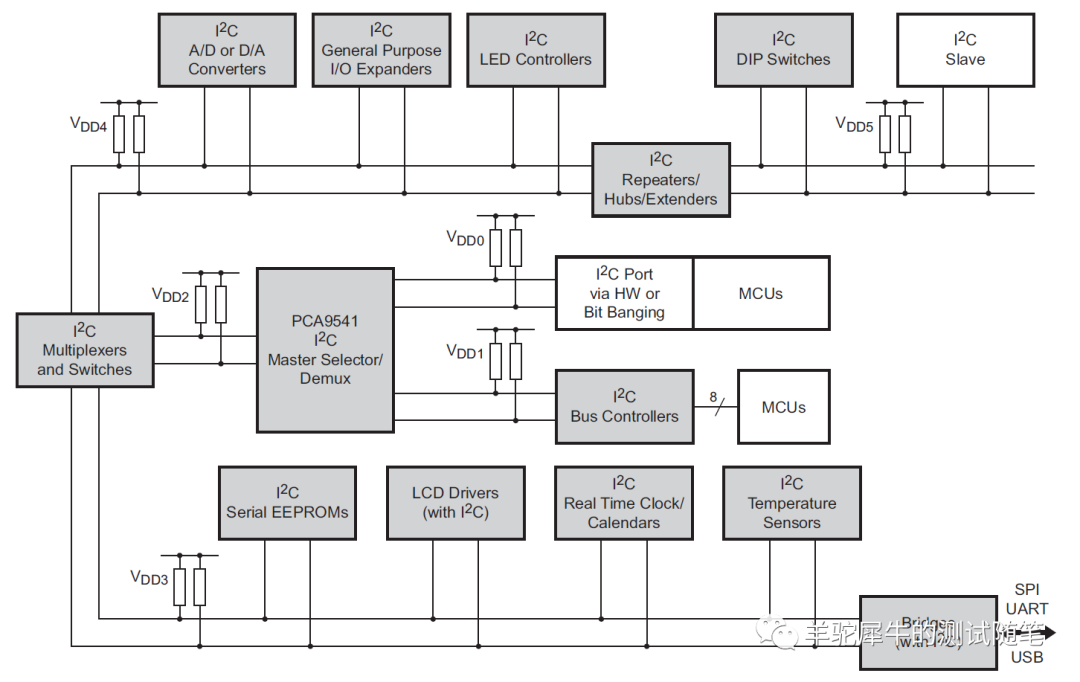

I2C总线是一个真正的多主机总线,如果两个或多个主机同时初始化数据传输,可以通过冲突检测和仲裁防止数据破坏,每个连接到总线上的器件都有唯一的地址,任何器件既可以作为主机也可以作为从机,但同一时刻只允许有一个主机。

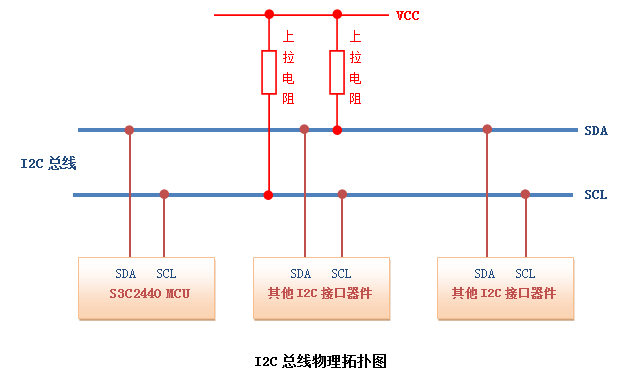

好的,我们来详细分析介绍 I2C 总线的信号时序。I2C (Inter-Integrated Circuit) 是一种广泛使用的同步、多主/从、串行通信总线标准,其通信完全由两根信号线控制:SDA (Serial Data Line) 和 SCL (Serial Clock Line)。理解其信号时序对于调试和使用 I2C 设备至关重要。

核心概念:

- 同步通信: 所有数据传输都与由主设备(Master)产生的时钟信号(SCL)同步。

- 开漏输出(Open-Drain): I2C 物理层标准要求设备使用开漏输出驱动总线。这意味着:

- 设备只能将信号线主动拉低(驱动为逻辑

0)。 - 无法主动将信号线驱动为高电平(逻辑

1)。 - 要达到逻辑

1状态,需要依赖 上拉电阻 (通常接在 SDA 和 SCL 线上拉到 VCC)。当总线上的所有设备都不主动拉低时,上拉电阻将信号拉高。 - 优点: 实现了“线与”(Wire-AND)逻辑,允许多个设备驱动总线而不损坏;支持不同电压逻辑的设备共存(需电平转换器)。

- 设备只能将信号线主动拉低(驱动为逻辑

- 数据有效性: SDA 线上的数据必须在 SCL 高电平期间保持稳定。只有 SCL 处于低电平期间,SDA 线上的数据才允许发生变化。

I2C 时序关键元素详解:

-

空闲状态 (Bus Free / Idle State):

- 条件: SDA 和 SCL 都通过上拉电阻保持在高电平。

- 含义: 表示当前没有主设备在使用总线,或者通信处于停止状态。

-

时序图示意:

SCL: ------------ HIGH ----------------- SDA: ------------ HIGH -----------------

-

起始条件 (START Condition, S):

- 产生: 由主设备发起,标志着一次通信传输的开始。

- 时序: 在 SCL 线为高电平期间,主设备将 SDA 线从高电平拉到低电平。

- 作用: 通知总线上的所有从设备,即将进行数据传输。

- 唯一性: 总线在任何时刻只能有一个有效的起始条件。

- 时序图示意:

SCL: HIGH -----___ SDA: HIGH --__ \_\_\_\_\_\_\_\_\_\_\_\_\_ LOW ^ |--- START Condition (S)

-

停止条件 (STOP Condition, P):

- 产生: 由主设备发起,标志着一次通信传输的结束。

- 时序: 在 SCL 线为高电平期间,主设备将 SDA 线从低电平释放到高电平(通过停止拉低 SDA,上拉电阻将其拉高)。

- 作用: 通知总线上的所有设备,本次传输结束,总线将进入空闲状态。

- 唯一性: 总线在任何时刻只能有一个有效的停止条件。

- 时序图示意:

SCL: __________________ HIGH --------- SDA: ______ LOW ______________________ HIGH ^ |--- STOP Condition (P)

-

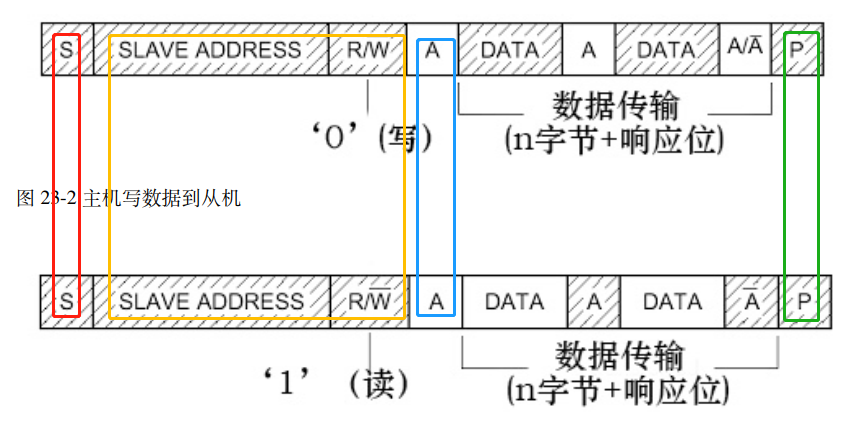

数据传输 (Data Transfer):

- 单位: 数据以字节(Byte) 为单位传输(MSB - Most Significant Bit first)。

- 位传输: 每个数据位在 SCL 的一个完整时钟周期内传输。

- 数据有效性规则:

- 稳定期: SCL 为高电平期间,SDA 线上的数据必须保持稳定不变(有效数据位)。从设备通常在此时钟沿读取数据。

- 变化期: SDA 线上的数据只允许在 SCL 为低电平时改变。发送器(主或从)在此低电平期间更新下一比特的数据。

- 时序图示意 (传输一位):

SCL: __ (LOW) ______ (HIGH) __ (LOW) ______ SDA: _______________ BIT n _______________ | | | |<-数据改变->|<-稳定期/采样点->

-

应答位 (Acknowledge Bit, ACK):

- 位置: 紧随每个字节(8位)传输之后。

- 目的: 接收方(Receiver)向发送方(Transmitter)报告是否成功接收到该字节。

- 产生: 由接收方在发送方释放 SDA 线(在第9个 SCL 周期)后产生。

- ACK (应答): 接收方在 SCL 的第9个时钟周期将 SDA 线拉低。

发送方 (释放 SDA): 停止驱动SDA (进入输入模式, SDA线由上拉电阻拉高) 接收方 (驱动 ACK): 在第9个SCL脉冲的稳定期(SCL HIGH期间)内将SDA拉低。 - NACK (非应答): 接收方在第9个 SCL 时钟周期内保持 SDA 线为高(不拉低)。

- ACK (应答): 接收方在 SCL 的第9个时钟周期将 SDA 线拉低。

- 主控:

- 写操作(主发数据给从):主设备是发送方,从设备是接收方。主设备在发完8位数据后(第9个SCL时钟),会释放 SDA(准备接收ACK)。从设备需要在这个时钟周期驱动 SDA 回应 ACK 或 NACK。

- 读操作(主从从读取):主设备是接收方,从设备是发送方。主设备在读取完8位数据后(第9个SCL时钟),需要驱动 SDA 发出 ACK(继续读取下一个字节)或 NACK(停止读取)信号给从设备。

- 时序图示意 (ACK):

SCL: [1] [2] [3] [4] [5] [6] [7] [8] [9] SDA: [D7] [D6] [...] [D0] [ACK=LOW] ^ |-- 接收方驱动 ACK (拉低) - 时序图示意 (NACK):

SCL: [1] [2] [3] [4] [5] [6] [7] [8] [9] SDA: [D7] [D6] [...] [D0] [NACK=HIGH] ^ |-- 接收方不驱动 (SDA保持由电阻拉高) 或 主动驱动为高(少见)

-

重复起始条件 (Repeated START Condition, Sr):

- 本质: 就是一个标准的起始条件 (

S)。 - 位置: 在起始条件 (

S) 之后,在停止条件 (P) 之前。 - 作用: 允许主设备在不释放总线控制权(不发送

P)的情况下,发起一次新的传输(通常针对新的从设备地址或新的读写方向)。它不会终止前一次通信,只是将前一次通信与即将开始的新通信结合成一个复合通信。 - 优势: 避免其他潜在主设备在两次传输之间抢占总线,提高效率。

- 时序: 与起始条件完全相同:在 SCL 为高期间,主设备拉低 SDA。

- 本质: 就是一个标准的起始条件 (

关键时序参数 (通常在I2C规范中定义):

以下是 I2C 规范中定义的一些关键时间间隔,它们规定了信号转换的最小或最大时间要求,确保设备间可靠通信:

| 参数名称 | 符号 | 描述 | 影响 |

|---|---|---|---|

| SCL时钟频率 | Fscl | SCL 线的工作频率,标准模式:100kHz, 快速模式:400kHz, 高速模式:3.4MHz 等。 | 决定数据传输速率 |

| 起始条件保持时间 | THD;STA | START 条件后,SCL 变为低电平之前,SCL 被主设备拉低前必须保持的最短时间。 | 确保从设备能检测到起始条件 |

| 重复起始条件建立时间 | TSU;STA | Sr 条件前,SCL 被释放为高电平后需要保持的最短时间。 | 确保从设备准备好接收新的地址 |

| 停止条件建立时间 | TSU;STO | STOP 条件前,SCL 被释放为高电平后需要保持的最短时间。 | 确保数据完整性 |

| SDA 数据建立时间 | TSU;DAT | SCL 上升沿(采样点)之前,SDA 数据线上信号必须保持稳定的最短时间。 | 保证数据在采样时是稳定的 |

| SDA 数据保持时间 | THD;DAT | SCL 上升沿(采样点)之后,SDA 数据线上信号必须保持稳定的最短时间。 | 保证数据在采样后足够时间 |

| SDA 输出下降时间 | TF | SDA 线从高电平到低电平的最大允许转换时间。 | 影响信号边沿速度 |

| SDA / SCL 上升时间 | TR | SDA 或 SCL 线从低电平上升到高电平的最大允许时间。 | 影响空闲恢复速度和信号完整性 |

| SCL 低电平持续时间 | TLOW | SCL 线维持低电平的最短时间。 | 决定低电平宽度 |

| SCL 高电平持续时间 | THIGH | SCL 线维持高电平的最短时间。 | 决定高电平宽度 |

| 总线空闲时间 | TBUF | STOP 条件后到新的 START 条件之间的最短时间。 | 确保总线恢复空闲状态 |

| 噪声抑制时间 | TSP | 输入端的噪声过滤器参数(非示波器直接测量参数)。 | 滤除总线上的窄脉冲干扰 |

提示:

- 这些参数的具体数值取决于你使用的 I2C 模式(Standard-mode, Fast-mode, Fast-mode Plus, High-speed mode)。

- 在调试 I2C 通信问题时,用示波器观察 SDA 和 SCL 的实际波形,并核对是否符合上述的规则和要求(特别是数据有效窗口、起始/停止条件、ACK/NACK),是定位问题的有效方法。

- 最重要最核心的时序规则:SCL 为高时 SDA 必须稳定;SDA 变化只能发生在 SCL 为低时。

常见时序相关调试问题:

- ACK/NACK 缺失或不正确: 设备不响应、地址错误、寄存器地址错误、设备忙、总线冲突。

- 数据错误: 采样点时机不对(违背数据建立/保持时间

T<sub>SU;DAT</sub>/T<sub>HD;DAT</sub>)、上升/下降时间 (T<sub>R</sub>/T<sub>F</sub>) 太长导致信号畸变(检查上拉电阻阻值)、电磁干扰。 - 起始/停止条件不被识别: 主设备驱动波形不符合规范(检查

T<sub>HD;STA</sub>,T<sub>SU;STO</sub>等),或者多个主设备竞争总线。 - 总线被长时间拉低 (LOCK-UP): 设备故障(如 MCU 死机持续驱动 SDA/SCL 低)、严重总线冲突、缺少上拉电阻。

- 设备无反应: 检查起始条件是否正确、设备地址是否正确、电源/连接是否正常、SCL 线是否连接。

总结:

掌握 I2C 总线时序的核心在于理解 SDA 和 SCL 之间的严格同步关系,特别是“SCL 高时 SDA 稳定,SCL 低时 SDA 可变”的数据有效性规则,以及 START/STOP 条件的定义、ACK/NACK 的响应机制。结合示波器观察波形并对照规范定义的时序参数进行分析,是解决 I2C 通信问题的关键技能。

嵌入式内核及驱动开发-09IIC子系统框架使用(I2C协议和时序,I2C驱动框架,I2C从设备驱动开发,MPU6050硬件连接

文章目录I2c协议和时序I2c介绍

资料下载

![]() tr12345

2021-12-06 14:06:07

tr12345

2021-12-06 14:06:07

简述I2C总线协议

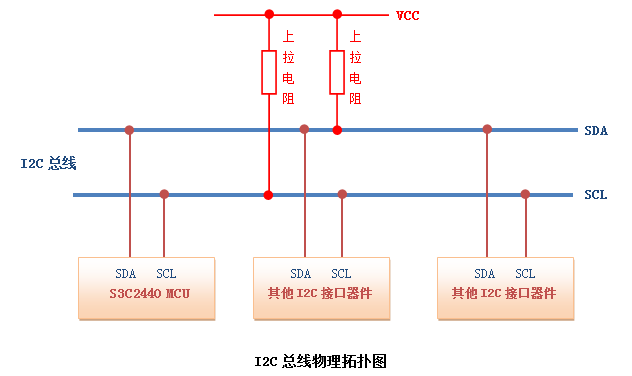

I2C 总线在物理连接上非常简单,分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低电平时序的

2023-02-13 10:14:21

I2C总线物理拓扑结构_I2C总线协议解析

I2C 总线在物理连接上非常简单,分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低电平时序的

2020-09-24 14:12:09

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 芯片的工作原理是什么?

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- dtmb信号覆盖城市查询

- 怎样挑选路由器?

- 华为芯片为什么受制于美国?

- 元宇宙概念股龙头一览

- type-c四根线接法图解

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- BLDC电机技术分析

- 复位电路的原理及作用

- dsp是什么意思?有什么作用?

- iphone13promax电池容量是多少毫安

- 苹果无线充电器怎么使用?

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 传感器常见类型有哪些?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机