cadence原理图库制作

在 Cadence 设计工具(主要指 OrCAD Capture/Capture CIS,这是最常用的原理图输入工具)中制作原理图库(.olb 文件)是硬件设计的基础步骤。以下是详细的制作流程和关键注意事项:

核心步骤:

-

打开或新建库文件:

- 启动 OrCAD Capture。

File>New>Library:创建一个新的空白原理图库文件(.olb)。- 或

File>Open>Library:打开一个现有的库文件进行编辑。

-

创建新元件 (Part):

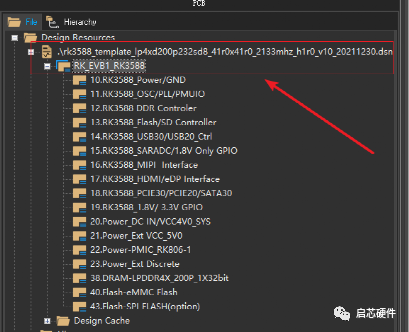

- 在项目管理器 (Project Manager) 窗口中,找到并展开你的库文件 (

.olb)。 - 右键点击

Library名称(或里面的Parts文件夹)。 - 选择

New Part。

- 在项目管理器 (Project Manager) 窗口中,找到并展开你的库文件 (

-

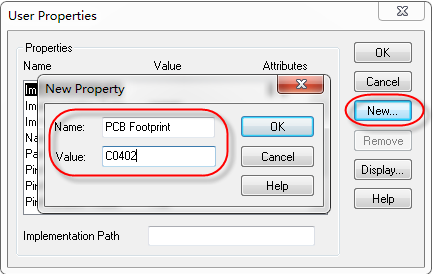

设置元件属性: 在弹出的

New Part Properties对话框中设置关键参数:- Name: 元件的唯一标识符(如

LM358,RES_10K_0603,SN74HC00)。命名需清晰、规范。 - Part Reference Prefix: 元件在原理图中的默认标识前缀(如电阻用

R, 电容用C, IC 用U, 二极管用D)。 - PCB Footprint: 最重要属性之一! 输入该元件对应的 PCB 封装名称(如

R0603,C0805,SOIC-8)。必须与后续 PCB 设计库中的封装名严格一致。 - Parts per Pkg: 一个元件符号代表几个物理单元(管脚封装)。

1:大多数分立元件、单芯片 IC。>1(如2,4):多单元元件(如一个封装里有 4 个独立门电路的74HC00)。选择此项后会进入多部分元件编辑模式。

- Homogeneous: 勾选表示所有单元相同(如

74HC00的 4 个与非门都一样)。 - Heterogeneous: 不勾选表示单元不同(较少见,如复杂 IC 的不同功能块)。

- Pin Number Visible: 是否显示管脚编号(通常推荐显示)。

- Part Aliases: 可为元件添加别名(如不同厂商对同一器件的不同命名)。

- 点击

OK进入符号编辑窗口。

- Name: 元件的唯一标识符(如

-

绘制元件符号外形:

- 使用右侧绘图工具栏(Place > Rectangle / Polygon / Ellipse / Arc / Line)绘制元件的主体轮廓。形状仅代表电气功能,不必与实际物理尺寸一致,但要清晰美观。

- 常用矩形表示 IC。

- 确保图形放置在栅格上(

Options>Preferences>Grid Display可设置),保持图纸整洁。

-

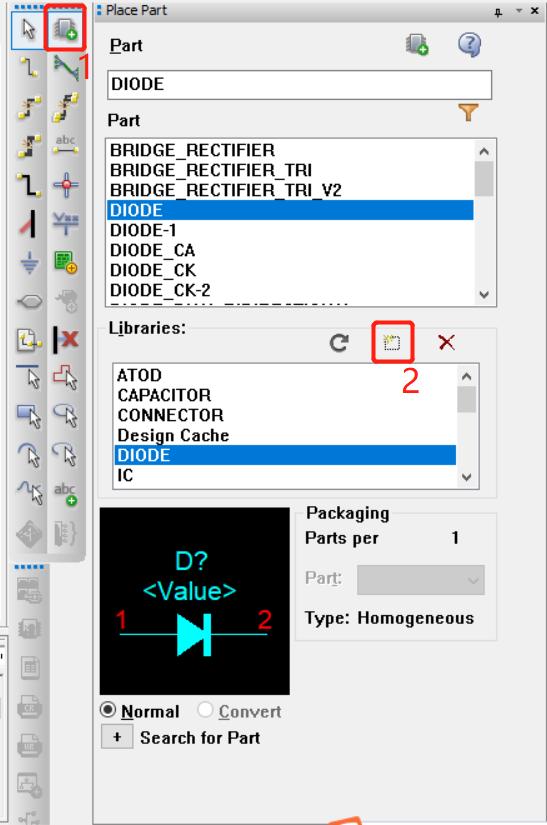

放置管脚 (Place Pin):

- 点击右侧工具栏的

Place Pin图标或菜单Place>Pin。 - 弹出

Place Pin对话框:- Name: 管脚功能名(如

VCC,GND,IN+,OUT,CLK)。命名要准确反映功能。 - Number: 最关键属性! 管脚编号(如

1,2,A13)。必须与元器件数据手册(datasheet)和 PCB 封装中的编号完全一致! - Shape: 管脚图形样式(Line, Short, Zero Length, Clock, Dot, Dot-Clock, Schmitt...)。用于直观表示信号类型(如

Clock表示时钟,Dot表示低电平有效)。 - Type: 管脚电气类型 (Electrical Type),对 ERC(电气规则检查)至关重要!

Passive:被动(电阻、电容、普通 IO 等)Input:输入Output:输出Bidirectional:双向(如数据总线)Power:电源引脚(即使名字不是 VCC/GND)Ground:地引脚OpenEmitter/Drain/Collector:开漏/开集电极3-State:三态

- Width: 一般选

Scalar。Bus用于总线引脚(较少直接在元件符号上使用)。

- Name: 管脚功能名(如

- 点击

OK,光标附带引脚符号,将其放置在符号轮廓的合适边界上(通常在栅格点上)。 - 关键原则:

- 电源和地引脚: 习惯放在元件符号的顶部(VCC/VDD等) 和底部(GND/VSS等)。电气类型必须设为

Power或Ground。 - 输入引脚: 通常在左侧。

- 输出引脚: 通常在右侧。

- 信号流向: 布局应尽量体现信号流向(从左到右)。

- 引脚间距: 均匀,建议使用栅格(如 0.1 inch 或 2.54mm)。

- 分组: 功能相关的引脚靠近放置。

- 名称可见性: 确保引脚名清晰可见(可用

Edit>Properties选中引脚后批量修改显示属性)。

- 电源和地引脚: 习惯放在元件符号的顶部(VCC/VDD等) 和底部(GND/VSS等)。电气类型必须设为

- 点击右侧工具栏的

-

放置电源/地符号(可选但推荐):

- 对于分离的电源/地引脚(非通过

Power/Ground类型隐式连接),可以在符号轮廓内部靠近引脚的地方放置Place>Power(或GND)图标。这些符号通常与全局网络关联。 - 注意: 这只是视觉符号,引脚本身的电气类型 (

Power/Ground) 和网络名才是关键连接依据。

- 对于分离的电源/地引脚(非通过

-

添加文本信息:

Place>Text:添加元件名称、型号、关键参数等(如0.1uF,10kΩ)。- 放置

Name和Part Reference(如U?,R?),通常在符号上方或中心。

-

保存元件:

- 绘制完成后,关闭该元件的编辑窗口。

- 在项目管理器 (Project Manager) 的库列表中,右键点击该元件名 (

Part),选择Save或直接保存整个库文件 (File>Save)。

-

编辑现有元件:

- 在项目管理器中双击库里的元件名,或右键选择

Edit Part。

- 在项目管理器中双击库里的元件名,或右键选择

关键注意事项与最佳实践:

-

精准性至上:

- 引脚编号 (Pin Number): 务必与 Datasheet 和 PCB 封装一字不差。一个错位可能导致 PCB 报废。

- 引脚名称 (Pin Name): 准确反映功能(如

/CS表示低电平有效片选,RESET而非RST如果手册如此命名)。 - 电气类型 (Pin Type): 正确设置(特别是

Power/Ground/Input/Output)对 ERC 至关重要。电源脚误设为Passive会导致 ERC 错误。

-

PCB 封装关联:

PCB Footprint属性绝对不能为空或错误。这是原理图符号与物理封装的桥梁。确保名称与 PCB 库 (.dra/.psm) 中的封装名完全一致(区分大小写!)。

-

清晰性与一致性:

- 命名规范: 制定并遵守公司和项目的元件命名规则(如

CAP_CER_10nF_50V_0603_X7R)。 - 符号风格: 保持库内符号风格统一(大小、引脚方向、文本位置)。

- 栅格对齐: 所有元素(轮廓、引脚)严格对齐栅格,保证原理图整洁和连接可靠。

- 隐藏引脚: 对于必须连接到全局网络的引脚(如

VCC),可将其设为Power类型并勾选Pin Visible使其在原理图中不显示(避免视觉混乱),但确保其Name和Number正确且关联了正确的全局网络(如VCC)。

- 命名规范: 制定并遵守公司和项目的元件命名规则(如

-

多部分元件处理:

Parts per Pkg > 1时,每个单元 (Part A,Part B...) 需要单独编辑其引脚。- 引脚分配: 将功能相关的引脚合理分配到不同的单元(如电源/地放在一个单元)。

- 单元标识: 确保每个单元有清晰的标识(如

A,B,C,D或Gates,Power)。 - 电源引脚: 通常只在一个单元(如

Power单元)放置,并在其他单元中隐藏(通过属性设置)。

-

利用已有资源:

- 厂商库: 优先使用芯片厂商提供的官方

.olb库(通常官网下载)。 - 复制修改: 找到类似的元件,右键

Copy,然后在新元件上右键Paste进行修改,效率更高。 - CIS 数据库: 对于企业级应用,使用 Capture CIS 连接数据库管理元件(包含符号、封装、参数、供应商、价格等信息),实现高效管理和复用。

- 厂商库: 优先使用芯片厂商提供的官方

-

版本管理与备份:

- 使用版本控制系统 (如 Git, SVN) 管理库文件,记录变更历史。

- 定期备份库文件。

-

设计规范:

- 遵循公司或项目的硬件设计规范(如电源/地引脚放置规则、引脚类型定义规则)。

总结流程:

新建/打开库->新建元件->设置属性(Name, Prefix, Footprint, Parts/Pkg)->绘制轮廓->放置引脚(重点:Name, Number, Type, Shape)->布局优化(电源顶/地底,输入左/输出右)->添加文本->保存->严格检查(Pin Num, Footprint, Pin Type)->版本管理

掌握原理图库制作是高效、准确进行电路设计的基础。务必严谨细致,特别是引脚编号、PCB封装和电气类型这三项,错误会导致后续设计出现严重问题。

怎么显示与隐藏原理图库的PCB封装名称

这里我们分为两种情况进行分析,一种是在绘制原理图库的时候,怎么显示与隐藏元器件封装名称;另外一种是在绘制原理图的时候,怎么显示与隐藏元器件封装名称。 ①绘制原

2020-06-29 14:23:00

Cadence PCB封装制作流程

区别于altium的一库走天下,cadence的PCB套件流程中,PCB封装的制作需要单独制作pad,然后绘制封装。这两步的工具分别为Padst

2019-11-02 09:32:55

为什么原理图库引脚和封装库的引脚对应Pin Map不同?

图这是原理图库的:下图则是我要使用的PCB封装库(TO-252-2封装):原理图库 我已经添加了这个封装,并且修改了pin map通过如下图,我在原理图库

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览