cadence drc报告

好的,理解!Cadence DRC报告中文解释指南如下:

当你在Cadence Virtuoso等工具中运行完设计规则检查后,生成的DRC报告是确保你的芯片版图(Layout)符合晶圆厂(Foundry)制造工艺要求的关键文件。这份报告会列出所有违反设计规则的地方。

以下是解读Cadence DRC报告的要点(中文):

-

报告的核心目的:

- 找出并定位你的版图设计中违反设计规则的所有地方。

- 设计规则定义了制造工艺的物理极限(如最小线宽、最小间距、最小包围、最小面积、阱/衬底接触要求等),目的是确保芯片能被正确、可靠地制造出来。

-

报告的结构和关键信息 (通常在文本报告中查找):

- Header (头部信息):

- 运行日期和时间: 报告生成的时间。

- 设计名称: 你检查的版图单元名称。

- 使用的DRC规则文件:

xxx.drc或类似名称,这是晶圆厂提供的包含所有具体规则的文件。 - 运行环境/工具版本: 使用的Virtuoso版本、PVS版本或Assura版本等。

- 工艺信息: 使用的工艺节点和技术文件(例如:

tsmcN28)。

- Summary (摘要/总结):

- 总规则数: 检查了多少条设计规则。

- 违反规则数: 有多少条规则被违反了。

- 总错误数: 所有违反加起来一共有多少个具体的错误点(非常重要!)。

- 运行时间: DRC检查花了多长时间。

- 结果状态:

DRC completed successfully(检查完成) 或DRC completed with errors(检查完成但有错误) 或DRC failed(检查失败,可能规则文件或数据有问题)。- 最关心的是违反规则数和总错误数。理想状态是

0。

- 最关心的是违反规则数和总错误数。理想状态是

- Violation Details (违规详情 - 报告的核心部分): 这是你需要仔细检查和修改的部分。

- 规则名称/编号: 每一条违反的设计规则都有一个唯一的标识符。格式通常是

RuleName [RuleNumber]或类似。- 例如:

METAL1.S.1(表示金属1层的间距规则第1条),VIA1.E.2(表示通孔1层的包围规则第2条)。

- 例如:

- 错误坐标: 最重要的信息之一! 报告会列出每个错误发生的精确坐标

(X, Y)。这些坐标是你在版图编辑器中定位错误位置的依据。- 通常格式:

db: error at (12345.67, 89012.34)

- 通常格式:

- 错误描述: 对违反规则的具体解释。

- 例如:

Spacing between METAL1 shapes must be >= 0.1um(金属1图形间距必须 >= 0.1微米)METAL2 enclosure of VIA1 must be >= 0.05um on all sides(金属2对通孔1的包围在所有边上必须 >= 0.05微米)Width of POLY must be >= 0.05um(多晶硅条宽度必须 >= 0.05微米)NTAP must be connected to VSS with at least 2 contacts(N阱接触必须通过至少2个接触孔连接到VSS)

- 例如:

- 错误数量: 对于每条规则,报告会告诉你它触发了多少个具体的错误实例。

- 例如:

METAL1.S.1: 5 errors found(金属1间距规则1发现了5个错误点)。

- 例如:

- 层信息: 通常包含违反规则涉及到的层(Layer)。

- 规则名称/编号: 每一条违反的设计规则都有一个唯一的标识符。格式通常是

- Statistics (统计信息): 有时会包含更详细的统计,比如每层发生的错误数或每个规则类型的错误数。

- Footer (尾部信息): 可能包含结束时间、状态码等。

- Header (头部信息):

-

如何在版图中查看错误 (通常使用Virtuoso):

- 加载错误标记层: DRC工具在运行时会生成一个特殊的层(通常叫

DRC ERROR、VIOLATION或类似名字),包含所有错误位置的标记(通常是叉号或方框)。 - 在版图窗口中查看:

- 确保这个错误标记层是可见的。

- 报告中给出的

(X, Y)坐标,可以直接在版图窗口的坐标栏里输入,按回车键后视图会跳转到那个位置。 - 放大坐标点附近区域,就能看到错误标记和相关的版图图形。

- 结合报告中的规则描述,理解为什么那里违反了规则(是间距太小?包围不够?线太窄?)。

- 使用验证工具界面: Cadence PVS或Assura通常有自己的图形界面或浏览器,可以直接点击报告中的错误条目,自动在版图中定位并高亮显示违规的图形,非常方便。

- 加载错误标记层: DRC工具在运行时会生成一个特殊的层(通常叫

-

处理DRC错误:

- 根据报告定位每一个错误点。

- 理解违反的具体规则要求。

- 修改你的版图设计以符合规则要求(例如:拉开间距、加大包围、加宽导线、添加接触孔等)。

- 修改后必须重新运行DRC,直到报告显示

Total Errors = 0并且Rules Violated = 0。

关键要点总结:

- 坐标 (X, Y) 是你的“地图坐标”,用它找到版图中的错误点。

- 规则名称/编号 是你的“规则手册条目”,用它理解违反了什么。

- 错误描述 是“规则条款”,清楚说明具体要求是什么。

- 错误数量 告诉你问题的严重程度。优先解决数量多的错误类型。

- 目标是

0 Errors和0 Violations。

请提供你遇到的DRC报告片段或截图(删除敏感信息),我可以帮你解读具体的规则名称、错误描述和建议的修改方向。 例如,告诉我报告里写着类似 METAL1.S.1: spacing < 0.1um at (100.0, 200.0) 这样的信息。

芯片后端设计的DRC是什么?

DRC的全称为design rule check,也就是设计规则检查。广义上DRC会包含很多分类,只要是设计规则广义上都可以成为DRC。

2023-12-04 13:55:16

基于Cadence软件DRACULA工具的DRC检查

基于Cadence软件DRACULA工具的DRC检查(ups电源技术维修)-该文档为基于Cadence软件DRACULA工具的

资料下载

![]() 张涛

2021-09-27 15:25:26

张涛

2021-09-27 15:25:26

怎么自动加载Cadence Toolbox功能组件

Symbol Edit... 快速编辑封装25.[Tools] Z-DRC...跨层DRC检查26.[Tools] PCB Design Compare...brd板间对比 27.[Tools] Padstack

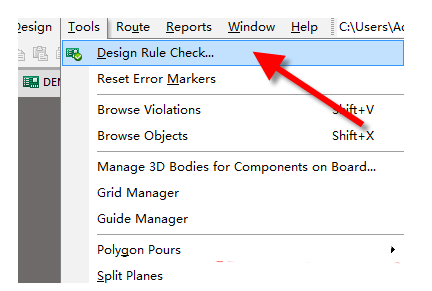

Altium designer对DRC的常规检查

Create Report File 执行完DRC之后,Altium会创建一个关于规则检查的报告,对报错信息会给出详细的描述并会给出报错的位置信息,方便我们设计者对报错信息进行解读。

2020-10-06 17:49:00

Altium:DRC检查 report_drc.xsl不存在报错的解决方法

使用AD进行PCB——DRC检查时,报告未生成,软件提示...report_drc.xsl don't exist。出现此种报错的原因大致的有以

如何使用签核DRC引擎来执行版图设计的所有检查

定制化设计工具包含多种内建DRC工具,辅助版图工程师放上多边形。在这些“工具内”DRC检查程序里最著名的是Cadence的DIVA工具,但所有的

2019-09-19 14:29:00

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览