FPGA PID 代码

以下是一个简单的 FPGA PID 控制器实现代码(Verilog HDL)。该代码实现了离散位置式 PID 控制算法,包含积分抗饱和和输出限幅功能:

module PID_Controller (

input clk, // 时钟信号 (50MHz)

input rst_n, // 复位信号 (低有效)

input signed [15:0] setpoint, // 16位设定值

input signed [15:0] feedback, // 16位反馈值

output reg signed [15:0] output // 16位控制输出

);

// PID 参数(使用 Q16.15 定点数格式)

parameter KP = 16'h2000; // Kp = 2.0 (0x2000 = 8192/16384)

parameter KI = 16'h0800; // Ki = 0.5 (0x0800 = 2048/16384)

parameter KD = 16'h0500; // Kd = 1.25 (0x0500 = 1280/16384)

// 运算中间量(扩展位宽防止溢出)

reg signed [31:0] integral; // 积分项

reg signed [15:0] prev_error; // 上次误差

reg signed [31:0] p_term, i_term, d_term;

// 输出限幅参数

parameter OUT_MAX = 16'h7FFF; // 最大输出值 (32767)

parameter OUT_MIN = 16'h8000; // 最小输出值 (-32768)

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin // 复位初始化

integral <= 0;

prev_error <= 0;

output <= 0;

end

else begin

// 计算误差

wire signed [15:0] error = setpoint - feedback;

// P项计算

p_term = KP * error; // 比例项

// I项计算(带抗饱和)

if (output < OUT_MAX && output > OUT_MIN) begin

integral <= integral + (KI * error);

end

i_term = integral; // 积分项

// D项计算

d_term = KD * (error - prev_error); // 微分项

prev_error <= error;

// PID求和(右移15位还原Q16.15)

wire signed [31:0] pid_sum = p_term + i_term + d_term;

wire signed [15:0] pid_out = pid_sum[30:15]; // 等效除以16384

// 输出限幅

output <= (pid_out > OUT_MAX) ? OUT_MAX :

(pid_out < OUT_MIN) ? OUT_MIN : pid_out;

end

end

endmodule关键功能说明:

-

定点数运算:

- 使用 Q16.15 格式(16位整数 + 15位小数)

- 最终输出通过截取[30:15]位实现右移15位(除以32768)

-

抗积分饱和:

if (output < OUT_MAX && output > OUT_MIN) begin integral <= integral + (KI * error);当输出未饱和时,才进行积分累加

-

微分环节:

d_term = KD * (error - prev_error); // 微分项 -

输出限幅:

output <= (pid_out > OUT_MAX) ? OUT_MAX : (pid_out < OUT_MIN) ? OUT_MIN : pid_out;

使用注意事项:

-

参数整定:

- 需根据实际系统调整

KP、KI、KD参数 - 建议先用 MATLAB/Simulink 仿真验证参数

- 需根据实际系统调整

-

运算优化:

- 可根据需要添加饱和环节的积分复位(integral reset)

- 微分项可增加一阶低通滤波减少高频噪声

-

时钟要求:

- 采样频率应为被控系统带宽的10倍以上

- 例中使用50MHz时钟,实际频率需根据需求调整

-

接口扩展:

- 可增加参数在线调整接口

- 可添加手动/自动切换功能

调参建议:

- 先设定 Ki=0, Kd=0,逐步增大 Kp 至临界震荡

- 取临界震荡时 Kp 的50%~80%作为基础值

- 逐渐加入积分项消除稳态误差

- 最后加入微分项抑制超调

实际应用中需结合具体控制对象特性调整算法细节。复杂系统建议加入变参数 PID 或模糊 PID 等高级算法增强鲁棒性。

PID算法的代码实现

PID算法的代码实现 舵机控制 在对舵机的控制中,我采用的是位置式PD算法。 将左右电感的偏差值赋给error,再代入公式进行解算,最后传给舵机输出子函数,控制舵机正确打角。 void

2023-11-28 15:57:39

PID控制算法代码 PID控制算法的原理

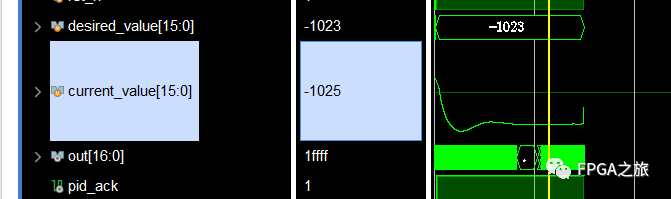

算法的原理,然后带大家使用FPGA来实现(C语言实现过程特别简单)。 二. PID算法 PID取自比例、积分、微分三个英文字母的首字母。意味着算

2023-07-20 09:23:12

FPGA实现PID控制算法

相信大家对于PID控制算法,都不感到陌生了,平衡车就是靠它平衡起来的,还有飞控的平衡算法也是它,以及FOC中的闭环控制中也是用的它,它不仅简单,而且易于理解。那么本篇文章将简要介绍一下算法的原理,然后带大家使用FPGA

2023-05-19 16:40:23

角度单环与串级PID伪代码资料下载

电子发烧友网为你提供角度单环与串级PID伪代码资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户

资料下载

![]() 佚名

2021-03-30 08:46:22

佚名

2021-03-30 08:46:22

EasyGo FPGA Solver

1970-01-01 08:00:00 至 1970-01-01 08:00:00

请问我们可以使用生成的代码在Zynq 7020 FPGA上实现设计吗?

我使用SIMULINK中的系统生成器设计了我的PID控制器浮点。我们可以使用生成的代码在Zynq 7020 FPGA上实现设计吗?或者我们需要在

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览