如何实现DRAM控制器的电路设计?

DRAM的结构可谓是简单高效,每一个bit只需要一个晶体管另加一个电容。但是电容不可避免的存在漏电现象,如果电荷不足会导致数据出错,因此电容必须被周期性的刷新(预充电),这也是DRAM的一大特点。

DRAM控制器的电路设计是一个复杂且涉及多层次的工程任务,旨在高效可靠地在处理器/SoC和动态随机存取存储器(DRAM)之间管理数据传输。以下是实现DRAM控制器电路设计的关键步骤和核心考虑因素:

核心目标和挑战:

- 时序满足: 严格遵守DRAM芯片(如DDR4, LPDDR4, DDR5)极其严格的时序要求(

tRCD,tRP,tRAS,tRTP,tWTR,CL,CWL,tRFC等)。 - 带宽最大化: 通过调度优化、突发传输、数据位宽扩展等方式充分利用DRAM接口带宽。

- 延迟最小化: 优化命令调度、流水线操作、降低访问冲突以减少访问延迟。

- 功耗管理: 实现低功耗状态(如自刷新、部分阵列自刷新、节能模式),优化刷新策略,降低活动功耗。

- 协议符合: 严格遵守对应的DRAM协议标准(如JEDEC规范)。

- 可靠性和纠错: 集成ECC以检测和纠正数据错误(尤其在服务器/企业级应用中)。

电路设计主要组件与流程:

-

前端接口:

- 功能: 连接处理器或片上总线(如AXI, AHB, OCP)。接收读写请求、地址、数据、控制信号。

- 设计要点:

- 定义清晰的接口协议。

- 地址映射:将系统地址转换为DRAM所需的Bank-Row-Column地址。通常由

地址映射逻辑完成。 - 请求缓冲区:缓存传入请求以实现调度优化。可能是FIFO或更复杂的带优先级队列结构。

- 原子操作处理(可选):支持CAS操作(如Atomic Add/Swap)。

-

后端接口 (PHY Interface - DFI标准):

- 功能: 连接物理层接口。发送精确时序的命令(ACT, RD, WR, PRE, REF等)、地址和数据,接收读回数据。

- 设计要点:

- 严格遵守DFI协议或类似标准。

- 精细的时序控制:使用状态机或专用逻辑严格产生符合要求的命令序列和时序间隔(满足所有

t*参数)。通常由命令调度器和时序控制逻辑实现。 - 数据通路(读/写):包含缓冲、对齐(考虑WL/BL)、可能的串并/并串转换(与PHY协作)。

- 读数据通路:捕获读数据、数据选通(DQS)对齐/训练(通常在PHY或通过校准逻辑完成)、可能的数据重排序。

-

核心控制逻辑 (命令调度器/仲裁器):

- 功能: 控制器的“大脑”。管理DRAM内部状态(哪些行激活、哪些Bank空闲),决定接下来发送哪个命令以优化性能、避免冲突、满足时序要求。

- 设计要点:

- Bank状态机: 为每个Bank维护状态(Precharged, Activated, Refreshing等)。

- 命令调度算法:

- 支持基础命令(Read, Write, Activate, Precharge, Refresh)。

- 关键算法:Bank开放策略(按需/预充电),行缓存策略(行命中优先)。

- 高级调度:实现算法如FR-FCFS(先来先服务,优先行命中请求),优化行缓存命中率以最大化带宽。

- 优先级仲裁:区分高优先级请求(如实时数据)和低优先级请求。

- 冲突避免: 确保命令不违反时序规则和Bank状态。

- 刷新管理:

- 计数器跟踪刷新周期。

刷新调度器:生成刷新命令(REF或REFpb)。可支持自刷新、部分阵列自刷新。- 调度策略:避免刷新导致高延迟,可与正常请求交错(如Refresh调度算法)。

- 时序管理单元: 跟踪每个Bank和命令的时序计数器(

counters/timers),确保命令仅在满足所有t*要求后才能发出。通常实现为一组独立的计数器或状态机,监控Bank上次操作时间。 - 功耗管理单元: 控制进入/退出低功耗模式,管理片内终结(ODT)。

-

数据路径与缓冲:

- 写缓冲区: 缓存待写入DRAM的数据。

- 读缓冲区: 缓存从DRAM读取的数据,在数据完整前不会送回给前端。

- 缓冲管理: 管理缓冲区的分配与释放,确保数据一致性和有序性(如果协议要求)。

- 数据宽度转换: 协调前端和后端(PHY)可能不同的数据位宽。

-

纠错码 (ECC):

- 功能: 检测和纠正数据位错误(单比特错误纠正,双比特错误检测)。

- 设计要点:

ECC编码器:在写数据时生成校验位。ECC解码器:在读数据时使用校验位检测和纠正错误。- 集成在数据路径中(通常写数据时加编码,读数据后解码纠错)。

- 额外DRAM空间存储校验位(通常每64位数据加8位ECC)。

-

校准与训练逻辑:

- 功能: 在初始化或环境变化时动态调整PHY参数,补偿PVT变化。

- 设计要点:

- 读训练: 动态调整读采样的时钟相位(针对DQS)。

- 写训练: 动态调整写数据的输出相位(针对DQS/DQ)。

- 命令/地址训练: 优化CA输出时序。

- 片内终结校准: 校准片上终结电阻值。

设计流程:

- 规格定义: 明确定义支持哪种DRAM类型(DDR4/5, LPDDR4/5)、速率、容量、总线位宽、特性(ECC?低功耗模式?)、接口协议(AXI? DFI版本?)。

- 架构设计: 定义控制器模块划分、主要状态机、调度策略、关键流水线级、缓冲区大小、时钟域划分(通常多个时钟域:前端、核心逻辑、PHY接口)。

- RTL实现:

- 使用HDL(Verilog/VHDL)编码。

- 详细设计并实现:前端接口、地址映射、请求缓冲、命令调度器、仲裁器、Bank状态机、时序控制逻辑(计数器/FSM)、刷新逻辑、数据缓冲、ECC逻辑(如果需要)、功耗控制逻辑。

- 功能验证:

- 搭建强大的测试平台(Testbench),模拟前端请求和DRAM行为模型(PHY模型)。

- 编写测试用例:覆盖所有命令、时序场景、冲突、刷新、边界情况、错误注入(如ECC)。

- 使用形式化验证检查关键协议符合性。

- 目标:达到接近100%的状态机/状态覆盖和时序弧覆盖。

- 时序分析与收敛:

- 执行静态时序分析。

- 优化关键路径以满足目标时钟频率。

- 管理跨时钟域信号(CDC),进行充分验证。

- 物理实现:

- 逻辑综合。

- 布局布线。

- 签核验证:时序签核、功耗签核、物理规则检查。

- PHY协同设计与验证:

- 控制器和PHY作为一个整体进行验证。

- 重点验证DFI接口时序和功能、读/写数据路径、训练序列。

- 系统级验证与测试:

- 集成到SoC或与处理器配合测试。

- 实际搭载DRAM芯片进行板级或芯片级测试。

- 性能测量、压力测试、功耗测试、兼容性测试。

工具与技术:

- EDA工具: HDL仿真器(VCS, NC-Verilog, ModelSim/QuestaSim),波形查看器(Verdi, DVE),逻辑综合工具(Design Compiler, Genus),布局布线工具(Innovus, ICC2),时序分析工具(PrimeTime),形式验证工具(JasperGold, VC Formal)。

- 仿真模型: PHY行为模型、DRAM行为模型(常用的是来自Synopsys的

VIP或开源模型)。 - 高级语言: SystemVerilog(广泛用于验证)和SystemC/TLM(用于早期架构探索)也很常用。

总结:

DRAM控制器是SoC内存子系统的关键且复杂的组成部分。其设计涉及深入理解DRAM协议细节、高性能调度算法、精确的时序管理、数据通路设计以及现代设计方法学和验证技术。它本质上是高速数字逻辑、状态机控制以及对物理层接口约束的复杂结合。整个流程需要严格的验证和协同设计(尤其是与PHY)。

怎么实现基于业界首款Cortex-M33双核微控制器LPC55S69的电路设计?

怎么实现基于业界首款Cortex-M33双核微控制器LPC55S69的电路设计?

60KW电机控制器硬件驱动电路设计(可下载)

摘 要:设计一款 60KW 的电机驱动控制器,产品的功能、性能及成本等都能达到客户的需求,还要在市场上有竞争力。根据客户要求再开发一款中型物流车车用电机 控制器,该

资料下载

![]() 松山归人

2025-03-07 14:34:33

松山归人

2025-03-07 14:34:33

实现基于FPGA的SPIFlash控制器设计

实现基于FPGA的SPIFlash控制器设计(嵌入式开发工作怎么样)-该文档为实现基于FPGA的SPIFlash

资料下载

![]() 佚名

2021-07-30 09:10:17

佚名

2021-07-30 09:10:17

求一种DRAM控制器的设计方案

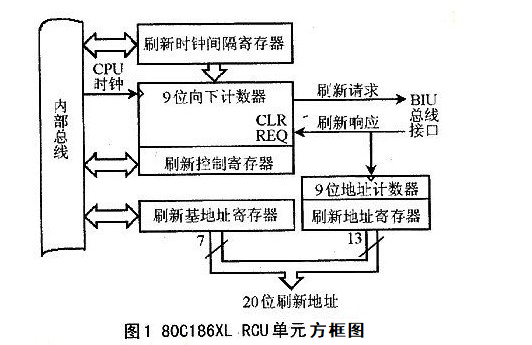

本文介绍了怎样在嵌入式CPU 80C186XL DRAM刷新控制单元的基础上,利用CPLD技术和80C196XL的时序特征设计一个低价格、功能完整的DRAM

基于VHDL语言和可编程逻辑器件实现Petri网逻辑控制器的设计

VHDL语言由于其其强大的行为描述能力及与硬件行为无关的特性,被广泛的用于数字系统设计,实现了硬件电路设计的软件化,成为实现Petri网逻辑

2020-09-22 20:46:51

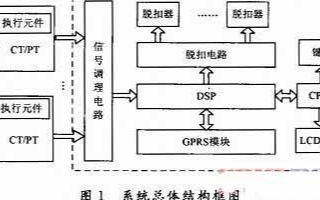

基于DSP和CPLD EPM3128芯片实现智能控制器的电路设计

群组智能控制器的核心采用DSP TMS320F2812芯片,辅以CPLD EPM3128芯片来实现键盘和液晶的时序逻辑,减少扩展芯片带来的体积问题,外围电路

2020-09-07 17:52:00

如何获得配置PS DRAM控制器(DDRC)板的参数?

嗨,我已经搜索了很多关于配置PS DRAM控制器(DDRC)板参数的信息,链接如下,http://www.xilinx.com/support/answers/46778.htm, 我想知道如何获得包装长度?谢谢!

基于80C186XL和CPLD怎么实现DRAM控制器?

控制单元。RCU单元可以自动产生DRAM刷新总线周期,它工作于微处理器的增益模式下。经适当编程后,RCU将向将处理

基于嵌入式系统中DRAM控制器该怎么设计?

80C186XL16位嵌入式微处理器是Intel公司在嵌入式微处理器市场的上导产品之一,已广泛应用于电脑终端、程控交换和工控等领域。在该嵌入式微处理器

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 芯片的工作原理是什么?

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- 苹果手机哪几个支持无线充电的?

- dtmb信号覆盖城市查询

- 怎样挑选路由器?

- 华为芯片为什么受制于美国?

- 元宇宙概念股龙头一览

- type-c四根线接法图解

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 传感器常见类型有哪些?

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览