Nios II的设计过程及如何构建其开发环境?

Nios Ⅱ处理器支持 Nios Ⅱ处理器支持页面提供了对Nios Ⅱ 设计者有帮助的多种信息,其中包括使用许可、下载、参考设计、文档资料、在线展示及常见问题。

以下是Nios II软核处理器的设计过程及开发环境构建的详细步骤(中文版):

一、Nios II 设计流程

1. 硬件设计(在Quartus中完成)

- 步骤1:创建Qsys系统

- 在Quartus中打开Platform Designer (旧版Qsys)

- 添加Nios II处理器核(根据需求选型):

- Nios II/e(最小资源,低性能)

- Nios II/s(平衡型)

- Nios II/f(高性能,带缓存)

- 关键组件配置:

- 指令/数据缓存大小

- 乘法器、硬件除法器等加速单元

- 复位/异常向量地址(指向片上存储器或SDRAM)

- 步骤2:添加外设接口

- 内存:On-Chip RAM/ROM、SDRAM控制器、QSPI Flash控制器

- 通信:UART、SPI、I²C、Ethernet MAC

- 通用:PIO(按键/LED)、定时器、DMA控制器

- 总线连接:所有外设通过Avalon-MM/Avalon-ST总线互联

- 步骤3:生成系统

- 设置基地址和中断号(自动分配)

- 点击 Generate HDL 生成系统描述文件(

.sopcinfo) - 在Quartus顶层例化生成的Qsys模块

2. FPGA工程集成

- 在Quartus中编译整个设计:

- 分配FPGA引脚约束(

.qsf) - 时序约束(

.sdc) - 生成FPGA编程文件(

.sof)

- 分配FPGA引脚约束(

3. 软件设计(在Nios II Software Build Tools for Eclipse中完成)

- 步骤1:创建BSP(Board Support Package)

- 使用

nios2-bsp命令生成BSP模板:nios2-bsp hal <bsp_dir> <sopc_file>.sopcinfo - 配置BSP:

- 内存分配(

system.h中的内存区域) - 标准I/O设备(指定UART作为

stdout) - 中断优先级

- 使用

-

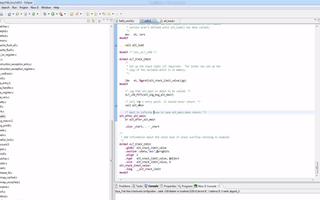

步骤2:编写应用程序

- 在Eclipse中创建Nios II工程:

- 选择Altera Nios II Application and BSP模板

- 关联步骤1生成的BSP

- 代码示例(控制LED):

#include "system.h" #include "altera_avalon_pio_regs.h"

int main() { while (1) { // PIO基地址在system.h中定义 IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE, 0xFF); // LED全亮 usleep(500000); // 延时500ms IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE, 0x00); // LED全灭 } }

- 步骤3:编译与链接

- 使用

Makefile自动调用nios2-elf-gcc编译为ELF文件

- 使用

二、开发环境搭建

1. 必备软件

| 工具 | 版本 | 功能 |

|---|---|---|

| Quartus Prime | ≥18.1 | FPGA综合/布局布线 |

| Nios II Software Build Tools (EDS) | 与Quartus匹配 | 包含编译器、调试器、Eclipse插件 |

| FPGA开发板支持包 | 板商提供 | 板级初始化代码 |

2. 安装步骤

-

安装Quartus Prime

- 从Intel官网下载Standard/Pro版

- 必选组件:Quartus、Device Support(如Cyclone V)、Nios II EDS

-

安装Nios II EDS

- 包含在Quartus安装包中,勾选 Nios II Software Build Tools

- 安装后配置环境变量(通常自动完成):

# 检查路径(Linux示例) export PATH=$PATH:/opt/intelFPGA/20.1/nios2eds/bin

-

启动开发环境

- 硬件设计:Quartus → Platform Designer

- 软件开发:

# 启动Eclipse nios2-eclipse & - 配置BSP生成器路径:

nios2-bsp-generate-files --settings=<bsp_dir>/settings.bsp

三、下载调试流程

-

配置FPGA

- 使用Quartus Programmer烧写

.sof到FPGA - 开发板电源/下载线(USB-Blaster II)连接

- 使用Quartus Programmer烧写

-

软件调试

- 在线调试:

- 在Eclipse中右键工程 → Debug As → Nios II Hardware

- 自动通过JTAG-UART连接目标板

- 独立运行:

# 将ELF文件转为Flash格式 nios2-elf-objcopy -I elf32-little -O srec app.elf app.srec # 使用Flash Programmer烧写至板载Flash

- 在线调试:

四、关键注意事项

-

内存空间冲突

- 在

Platform Designer中确认外设地址无重叠 - 检查BSP的

linker.x脚本是否匹配硬件地址

- 在

-

中断处理优化

- 中断服务函数需短小,避免阻塞

- 使用

alt_ic_isr_register()注册中断处理例程

-

性能调优

- 启用指令缓存(Nios II/f)

- DMA代替CPU搬运数据

- 关键代码使用汇编优化(

.S文件)

五、排错指南

| 问题现象 | 解决方案 |

|---|---|

程序卡在alt_main |

检查复位向量是否指向有效内存 |

printf无输出 |

在BSP中指定正确的UART基地址 |

| 链接失败 | 调整.ld文件中内存区域大小匹配硬件 |

| JTAG识别失败 | 重启jtagd服务:jtagconfig |

⚠️ 推荐实践:

首次开发时选择Cyclone IV/V等常用FPGA型号,使用Intel提供的参考设计(如DE10-Lite板)快速验证流程。

通过以上步骤,可完整实现从硬件搭建到软件开发的Nios II系统构建。整个过程依赖Quartus与Eclipse的协同操作,重点在于硬件/软件接口(system.h)的一致性验证。

QuartusⅡ10.1中NIOS2软核的构建方法

)DDR2 SDRAM模块的构建(2)On-Chip RAM模块的构建(3)SRAM模块的构建(4)软核的生成和引脚的分配 二、软件

基于Nios II的hello world相关资料分享

目录一、基于Nios II的hello world1、NiosII实现hello world1.1硬件设计1.2软件设计1.3下载硬件和软件一、基于Nios

关于QuartusⅡ10.1中NIOS2软核的构建、软件编译及程序固化

)DDR2 SDRAM模块的构建(2)On-Chip RAM模块的构建(3)SRAM模块的构建(4)软核的生成和引脚的分配 二、软件

资料下载

![]() 从未拥有

2021-11-30 18:06:04

从未拥有

2021-11-30 18:06:04

如何制作一个方便在Quartus II和Nios II中使用的简单IP

本文档的主要内容详细介绍的是如何制作一个方便在Quartus II和Nios II中使用的简单IP。

资料下载

![]() 佚名

2019-07-09 17:40:00

佚名

2019-07-09 17:40:00

FPGA视频教程之NIOS II开发流程的详细资料说明

本文档的主要内容详细介绍的是FPGA视频教程之NIOS II开发流程的详细资料说明主要目的是:1.完整的嵌入式

资料下载

佚名

2019-03-22 13:59:55

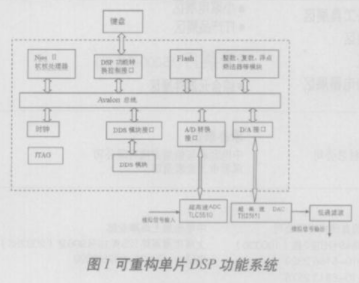

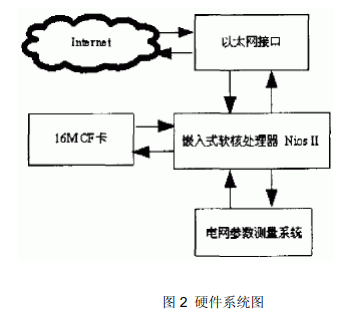

基于Nios II和uClinux实现远程测控服务器的设计

系统的硬件结构如图2所示。硬件系统的核心是构建于Ahera Cyclone FPGA中的Nios II嵌入式软核处理器。

2020-06-28 14:49:45

NIOS II SOPC开发少走弯路的技巧

1、保证EPCS FLASH中没有任何与NIOS II相关的固件,可以通过擦除EPCS存储器的方法实现。为啥要擦除,如果EPCS里面存储有与NIOS

锆石FPGA A4_Nano开发板视频:NiOS II硬件框架结构深入剖析2

Nios II系列软核处理器是Altera的第二代FPGA嵌入式处理器,其性能超过200DMIPS,在Altera FPGA中实现仅需35美分。

2019-09-26 07:00:00

锆石FPGA A4_Nano开发板视频:NiOS II硬件框架结构深入剖析(2)

Nios II系列软核处理器是Altera的第二代FPGA嵌入式处理器,其性能超过200DMIPS,在Altera FPGA中实现仅需35美分。

2019-09-25 07:09:00

采用Nios II软核处理器实现SD卡接口设计

的硬件电路SD卡采用SPI总线方式与处理器连接,其电路原理如图2所示。图2 SD 卡接口电路图1.5 NiosII的构建过程首先要考虑到的是使用

基于Nios II的MCU接口方式的指纹采集系统

的身份证。指纹图像的采集技术是指纹识别系统中的关键技术之一[2],在指纹识别系统中具有非常关键的作用,altera公司提供的Nios II是一种软核处理器,用于可编程逻辑器件的

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 芯片的工作原理是什么?

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- dtmb信号覆盖城市查询

- 怎样挑选路由器?

- 华为芯片为什么受制于美国?

- 元宇宙概念股龙头一览

- type-c四根线接法图解

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- BLDC电机技术分析

- 复位电路的原理及作用

- dsp是什么意思?有什么作用?

- iphone13promax电池容量是多少毫安

- 苹果无线充电器怎么使用?

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 传感器常见类型有哪些?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机