采用FPGA器件如何实现模糊PID控制器的设计?步骤与方法分析

PID控制器可以用来控制任何可以被测量的并且可以被控制的变量。比如,它可以用来控制温度,压强,流量,化学成分,速度等等。

更多

采用FPGA实现模糊PID控制器设计的关键在于充分利用FPGA的并行处理能力、硬件可编程性以及低延迟特性。以下是详细的步骤与方法分析:

核心步骤与方法

-

系统需求分析与架构规划

- 明确指标:确定控制对象特性、输入输出范围、控制精度(如误差位数)、采样频率、实时性要求(计算延迟)。

- 选择模糊PID结构:

- 参数自整定型:模糊规则实时调整Kp, Ki, Kd参数(最常用)。

- 直接输出型:模糊控制器替代PID,输出直接为控制量(较少见)。

- 定义模块划分:

- 模糊化模块

- 规则库与推理模块

- 解模糊化模块

- 核心PID计算模块

- 参数调整模块(用于参数自整定型)

- 接口模块(ADC/DAC、通信接口等)

- 时序控制模块(同步协调各模块)

- 数据表示:选择定点数格式(如Q格式)代替浮点数,以节省资源、提高速度。确定整数位和小数位宽。

-

模糊控制器设计(核心算法)

- 确定输入/输出变量:

- 输入:误差

e= 设定值 - 反馈值,误差变化率ec= de/dt(通常用差分近似)。 - 输出(参数自整定型):ΔKp, ΔKi, ΔKd 或最终参数 Kp, Ki, Kd。

- 输入:误差

- 定义隶属函数(MF):

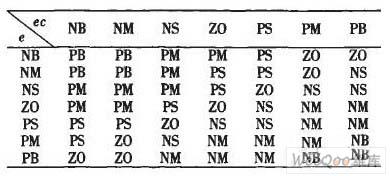

- 语言值:负大(NB)、负中(NM)、负小(NS)、零(ZO)、正小(PS)、正中(PM)、正大(PB)等。

- 形状:常用三角形或梯形(易于硬件实现)。

- 量化因子:将物理量[-Range, +Range]映射到离散论域[-n, +n](如-7到7)。

- FPGA实现:用LUT (查找表) 存储预计算的隶属度值。将输入离散化作为地址,输出对应MF的隶属度(多比特宽)。

- 建立模糊规则库:

- 形式:IF

eis A ANDecis B THENoutputis C。 - 知识来源:经验、仿真或自学习。

- FPGA存储:用双端口ROM或分布式RAM存储规则。

(e, ec)的组合作为地址索引(或部分地址),输出为目标语言值的组合信息(如权值向量或输出MF索引)。

- 形式:IF

- 选择推理方法:

- Mamdani型(更直观,输出也是模糊集):常用

MIN-MAX或乘积算子进行与、或运算。 - FPGA优化:

MIN/MAX本质为比较器链;乘积用硬件乘法器。规则激活度计算(如 min(μe, μec))可并行进行。

- Mamdani型(更直观,输出也是模糊集):常用

- 解模糊方法:

- 重心法(COG):精度高但计算复杂(需积分)。

- 加权平均法:常用、硬件友好。

COG ≈ Σ(μ_i * Center_i) / Σμ_i。 - FPGA优化:

- 预计算COG值:对输出MF离散点预先计算其重心,存储在ROM中(近似法)。

- 重心法直接计算:用累加器(ACC)和除法器实现积分和除法(资源消耗较大)。

- 最大值法/中心法:简单但精度略低(硬件极易实现)。

- 确定输入/输出变量:

-

PID计算模块设计

- 离散化模型:采用位置式或增量式PID。

- 位置式:u[k] = Kpe[k] + KiΣe[j] + Kd*(e[k] - e[k-1])

- 增量式:Δu[k] = Kp(e[k]-e[k-1]) + Kie[k] + Kd*(e[k] - 2e[k-1] + e[k-2]) (更常用,抗积分饱和、易无扰切换)。

- FPGA实现:

- 移位寄存器:存储历史误差数据

e[k-1],e[k-2]。 - 乘法器:与参数相乘(注意定点数位宽和溢出处理)。

- 加法器/累加器:求和及积分累加(带饱和限制,防止Windup)。

- 数字滤波:可在微分项后加一阶低通滤波器抑制噪声。

- 移位寄存器:存储历史误差数据

- 离散化模型:采用位置式或增量式PID。

-

参数调整模块(参数自整定型)

- 接口:接收来自解模糊化模块的ΔKp, ΔKi, ΔKd或新的Kp, Ki, Kd。

- 实现:

Kp_new = Kp_base + ΔKp(类似处理 Ki, Kd)。- 包含限幅功能,保证参数在合理范围。

- 实时性:此模块需在每次模糊推理完成后、下一个PID计算前更新参数。

-

整体数据流与时序设计

- 流水线设计:将整个计算过程划分为多个阶段(如模糊化、规则评估、解模糊、PID计算、输出),每一时钟周期处理不同数据样本,提高吞吐率。

- 状态机控制:设计一个状态机来精确控制每个模块的启动、运算完成、数据传输和同步。常见的操作流程:

- ADC采样完成,读入

r(k)和y(k)。 - 计算

e(k)=r(k) - y(k)。 - 计算

ec(k)≈ (e(k) - e(k-1)) /Ts(或直接差分e(k) - e(k-1))。 - 模糊化模块并行计算

e和ec对各MF的隶属度。 - 规则推理模块并行评估所有规则,生成各输出MF的激活强度。

- 解模糊模块融合激活强度,计算清晰输出值(ΔKp, ΔKi, ΔKd 或 PID输出)。

- 参数自整定型:参数调整模块更新PID参数。

- PID计算模块利用当前误差、历史数据和(可能更新后的)参数计算控制量

u(k)。 - 将

u(k)通过DAC输出(或转换为PWM信号)。 - 更新历史数据寄存器:

e(k-2) = e(k-1),e(k-1) = e(k)。

- ADC采样完成,读入

- 时钟策略:根据采样频率要求,确定系统主时钟频率。确保最慢模块在单个采样周期Ts内完成计算。

-

硬件描述语言编码与模块化实现

- 语言选择:Verilog HDL 或 VHDL。

- 模块化实现:按前述规划,分别编写清晰接口的功能模块:

fuzzify.vhd/defuzzify.vhdfuzzy_rule_engine.vhd/fuzzy_inference.vhdpid_core.vhdparam_adjuster.vhd(如果采用)top_fuzzy_pid.vhd(顶层,实例化并连接所有模块、时钟、复位逻辑)

- 接口设计:明确定义输入输出端口(数据线、控制信号、时钟、复位)。

- 资源优化:

- 共享乘法器/除法器(如果资源紧张且频率允许)。

- 采用DSP Slice:调用FPGA内置的硬核乘法器/累加器单元。

- 位宽优化:仔细分析各运算所需的位宽,避免不必要的宽位。

- 分布式RAM/块RAM:高效存储隶属函数LUT和规则库。

- 流水线:在关键路径(如复杂的加法链、除法器)中插入寄存器级,以提高系统时钟频率。

-

仿真验证与调试

- 单元仿真:使用HDL测试平台(

testbench)对每个子模块进行独立仿真,验证其功能正确性。生成激励信号(如阶跃、斜坡),观察输出波形。 - 系统仿真:对整个模糊PID控制器Top进行闭环/开环仿真。使用数值模型或导入实际控制对象模型数据。

- 调试工具:使用Xilinx Vivado / Intel Quartus 内置的逻辑分析仪(如ILA/VIO for Xilinx, SignalTap for Intel)在真实FPGA上抓取内部信号调试。

- 定点数精度验证:对比软件浮点仿真结果,确保定点化精度满足要求。

- 单元仿真:使用HDL测试平台(

-

综合、布局布线、时序约束

- 时序约束:在工具中设置时钟频率约束(例如:

create_clock -name sys_clk -period 20 [get_ports clk])。 - 管脚约束:绑定ADC、DAC、PWM、通信等实际物理管脚。

- 综合与实现:运行工具链,分析报告:

- 资源报告:LUTs、FFs、DSPs、Block RAM的用量是否在目标器件范围内?

- 时序报告:是否满足设置时钟频率?(检查Setup/Hold时间是否违例)

- 优化迭代:若时序违例,调整流水线结构、优化组合逻辑、或放宽位宽;若资源超限,考虑减少MF数量/规则数、采用更简单的解模糊方法。

- 时序约束:在工具中设置时钟频率约束(例如:

-

板级测试与闭环验证

- 开环测试:验证ADC、DAC转换正确,FPGA输出控制信号符合预期。

- 软件开环对比:将FPGA计算结果与PC端模糊PID算法(如Matlab/Simulink)结果对比。

- 闭环验证:连接实际控制对象(电机、温控装置等),施加设定值变化,观察系统响应动态性能(超调量、调节时间、稳态误差)。

- 在线调参:可增加UART/Ethernet等接口连接上位机,实时观察内部状态(如当前e, ec, Kp, Ki, Kd, u)并在线微调量化因子或规则库。

核心优势与注意事项

- 优势:

- 高速、低延迟、确定性:并行处理远快于软件方案。

- 高可靠性:硬件固化,不受软件任务切换影响。

- 可重构性:方便更改规则或MF而不重新设计电路板。

- 单片集成:可与ADC、PWM、通信接口等集成在同一芯片。

- 注意事项/挑战:

- 开发复杂度高:需要深厚的数字电路和HDL设计能力。

- 调试难度:观察内部信号比软件调试更困难。

- 精度与资源平衡:定点运算精度需仔细设计。

- 规则库/MF复杂度限制:过复杂的模糊系统会消耗大量资源。

- 初始设计时间:对于简单应用,可能不如成熟MCU快速。

通过严谨地按照上述步骤,利用FPGA强大的并行处理能力和硬件灵活性,可以构建出高性能、高可靠性、实时性优异的模糊PID控制器,尤其适合于高速运动控制、精密仪器、噪声环境等要求苛刻的应用场景。

7天热门专题

换一换

换一换

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 芯片的工作原理是什么?

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- dtmb信号覆盖城市查询

- 怎样挑选路由器?

- 华为芯片为什么受制于美国?

- 元宇宙概念股龙头一览

- type-c四根线接法图解

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- BLDC电机技术分析

- 复位电路的原理及作用

- dsp是什么意思?有什么作用?

- iphone13promax电池容量是多少毫安

- 苹果无线充电器怎么使用?

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 传感器常见类型有哪些?

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机