cpu和存储器之间FIFO

在计算机系统中,CPU 与存储器之间使用 FIFO(先进先出队列) 主要解决速度匹配和时序协调问题,尤其在高速数据传输和异步时钟域场景下。以下是其核心作用及工作原理:

核心作用

-

缓冲速率差异

- CPU处理速度 >> 存储器访问速度(如DRAM延迟高、Flash写入慢)。

- FIFO作为临时缓冲区:CPU可快速写入数据后立即执行后续指令,存储器则按自身速率从FIFO读取数据,避免CPU空等。

-

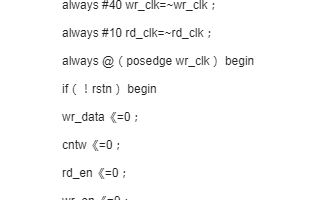

异步时钟域隔离

- CPU与存储器常工作在不同时钟频率(如CPU主频2GHz vs DDR内存控制器1.2GHz)。

- FIFO通过双端口结构(独立读写时钟)实现跨时钟域数据同步,避免亚稳态风险。

-

突发数据传输优化

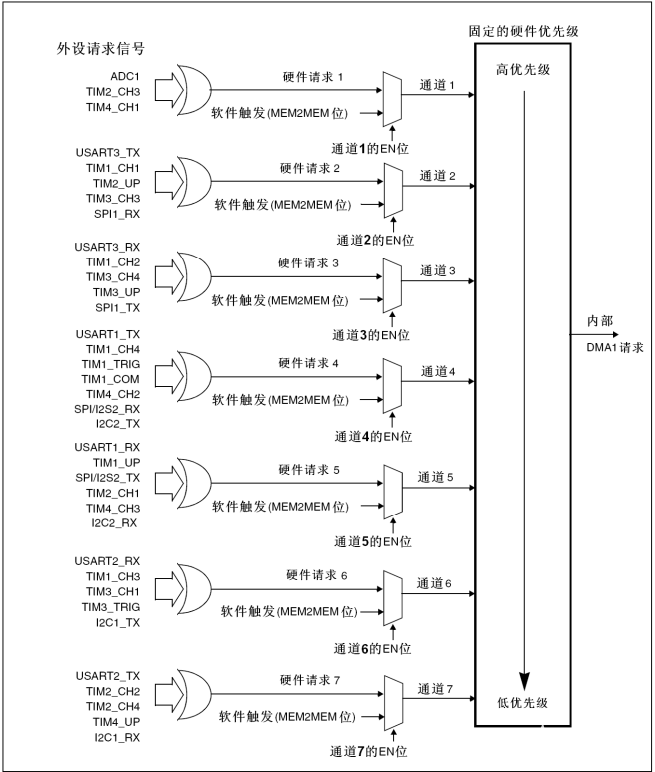

- CPU可能突发写入大量数据(如DMA传输)。

- FIFO缓存突发数据,平滑输出至存储器,避免带宽浪费或数据丢失。

-

降低访问冲突

- 当多个核心/外设竞争存储器时,FIFO可暂时缓存请求,仲裁逻辑按序处理。

典型实现场景

| 场景 | 说明 |

|---|---|

| CPU → 内存写操作 | CPU连续写入数据时,FIFO暂存数据,内存控制器按页/行策略高效写入DRAM。 |

| 高速缓存行填充 | Cache未命中时,存储器通过FIFO将整块数据流式传输至CPU,减少等待延迟。 |

| 外设DMA传输 | DMA控制器将外设数据写入FIFO,CPU异步读取,避免轮询阻塞(如网卡收包)。 |

| GPU显存接口 | GPU核心与GDDR显存间用大深度FIFO吸收渲染流水线的突发写入压力。 |

硬件结构示例

CPU侧 存储器侧

+-----+ 写入数据/时钟 +--------------+

| | ------------------> | FIFO写指针 |

| CPU | | 缓冲区RAM |

| | <------------------ | FIFO读指针 |

+-----+ 读请求/状态信号 +--------------+

|

v

存储器控制器(DDR, Flash等)- 同步机制:读写指针使用格雷码(Gray Code)编码,确保跨时钟域同步时仅1比特变化,消除亚稳态。

- 状态信号:FIFO提供

空(empty)/满(full)标志位,防止溢出或读空。

设计挑战

-

深度计算

FIFO深度需满足:最大突发数据量 × (CPU速率/存储器速率),否则可能溢出。

示例:CPU突发写入128字节,存储器延迟100ns,CPU频率2GHz → 最小深度=128×(2e9×100e-9)=256字节。 -

功耗与面积

大深度FIFO占用片上SRAM资源,在嵌入式系统中需权衡性能与成本。 -

一致性保障

若缓存数据未写入存储器前系统崩溃,需硬件机制(如写回策略)确保数据安全。

关键技术演进

- AMBA AXI总线协议:使用

AXI FIFO接口管理读写通道的握手机制(VALID/READY)。 - 弹性缓冲区(Elastic Buffer):在FPGA中用于动态调整时钟偏差,确保数据传输连续性。

- 存储级内存(SCM):新型存储器(如Intel Optane)降低延迟,减少FIFO依赖,但未完全淘汰。

总结

FIFO在CPU与存储器间扮演智能缓冲器角色,核心价值是解耦生产与消费速率。其设计直接影响系统性能上限(如最大吞吐量、最低延迟),尤其在异构计算与高并发场景下不可或缺。现代处理器通过集成多级FIFO(如队列缓存、内存控制器预取缓冲)进一步优化数据流效率。

高速缓冲存储器是内存还是外存,高速缓冲存储器是为了解决什么

高速缓冲存储器(Cache)是内存的一种特殊形式,但它与通常所说的主存储器(RAM)有所不同。在计算机存储体系中,Cache位于

2025-01-29 11:48:00

TMS320C67系列DSP的EMIF与异步FIFO存储器的接口设计详细资料介绍

介绍了TI公司TMS320C67系列DSP的EMIF(外部存储器接口)与异步FIFO(先进先出)存储器的硬件接口设计,着重描述了用EDMA(扩展

资料下载

佚名

2019-07-31 16:40:47

CPU对存储器的读写

汇编语言程序目录一、CPU对存储器的读写二、内存地址空间三、将各类存储器看作一个逻辑器件——统一编址四、内存地址空间的分配方案——以8086PC

一种基于FPGA内部存储器的适合音频解嵌的高效异步FIFO设计

异步FIFO存储器是一种在数据交互系统中得到广泛应用的先进先出逻辑器件,具有容纳异步信号的频率(或相位差异)的特点。使用异步FIFO可以在两个不

2020-01-29 16:54:00

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机