好的,PCB静电放电(ESD)防护设计是确保电子产品可靠性和耐用性的关键环节。以下是一个系统的PCB静电设计方案,涵盖关键原则和具体措施:

核心目标: 为ESD电流提供一条低阻抗、可控的泄放路径,绕过敏感电路,同时降低ESD耦合到信号线上的可能性。

一、 器件级防护 - 第一道防线

- 选择合适的ESD防护器件 (TVS二极管、ESD抑制器、压敏电阻等):

- 关键接口位置: 在所有外部连接器(USB, HDMI, RJ45, 按键, 开关, 指示灯, 电源输入/输出, 调试接口等)的信号线和电源线上放置防护器件。靠近连接器放置是关键!

- 器件选型:

- 钳位电压 (Vclamp): 必须低于被保护IC引脚的最大耐受电压(通常低于Absolute Maximum Rating 3-5V),并留有一定裕量。

- 工作电压 (Vrwm): 高于信号或电源的正常工作电压。

- 峰值脉冲电流 (Ipp): 根据目标ESD等级(如IEC 61000-4-2 Level 4, 8kV接触/15kV空气)选择合适的Ipp值(通常越大越好)。

- 电容 (Cj): 对于高速信号线(如USB, HDMI, MIPI),选择低电容(如<0.5pF甚至更低)的TVS二极管(如专门的低电容ESD保护阵列),避免信号完整性劣化(上升/下降时间变缓、信号衰减)。

- 响应速度: TVS二极管响应极快(纳秒级),优于压敏电阻。

- 封装: 根据电流和PCB空间选择合适的封装(如SOD-323, SOT-23, SOT-143, DFN, 多通道阵列等)。

- 敏感IC的选择:

- 优先选择本身具有较好ESD防护能力的IC(查看Datasheet中的HBM/CDM等级)。

- 对于非常敏感的器件(如射频前端、高速ADC/DAC),即使有外部保护,也需特别关注布局布线。

二、 PCB布局 - 构建低阻抗路径

- 建立坚固的参考平面 (最重要!):

- 完整地平面: 提供低阻抗返回路径。尽可能使用完整、连续的地平面(GND Plane)。

- 地分割与统一:

- 谨慎使用地分割。仅在绝对必要(如高隔离度模拟/数字部分、噪声极大的电机/继电器)时才分割地平面。

- 如果分割,必须在单一连接点(Star Point)或用合适参数的磁珠/0欧电阻桥接,确保ESD电流有低阻抗回流路径回源头(通常是连接器屏蔽壳或机壳地)。

- 机壳地 (Chassis GND/Shield GND) vs 信号地 (Signal GND): 如果产品有金属机壳或屏蔽层,需要定义一个独立的机壳地(通常连接到金属外壳)。机壳地与信号地应在靠近ESD注入点(如连接器)的位置,通过单个或多个高压电容(如1nF/2kV 0805陶瓷电容)和/或并联的高阻值电阻(如1MΩ)连接(形成高频低阻抗通路并联直流隔离)。绝对不能直接大面积相连! 对于塑料外壳,信号地即主要参考地。

- ESD防护器件的布局:

- 紧邻入口: TVS二极管等保护器件必须尽可能靠近其要保护的连接器引脚放置。

- 最小化引线电感:

- 缩短TVS管脚到被保护线和到地平面的走线。

- 优先使用表贴器件(SMD)。

- 使用最短、最宽的走线连接TVS到被保护信号线和地平面。

- 大面积过孔到地: TVS的地引脚必须通过多个、低电感的过孔(Via)直接连接到完整的地平面(通常是参考平面层),绝对不能只连到顶层或底层的局部铺铜。过孔数量越多、直径越大(或使用盘中孔)、越靠近器件引脚,阻抗越低。

- 信号线布线:

- 远离板边: 所有关键信号线(高速、模拟、复位、时钟)应远离PCB边缘至少3-5mm,减少耦合。

- 避免环路: 减小信号环路面积,降低磁场耦合。关键信号线与其回流路径(地平面)应尽量靠近(参考平面层邻近)。

- 关键差分对匹配: 高速差分对(USB, HDMI等)必须严格等长、等距、紧密耦合,并保持参考平面完整性(避免参考平面开槽)。

- 屏蔽(必要时): 对极端敏感或长距离布线,考虑使用同轴线或微带线加屏蔽层/屏蔽罩。

- 电源平面与去耦:

- 低阻抗电源分配网络 (PDN): 使用电源平面层或宽走线,配合足够的去耦电容。

- 电源入口保护: 在电源输入接口处添加TVS二极管(针对电源线)和/或压敏电阻进行防护。

- 去耦电容靠近IC: 每个IC电源引脚附近放置小容量陶瓷电容(0.1uF, 0.01uF) 提供高频瞬态电流通路。

- 大容量储能电容: 在电源入口或关键器件附近放置较大容量电解电容或钽电容(10uF, 100uF等),稳定电压。

三、 PCB布线 - 细节决定成败

- 地线/回流路径:

- 避免细长地线: 任何需要连接到参考地的点(电阻电容地端、IC地引脚、屏蔽罩焊盘)都应使用宽走线和多个过孔直接连接到地平面。

- 连接器地的处理: 连接器的接地引脚(尤其是屏蔽壳引脚)必须通过宽走线和多个过孔牢固地连接到参考地平面或机壳地。

- 过孔使用:

- 在需要低阻抗连接的地方(如TVS地、连接器地、IC电源/地焊盘、屏蔽罩焊盘)大量使用过孔。

- 优先使用小孔径、盘上孔(Via-in-Pad)或盘中孔技术进一步降低电感(成本允许的情况下)。

- 铺铜:

- 在PCB表层和底层无信号走线的区域进行铺铜,并通过大量过孔缝合到内部地平面(Stitching Vias),增强屏蔽效果并降低地阻抗。铺铜到板边的距离需考虑爬电距离(Creepage)要求。

- 爬电距离和电气间隙:

- 在高压或可能承受高压差的区域(如初级/次级隔离、TVS管脚间),确保满足安规要求的爬电距离和电气间隙。

四、 结构设计配合

- 接地柱/金属外壳连接:

- 如果产品有金属外壳,PCB上的机壳地必须通过低阻抗、低电感的方式(如金属弹簧指、导电泡棉、金属螺钉+星形垫圈)可靠连接到机壳。

- 连接点应靠近主要的ESD注入点(如连接器区域)。

- 屏蔽罩(Can Shield):

- 对特别敏感的电路区域(如RF、高速数字、模拟前端)使用金属屏蔽罩隔离。

- 屏蔽罩必须通过大量的焊盘和过孔(围绕屏蔽罩焊盘一圈)360度良好接地到PCB的参考地平面。

- 缝隙与孔洞:

- 尽量减少机壳上的缝隙和孔洞,特别是在连接器、按键、显示屏等开口周围。使用密封圈、导电涂层或内部挡板来减少ESD能量通过这些开口耦合进去。

五、 测试与验证

- ESD测试: 根据产品适用的标准(如IEC 61000-4-2)进行实际ESD测试(接触放电和空气放电),验证设计是否达到目标等级(如±8kV接触,±15kV空气)。测试应在最终产品组装状态下进行。

- 故障分析: 如果测试失败,仔细分析失效点,定位是耦合路径问题还是泄放路径不畅,并针对性改进设计(可能需要调整TVS选型、改进接地、修改布局、增加屏蔽等)。

总结关键原则

- 泄放路径优先: 首要任务是为ESD电流建立一条最短、最宽、电感最低的泄放路径到地(或机壳)。

- 靠近入口防护: 防护器件必须紧贴连接器端口。

- 坚固完整的地平面: 它是整个ESD防护系统的基础和核心。

- 最小化环路面积: 减少ESD磁场耦合。

- 结构配合: PCB设计要与机壳、屏蔽罩良好配合,形成完整的防护体系。

切记: ESD设计是一个系统工程,需要综合考虑器件选型、PCB布局布线、结构设计以及最终的测试验证。没有单一的“银弹”,往往是多个措施的协同作用才能达到最佳防护效果。在设计初期就充分考虑ESD并进行布局布线优化,比后期补救要高效得多。

静电是如何产生的 PCB如何设计防静电

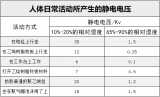

在干燥的环境下,人体静电(ESD)的电压很容易超过6~35Kv,当用手触摸电子设备、PCB或PCB上的元器件时,会因为瞬间的

2023-07-04 09:07:44

优化PCB布局走线的EMC静电整改方案

经过对PCB的研究发现,在充电弹片和正极充电路径下方的相邻层信号线过多,没有完整的地来释放静电,并有高速的flash信号经过。当静电打进来时,

2023-04-21 09:13:29

静电放电(ESD)最佳设计方案资料下载

电子发烧友网为你提供静电放电(ESD)最佳设计方案资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决

资料下载

![]() 佚名

2021-04-21 08:47:11

佚名

2021-04-21 08:47:11

PCB的电磁兼容测试设计方案

随之PCB板的电子元件和路线的流动量持续提升,以便提升系统软件的可信性和可靠性,务必采取相应的对策,使PCB板的设计方案考虑电磁兼容测试规定,提

2020-05-11 11:08:49

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机