allegro不同pcb之间的复制

在 Allegro PCB Editor 中,在不同 PCB 设计文件(.brd)之间复制对象(如元件、走线、铜皮、过孔、文本、板框等),最常用和推荐的方法是使用 Sub-drawing 功能。以下是详细步骤:

核心方法:使用 Sub-drawing (子图)

-

在源 PCB 文件 (

Source.brd) 中:- 打开包含你要复制内容的源 PCB 文件。

- 确保要复制的对象在当前设计中是可见且可选择的状态(检查层面、颜色设置)。

- 选择菜单:Place > Copy Mode (旧版本可能在 Edit > Copy 或 Place > Sub-drawing)。

- 中文路径可能为:放置 > 拷贝模式 (或 编辑 > 拷贝 / 放置 > 子图)

- 在 Options 面板:

- Activity: 选择

Copy。 - Origin: 这是关键步骤! 点击

Pick或Set Origin,然后在设计区域精确点击一个点作为参考原点(例如一个元件的引脚中心、板框角点、过孔中心等)。复制的所有对象都将相对于这个原点记录位置。粘贴时会用到这个点对齐。

- Activity: 选择

- 在画布上:

- 使用鼠标左键框选 (

Left-to-Right包含框内完整对象,Right-to-Left接触即选中) 所有你想要复制的对象。 - 或者按住

Ctrl+ 鼠标左键逐个选择对象。

- 使用鼠标左键框选 (

- 完成选择后,按鼠标右键选择 Complete (完成)。

- 弹出保存对话框:

- 给这个子图文件起一个名字 (例如

my_copy.clp)。 - 文件类型必须是

.clp(Clipboard 剪贴板格式)。Allegro 通常会默认添加后缀。

- 给这个子图文件起一个名字 (例如

- 点击 Save (保存)。现在源文件的操作完成。

-

在目标 PCB 文件 (

Target.brd) 中:- 打开你要粘贴内容的目标 PCB 文件。

- 确保粘贴区域的层面设置和设计规则(线宽、间距等)与源设计兼容。层叠结构 (Stackup) 最好一致,否则粘贴时需要仔细映射层。

- 选择菜单:Place > Place Mode (旧版本可能在 Place > Sub-drawing 或 Edit > Paste)。

- 中文路径可能为:放置 > 放置模式 (或 放置 > 子图 / 编辑 > 粘贴)

- 在 Options 面板:

- Activity: 选择

Place。 - Database: 勾选

Save Relative Path(如果.clp文件不在当前工作目录,通常需要勾选以正确找到路径)。 - Origin: 点击

Browse...,找到并选中你之前保存的.clp文件 (例如my_copy.clp)。 - Placement Origin: 点击

Set Origin,然后在目标设计区域精确点击一个点作为放置参考点(例如目标位置对应的元件引脚中心、板框角点、过孔中心等)。- 这个点将与源文件中设置的 Origin 点对齐。 粘贴的所有对象都将根据这两个原点的相对位置进行放置。

- Layer Options (层选项 - 非常重要!):

Keep layers: 粘贴对象保持它们在源文件中的层不变 (推荐)。前提是目标文件的层结构与源文件一致,或者有对应的层名。Map layers: 手动将源文件的层映射到目标文件的层 (当层结构/命名不同时使用)。点击Define Mapping按钮进行详细映射设置。

- Rename Options (重命名选项):通常用于元件位号 (RefDes)。

Add suffix/Add prefix: 粘贴时自动给位号添加前缀或后缀 (如U1变成COPY_U1),强烈推荐使用,避免位号冲突。Ignore: 保留源位号。极易导致位号重复冲突,不推荐!

- Other Options: 根据需要勾选

Ripup etch(自动挖空阻挡敷铜)、Retain net of vias(保留过孔的网络) 等。

- Activity: 选择

- 在画布上:

- 点击鼠标左键:此时,被复制的整个图形会随着鼠标移动。

- 将鼠标移动到你在目标文件中设定的

Placement Origin点附近 (系统会尝试吸附到你设定的点上)。 - 再次点击鼠标左键完成粘贴。所有对象将根据两个原点对齐放置。

关键注意事项

- 原点 (Origin) 是核心:

- 在源文件中设置的

Origin和在目标文件中设置的Placement Origin必须是你期望对齐的关键点(如某个焊盘中心)。这两个点的精准定位决定了复制内容的位置精度。

- 在源文件中设置的

- 层叠结构 (Stackup):

- 强烈建议源文件和目标文件使用相同的层叠结构定义 (层数、层名、类型)。 如果不同,在粘贴时 (

Keep layers模式):- 同名层:对象放在同名层上。

- 目标文件缺少的层:对象会被放在

Board Geometry层的某个子层(如BOARD GEOMETRY/SILKSCREEN_TOP),可能不是预期位置!需要手动调整层。

- 如果层结构差异大,务必使用

Map layers模式并仔细定义映射关系。

- 强烈建议源文件和目标文件使用相同的层叠结构定义 (层数、层名、类型)。 如果不同,在粘贴时 (

- 位号 (RefDes) 冲突:

- 务必在粘贴时使用

Add suffix或Add prefix选项自动修改粘贴过来元件的位号(如 U1 -> COPY_U1 或 U1_1)。直接保留源位号 (Ignore) 会引起目标设计中位号重复,导致严重问题。 - 粘贴后根据需要手动整理位号。

- 务必在粘贴时使用

- 网络 (Net) 属性:

.clp文件通常不保存网络名信息。粘贴过来的走线、铜皮、过孔通常会是No Net(无网络状态)。- 如果需要保留网络关系:

- 方法1 (复杂): 在导出 Sub-drawing 前,确保源设计中这些网络是定义好的。在目标设计中,必须先存在完全相同的网络名,并且在粘贴时确保选项保留了网络(如

Retain net of vias)。通常走线和铜皮的网络不容易保留。 - 方法2 (常用): 粘贴后,手动或使用

Logic > Net Logic > Identify DC Nets或Edit > Properties等方式重新分配网络。

- 方法1 (复杂): 在导出 Sub-drawing 前,确保源设计中这些网络是定义好的。在目标设计中,必须先存在完全相同的网络名,并且在粘贴时确保选项保留了网络(如

- 封装 (Symbols):

- 粘贴的元件将使用源设计中使用的封装路径下的同名封装 (.dra/.psm)。确保目标设计能找到这些封装文件(配置好

padpath和psmpath)。 - 如果目标设计中找不到同名封装,粘贴会失败或元件显示为

UNKNOWN。

- 粘贴的元件将使用源设计中使用的封装路径下的同名封装 (.dra/.psm)。确保目标设计能找到这些封装文件(配置好

- 设计规则 (Constraints):

- 粘贴的对象(线宽、孔径、间距)不会改变目标设计的规则设置。粘贴后务必进行 DRC 检查,确保新加入的内容符合目标设计的约束规则。

总结步骤口诀

- 源文件:

Place > Copy Mode-> 精确选原点 -> 框选内容 -> 保存为.clp文件。 - 目标文件:

Place > Place Mode-> 浏览加载.clp文件 -> 精确设放置原点 -> 设置层选项 (Keep layers/Map layers) -> 强制添加位号后缀/前缀 -> 点击放置。

遵循 Sub-drawing 流程并注意上述关键点,即可高效、准确地在 Allegro 的不同 PCB 文件间复制设计内容。

你知道PCB如何复制吗?

一站式PCBA智造厂家今天为大家讲讲电路板复制多少钱?PCB电路板抄板流程。根据客户提供的样品进行电路板复制、电路板改版、电路板打样,还可提供芯

2023-02-17 09:24:53

Cadence Allegro PCB设计详细教程资料合集

本文档的主要内容详细介绍的是Cadence Allegro PCB设计详细教程资料合集包括了:Allegro_常用快捷键说明,

资料下载

![]() ah此生不换

2020-06-12 17:40:11

ah此生不换

2020-06-12 17:40:11

PCB设计软件Allegro的学习教程免费下载

本文档的主要内容详细介绍的是PCB设计软件Allegro的学习教程免费下载包括了:Allegro学习笔记之1——导出Gerber文件和钻孔数据文

资料下载

![]() ah此生不换

2020-05-15 08:00:00

ah此生不换

2020-05-15 08:00:00

【Altium小课专题 第143篇】Allegro PCB如何转换成PADS PCB?

和错误信息,转换完成之后进行详细检查方可使用。 图6-272Allegro PCB的导入2.方法2如图6-273所示,利用各软件之间

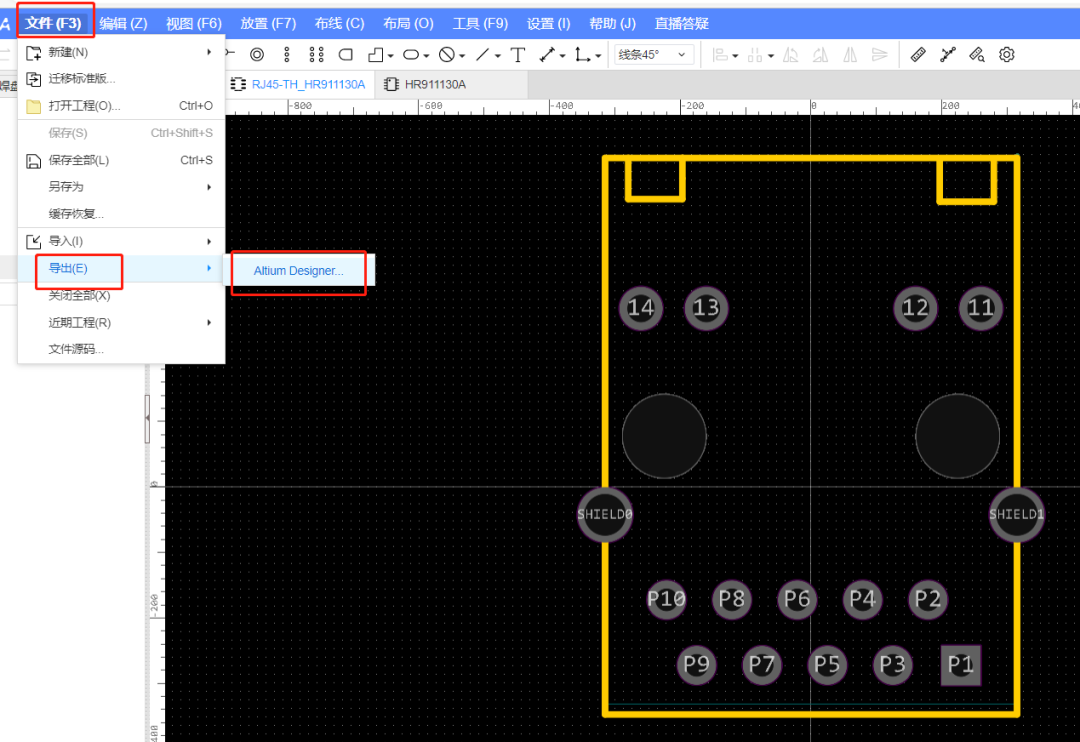

【Altium小课专题 第139篇】Allegro PCB如何转换成Altium Designer PCB?

跟原理图一样,因为各个公司的PCB设计软件不同,可能需要复制不同软件PCB设计里面的元件封装、模块、DDR走线等元素,这时候不同软件

PCB设计之Allegro软件问题

Allegro是Cadence推出的先进 PCB 设计布线工具,也是目前最高端、最主流的PCB软件代表之一,华为、中兴这类大型公司使用的也是

2019-10-11 16:40:38

【设计技巧】allegro PCB设计使用技巧

Display中的Ratsnest Points有两选项﹕1) Pin to Pin (Rats在Pin之间显现)2) Closest end point (Rats随走线改变显示) 15. 怎样复制多个有

Allegro设计PCB板的Out Of Date Shapes问题

使用Allegro设计PCB板时,查看Status,经常会遇到out of date shapes的警告信息,具体如下:

2019-06-16 10:02:58

cadence -- allegro和ad9之间的转换

将cadence allegro的brd文件导入AD中有2种方法:1。直接转换。AD summer 08 or winter 09已提供之间import的功能了。具体操作见Altium公司主页

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览