收发模块pcb 布线

更多

好的,收发模块(特别是射频收发模块)的 PCB 布线是设计的关键部分,直接影响性能(灵敏度、发射功率、噪声、稳定性)和可靠性。以下是用中文总结的核心布线原则和注意事项:

核心原则:控制阻抗、隔离干扰、保证完整性、优化电源/地

-

阻抗控制:

- 关键: 射频信号线(TX, RX, 本振 LO)必须进行严格的阻抗控制(通常是 50Ω 或 75Ω,具体看模块手册)。

- 实现:

- 使用 微带线 或 带状线 结构。

- 精确计算并控制线宽、信号层到参考地平面的高度(介质厚度)、介质常数。

- 保持阻抗连续性: 避免线宽突变、直角拐弯(用 45° 或圆弧拐弯)、过孔(尽量少用且优化)。过孔会引入不连续性和寄生电感。

- 参考地平面: 射频走线下方必须有完整、连续的 参考地平面(通常是相邻层的大面积铜皮),这是阻抗控制和信号回路的基础。避免在射频线下方的地平面开槽或走其他信号线。

-

隔离与屏蔽:

- 收发隔离: 发射通道 (TX) 和接收通道 (RX) 必须物理隔离。

- 尽量拉大 TX 和 RX 走线间距。

- 在 TX 和 RX 之间使用接地屏蔽过孔墙(Guard Vias),形成法拉第笼效应。

- 必要时,在 PCB 上进行 物理开槽(需谨慎,考虑结构强度和回流路径),并在槽两侧密集打接地过孔。

- 数字与模拟/射频隔离:

- 将数字电路(MCU、逻辑、时钟、数据总线)和模拟/射频电路严格分区布局。

- 两部分之间使用 电源/地分割(Split Planes)并确保单点连接(通常用一个磁珠或 0Ω电阻在一点连接两地平面),或者在混合信号区域使用统一的完整地平面(更推荐现代设计)。关键在于避免数字噪声电流流过敏感的模拟/射频地平面。

- 数字信号线(尤其是时钟、高速数据线)远离模拟/射频信号线,禁止平行长距离走线。必要时在它们之间加接地屏蔽过孔墙。

- 收发模块的控制线(如 SPI, I2C)靠近数字区域布线,串接小电阻(22-100Ω)或磁珠靠近收发模块端,有助于减缓边沿速度减少高频噪声发射。

- 本振 (LO) 隔离: LO 信号非常敏感且容易辐射干扰,也应尽量短,包地处理(两侧加接地过孔墙),远离其他敏感电路(如接收前端、天线端口)。

- 收发隔离: 发射通道 (TX) 和接收通道 (RX) 必须物理隔离。

-

信号完整性:

- 走线最短化: 关键射频路径(如天线到收发芯片、收发芯片到滤波器/PA/LNA)尽可能短,减少损耗和辐射。

- 避免交叉: 不同信号层上的走线尽量垂直交叉,避免平行重叠走线以减少串扰。

- 差分对: 如果收发芯片使用差分射频输入/输出(如某些 Zero-IF 架构),必须按差分线规则严格布线:等长、等距、对称、紧耦合、参考相同平面。

- 包地处理: 对于特别敏感或易产生干扰的线(如 LO、某些参考时钟),可在两侧布置密集的 接地过孔(Stitching Vias) 进行“包地”,形成屏蔽通道。

-

电源完整性:

- 分级滤波: 为收发芯片的每个电源引脚提供独立、低阻抗的供电路径和充分的多级滤波。

- 靠近芯片引脚: 放置高性能 去耦电容(通常是多个不同容值的 MLCC,如 10uF + 1uF + 0.1uF + 10pF 组合)。最小容值的电容要最近。

- 磁珠/电感隔离: 对于不同功能区块(如 RF 电源、PLL 电源、模拟电源、数字 IO 电源)的供电,在入口处使用磁珠或电感进行隔离(结合适当的滤波电容),防止噪声通过电源相互串扰。

- 低阻抗电源/地平面: 使用大面积、完整的电源平面和地平面。相邻的电源/地层形成良好的平板电容,提供高频去耦。

- 电源过孔: 电源引脚连接到电源平面时,使用多个过孔并联以减小阻抗和电感。地引脚亦然。

- 分级滤波: 为收发芯片的每个电源引脚提供独立、低阻抗的供电路径和充分的多级滤波。

-

接地:

- 低阻抗地平面: 提供完整、低阻抗的参考地平面是所有高速和射频设计的基础。

- 就近接地: 元器件(尤其是去耦电容、射频芯片)的接地引脚必须非常短且直接地通过过孔连接到地平面。避免长引线或“菊花链”接地。

- 过孔数量: 在射频区域和芯片周围,放置密集的接地过孔连接所有地层(如果有多层地),保证地平面电位一致,减小环路电感,并提供屏蔽。

- 混合接地策略: 对于数字、模拟、射频共存的系统,采用统一的完整地平面(Single Solid Ground Plane)通常是现代设计的最佳实践,但要严格分区布局并控制噪声源的回流路径。在某些特定场景下(如非常敏感的模拟前端),小范围的局部分割可能有效,但需极其谨慎。

-

天线接口/Antenna Port:

- 匹配网络: 天线端口连接的匹配网络(通常由 π 型或 L 型 LC 网络组成)元器件布局必须极其紧凑,走线最短化。

- 参考地清空: 在 RF 连接器(如 U.FL, MMCX)的焊盘下方和天线馈线区域下方的所有层,需要进行 “参考地清空” 。移除任何铜皮(包括地平面),形成一个净空区 (

Keepout)。这是为了防止地平面影响天线的辐射特性或阻抗。清空区域的大小和形状通常需要参考天线和连接器的设计指南或进行仿真。 - 天线馈线阻抗: 从匹配网络最后一级到天线连接器的馈线也必须进行 50Ω 阻抗控制(微带线),长度尽可能短。

-

辅助设计:

- 规则检查 (DRC): 布线后必须进行严格的 设计规则检查(线宽、线距、过孔、间距等)。

- 信号完整性/电源完整性仿真 (SI/PI): 对于高速或复杂设计,使用仿真工具分析关键网络的阻抗、串扰、损耗、电源噪声等。

- 电磁仿真 (EM): 对关键射频路径、天线接口、屏蔽结构进行 3D 电磁场仿真,验证隔离度、辐射特性、阻抗匹配等。

- 制造要求: 与 PCB 制造商沟通,明确其工艺能力(最小线宽/线距、最小孔径、铜厚、介质参数、阻抗控制公差等),并在设计中考虑其 DFM(可制造性设计)要求。

总结关键点:

- RF 走线: 50Ω 阻抗!短!连续!完整参考地!远离干扰源!

- 隔离: TX 和 RX 物理隔离(间距、接地过孔墙)!数字和模拟/RF 分区!

- 电源: 分区块!多级陶瓷电容去耦!磁珠/电感隔离!低阻抗平面!

- 接地: 完整平面!密集过孔!最短路径!避免分割噪声!

- 天线: 匹配网络紧凑!馈线阻抗控制!焊盘下方净空!

- 验证: DRC必做!仿真(SI/PI/EM)强烈推荐!

遵循这些原则能大大提高收发模块 PCB 设计的成功率和性能。务必查阅你所用特定收发芯片和元器件的官方数据手册和应用笔记,它们通常会提供具体的布局布线指南和参考设计。

一张表审视电路PCB布局布线设计(通用及射频模块)资料下载

电子发烧友网为你提供一张表审视电路PCB布局布线设计(通用及射频模块)资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、

资料下载

![]() 王娟

2021-03-27 08:44:23

王娟

2021-03-27 08:44:23

PT2262和PT2272无线收发模块的PCB原理图免费下载

本文档的主要内容详细介绍的是PT2262和PT2272无线收发模块的PCB原理图免费下载。

资料下载

佚名

2020-10-21 11:19:20

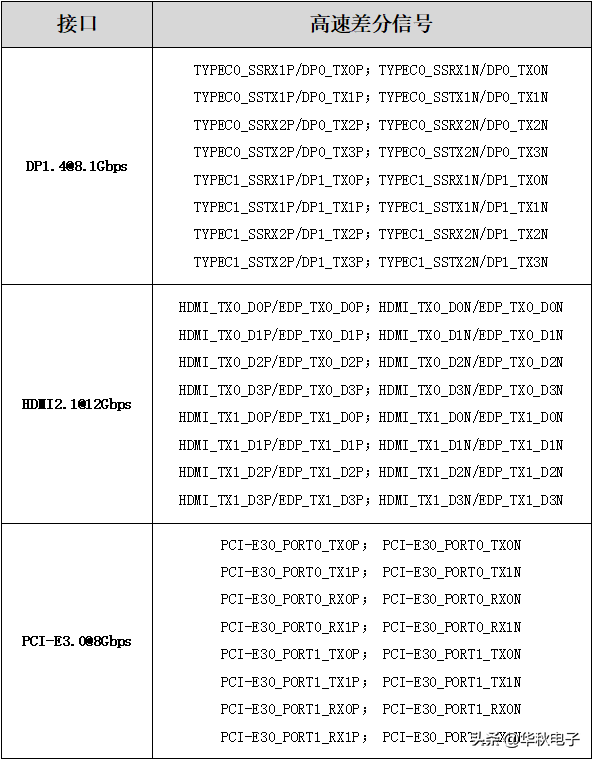

8Gbps及以上高速信号PCB布线建议

严格,在“PCBlayout 通用布线规范”的基础上,还需要根据本章节的要求来进行PCB布线设计。 表1-1 RK3588 8Gbps及以上差分

2023-08-02 07:35:01

7天热门专题

换一换

换一换

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览