0.5mm间距bga芯片的pcb设计

针对0.5mm间距BGA芯片的PCB设计,这是一项高密度互连(HDI)设计挑战,需要极其精细的规划和严格的制造工艺控制。以下是关键设计要点和注意事项:

一、 核心挑战

- 焊盘尺寸极小: 球直径通常在0.25mm - 0.30mm左右。

- 通道极窄: 焊盘间通道宽度可能不足100µm。

- 布线密度高: 内层和扇出区域布线密度极大。

- 对位精度要求高: PCB制造、贴装的对位精度要求极高。

- 成本敏感: 通常需要HDI工艺(激光微孔),成本显著增加。

二、 关键设计策略与规范

-

封装分析与规划:

- 获取准确封装文件: 从芯片厂商获取精确的.dat, .dra, .bsm文件(包含焊盘位置、尺寸、推荐钢网开口等)。

- 焊盘设计(SMD Pad):

- 推荐: 使用NSMD焊盘。

- 尺寸: 焊盘直径通常为球直径的80%-85%。例如,对于0.25mm球,焊盘直径约0.20mm - 0.22mm (8mil - 8.7mil)。必须严格遵循芯片厂商推荐值!

- 形状: 圆形首选,方形也可(需考虑制造能力)。

- 阻焊设计(Solder Mask):

- 开窗: 必须开窗,且开窗尺寸略大于焊盘。

- 桥宽: 阻焊桥是保证焊接不短路的关键。目标阻焊桥宽≥50µm (2mil)。这要求阻焊对准精度极高。

- 工艺: LCD(液态感光阻焊)或干膜阻焊,首选后者(精度更高)。

- 钢网设计(Aperture): (虽属SMT工艺,但与PCB焊盘设计强相关)

- 考虑焊盘尺寸、间距、阻焊桥宽来确定钢网开口尺寸和形状(通常方形或圆形)。

- 钢网厚度通常为0.08mm - 0.10mm。

- 确保锡膏释放良好,减少短路和虚焊风险。

-

布线策略:

- HDI工艺是必须的:

- 首选 激光钻孔形成的微孔。

- 微孔直径:典型的成品孔径为0.10mm (4mil)。必须与板厂确认其能力和成本。

- 焊盘尺寸:微孔在焊盘上的焊盘(Capture Pad)直径需≥0.25mm (10mil),以保证微孔与焊盘的环宽可靠性。

- 扇出(Fanout):

- 埋孔/盲孔扇出: 核心策略!

- 方式一:盘中孔(Via-in-Pad):

- 直接在BGA焊盘上钻激光微孔(填充并电镀填平)。

- 优点:节省空间,布线效率最高。

- 缺点:成本最高(需填孔电镀工艺);对孔位精度要求极高。

- 方式二:狗骨头式(Dog Bone):

- 将微孔打在相邻焊盘之间的通道上(焊盘外扇出)。

- 优点:工艺相对简单(可能不需要填孔),成本较低。

- 缺点:占用通道空间,限制了布线通道数量和线宽/线距。

- 层叠规划: 精心设计层叠结构,利用1+N+1(最常用)、2+N+2或更高阶HDI叠层,将信号快速扇出到内层。

- 走线宽度/间距:

- 目标线宽/线距:3mil/3mil (0.075mm/0.075mm) 是常见目标值。必须与板厂确认其量产能力和良率。

- 阻抗控制:若信号速率高,需进行阻抗计算。3mil线宽通常在薄介质层上才能达到50Ω阻抗(如FR4芯板厚度≤0.1mm)。

- 布线层分配:

- 优先在最靠近BGA焊盘的内层进行布线(减少微孔数量)。

- 尽量将高速信号布在带状线层(内层),减少干扰。

- 电源/地尽量使用内层平面层,利用过孔直接连接BGA电源/地焊盘。

- HDI工艺是必须的:

-

电源完整性(PI)与去耦:

- 多个低电感去耦电容: 尽可能靠近芯片的电源/地引脚放置(最好在BGA下方背面)。

- 紧密的电源/地平面对: 利用相邻层(如L2/L3)形成薄介质、高容值的电源/地平面对,提供低阻抗回路。

- 多过孔连接: 电源/地焊盘使用多个微孔并联连接到平面层,降低阻抗和寄生电感。

- 电源分割: 如果使用多个电压域,需在内层小心地进行电源分割,避免跨分割布线。

-

信号完整性(SI):

- 阻抗匹配: 关键高速信号线需严格控制阻抗(差分线尤为重要)。

- 等长控制: 对时序要求严格的并行总线或差分对需进行长度匹配。

- 串扰控制: 利用地孔隔离敏感信号线;在空间允许时增加线间距。

- 参考平面连续性: 高速信号线下方/上方应有完整的地平面作为参考,避免跨分割。

-

接地设计:

- 充足的地过孔: 在BGA区域内和周围放置大量地过孔(特别是激光微孔),连接表层地焊盘和内层地平面。

- 地环路: 为高速信号提供低阻抗、短回流路径。

三、 制造与可生产性(DFM)

-

与板厂紧密协作:

- 早期沟通: 在设计前期就与选定的、具备成熟0.5mm BGA和HDI生产能力的板厂沟通。

- 明确提交能力:

- 最小线宽/线距 (e.g., 3/3mil?)

- 最小激光钻孔孔径 (e.g., 0.10mm? 0.08mm?)

- 微孔对准精度 (至关重要!)

- 阻焊桥宽能力 (e.g., ≥50µm?)

- 盘中孔填充电镀能力

- 层间介质厚度控制能力

- 获取设计规则: 严格遵守板厂提供的HDI设计规范。

-

DFM审核:

- 使用DFM工具或人工仔细检查:

- 所有间距(焊盘-焊盘、焊盘-线、线-线、过孔-焊盘等)是否符合板厂规则。

- 阻焊桥是否足够(特别是在BGA区域)。

- 钻孔文件(特别是激光钻孔文件)准确性。

- 丝印是否避开焊盘和关键区域。

- 进行Gerber和钻孔文件检查。

- 使用DFM工具或人工仔细检查:

-

测试策略:

- 飞针测试: 可能是唯一可行的电气测试方法(传统针床夹具无法应对如此高密度)。

- 边界扫描: 在设计阶段就考虑加入JTAG边界扫描结构,提高可测试性。

- 烧录测试: 通过功能测试验证。

- X-ray/AXI: 贴装后必须使用X-ray检查焊接质量(桥连、开路、焊球大小、空洞等)。

四、 设计工具

- 必备高级功能:

- HDI设计支持: 支持激光钻孔、微孔、任意层互连定义。

- BGA扇出工具: 自动或半自动生成盘中孔或狗骨扇出方案。

- 约束管理器: 强大的线宽、间距、阻抗、等长规则设置与实时检查。

- 3D视图: 检查元件和过孔在Z轴方向上的冲突。

- 主流工具: Cadence Allegro, Mentor Xpedition, Altium Designer (需确认其对高端HDI的支持度)等。

五、 总结与建议

- HDI是必然选择: 接受使用激光微孔和可能需要的盘中孔工艺带来的成本。

- 精细化设计: 焊盘、阻焊桥、线宽线距、微孔尺寸必须精确计算和严格控制。

- 层叠规划先行: 良好的层叠设计是布线成功的基础。

- 扇出策略最关键: 盘中孔效率最高但成本最高;狗骨式需权衡布线空间。

- PI/SI贯穿始终: 从布局阶段就考虑电源分配和信号回流路径。

- 板厂是伙伴: 设计前、中、后期持续与板厂沟通,确保设计可制造且良率可控。

- DFM至关重要: 严格执行DFM检查,避免设计回炉。

- 测试方案早规划: 明确测试策略(大概率是飞针+边界扫描+X-ray)。

0.5mm间距BGA的设计是一项系统工程,要求设计师具备深厚的HDI知识、精密的操作技巧,并与板厂、贴片厂、测试工程师紧密合作,才能最终实现可靠、可制造、高性能的产品。 务必投入足够的时间和资源进行前期规划和验证。

请问LM96511 0.5mm间距的bga封装怎么处理呢?

0.5mm间距的bga封装怎么处理呢?如果扇出的话要用4mil的过孔进行激光打孔,价格十分昂贵。而如果在焊盘上打孔,孔径和焊盘大小应该怎么设置

0.4mm和0.5mm WLP的PCB设计注意事项和指南

使用晶圆级封装 (WLP) 可以减小解决方案的整体尺寸和成本。然而,当使用WLP IC时,印刷电路板(PCB)布局可能会变得更加复杂,如果不仔细规划,会导致设计不可靠。本文介绍了为您的应用选择0.4mm或

2023-03-07 13:48:10

0.5mm层叠封装应用处理器的PCB设计指南,第一部分

电子发烧友网站提供《0.5mm层叠封装应用处理器的PCB设计指南,第一部分.pdf》资料免费下载

资料下载

![]() 周臻庸

2024-10-14 11:15:06

周臻庸

2024-10-14 11:15:06

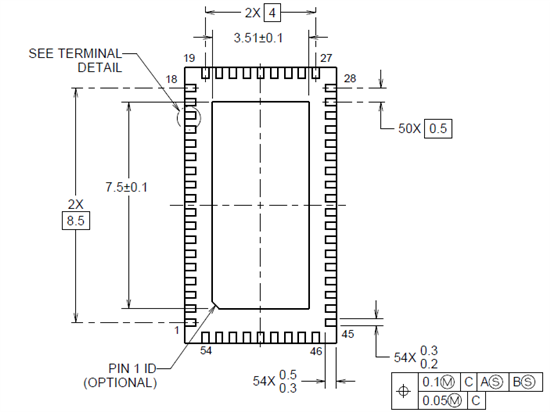

R0E436640CFK20 用户手册(64-pin 0.5mm间距LQFP转换板)

R0E436640CFK20 用户手册(64-pin 0.5mm间距LQFP转换板)

资料下载

![]() 贾熹

2023-05-04 19:45:02

贾熹

2023-05-04 19:45:02

0.5MM和0.8MM间距侧插板对板连接器公母座规格原理图免费下载

本文档的主要内容详细介绍的是0.5MM和0.8MM间距侧插板对板连接器公母座规格原理图免费下载。

资料下载

![]() h1654155946.4026

2020-01-08 08:00:00

h1654155946.4026

2020-01-08 08:00:00

针对PCB设计中由小间距QFN封装引入串扰的抑制方法

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线

BGA封装的PCB布线可靠性

目前,无论是ARM、DSP、FPGA等大多数封装基本上都是BGA或MBGA,BGA在PCB布线上的可靠性还都基本上能满足,但是MBGA封装的:

小间距QFN封装PCB设计串扰抑制的分析

BOTTOM层扇出。对于小间距的QFN封装,需要在扇出区域注意微带线之间的距离以及并行走线的长度。图一是一个0.5 pitch QFN封装的尺寸标注图。 图一

2021-11-10 09:42:22

浅谈波峰焊的最小间距PCB设计

保持的最小音高距离是多少? 通过适当的控制,仍然可以获得良好的结果,其间距可以低至0.5mm(.0197“)。 波形焊接缺陷可以在0.5mm以下

2021-03-01 10:57:52

【AD封装】FPC座子0.5mm间距1.0mm间距1.25间距(带3D)

`包含了我们平时常用的FPC接插件座子,总共103种封装及精美3D模型。其中包含了0.5mm间距FPC座子卧贴,1.0mm

BGA封装怎么突破0.5mm

当您突破BGA时,您基本上应用了扇出解决方案,并在PCB的一般布线之前将这些扇出的走线路由到设备的周边。几周前,我们举例说明了如何突破.4mm

2019-09-14 11:19:00

什么是小间距QFN封装PCB设计串扰抑制?

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- amoled屏幕和oled区别

- 单片机和嵌入式的区别是什么

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览