各种pcb的drc错误

好的,PCB设计中的DRC(设计规则检查)错误种类繁多,目的是确保设计满足电气、物理和制造要求。以下是一些常见的中文DRC错误类型及其简要解释:

一、电气连接性错误

- 短路:

- 描述: 两个或多个不应该连接的电气网络(Net)之间存在物理连接(如走线重叠、焊盘重叠等)。

- 后果: 会导致信号错误、电流流向异常,甚至烧毁元件或电路板。

- 常见原因: 走线间距过小导致重叠;不同网络的焊盘或过孔放置过近;铜箔区域覆盖错误;丝印误入焊盘造成潜在短路(虽然丝印不导电,但焊接时可能引起问题)。

- 开路/未连接:

- 描述: 设计中存在未连接的布线(悬空走线);元件焊盘没有连接到网络(飞线未布通);网络中存在断点。

- 后果: 信号或电源无法到达目的地,电路功能缺失。

- 常见原因: 手动布线遗漏;移动元件或走线后未重新连接;网络布线未完成;使用错误的网络标签(Net Label)。

- 未布线网络:

- 描述: 原理图中定义的电气连接关系(网络),在PCB布局布线阶段尚未用物理走线连接起来(飞线还存在)。

- 后果: 与开路类似,电路功能无法实现。

- 常见原因: 布线工作未完成;飞线被意外隐藏或忽略。

- 天线引脚:

- 描述: 元件的某个引脚(通常是输入引脚)通过一段较长的走线连接到焊盘或过孔,但没有最终连接到有效的驱动源(电源、地或输出引脚),形成一个类似“天线”的结构。

- 后果: 在制造过程中(如波峰焊)或板子工作时,该引脚可能积累静电荷,导致ESD(静电放电)损坏敏感元件(特别是MOS器件)。

- 常见原因: 布局布线不完整;特殊引脚(如未使用的IC输入脚)未按推荐方式处理(如上拉/下拉电阻或直接接地/电源)。

二、间距/间隙错误

- 走线到走线间距:

- 描述: 相邻走线(属于相同或不同网络)之间的距离小于设计规则设定的最小允许值。

- 后果: 可能导致信号串扰(Crosstalk)、耐压不足(高压板)、制造困难或良率下降(蚀刻时短路风险增加)。

- 走线到焊盘间距:

- 描述: 走线边缘到焊盘边缘(包括SMD焊盘和通孔焊盘)的距离过小。

- 后果: 焊接困难(焊锡桥接风险)、信号干扰、制造风险。

- 走线到过孔间距:

- 描述: 走线边缘到过孔外环边缘的距离过小。

- 后果: 同上(焊接、干扰、制造风险)。

- 焊盘到焊盘间距:

- 描述: 两个相邻焊盘(无论是否同网络)边缘之间的最小距离过小。

- 后果: 极易发生焊锡桥接短路,尤其是细间距IC(QFP, BGA等);组装困难。

- 过孔到过孔间距:

- 描述: 两个相邻过孔外环边缘之间的距离过小。

- 后果: 制造时钻孔可能导致孔壁破损(破孔)、孔铜连接(短路)、降低机械强度。

- 走线/焊盘/过孔到板边间距:

- 描述: 电气对象(走线、焊盘、过孔)距离PCB物理边缘太近。

- 后果: 在板边加工(如铣边、V割)时容易损坏铜箔,导致开路或短路;也影响安装和电气安全(爬电距离)。

- 丝印到焊盘间距:

- 描述: 丝印层(通常是顶层丝印

Top Overlay或底层丝印Bottom Overlay)上的文字、图形或边框与焊盘之间的距离过小。 - 后果: 丝印油墨覆盖焊盘会影响焊接(拒焊、虚焊),尤其是回流焊/波峰焊;丝印字符模糊不清。

- 描述: 丝印层(通常是顶层丝印

- 丝印到阻焊开窗间距:

- 描述: 丝印印刷区域与阻焊层开窗区域(即需要裸露焊接的铜区域)边缘距离过小。

- 后果: 丝印可能印到裸露的铜上,影响外观和焊接;丝印油墨侵入焊盘区域的风险。

- 钻孔到钻孔间距:

- 描述: 两个钻孔孔壁之间的最小距离(孔中心距减两孔半径)过小。

- 后果: 钻孔时钻头容易打滑导致孔位偏移或孔壁破损,降低可靠性。

- 钻孔到板边间距:

- 描述: 钻孔(特别是非金属化孔)距离PCB物理边缘太近。

- 后果: 板边加工时可能导致孔撕裂或部分缺失;影响机械强度。

三、物理尺寸/制造性错误

- 最小线宽违例:

- 描述: 走线的宽度小于设计规则允许的最小值。

- 后果: 电流承载能力不足(发热甚至烧断);制造成本增加或良率降低(蚀刻过度导致开路风险高);阻抗控制困难(高速信号)。

- 最小孔径违例:

- 描述: 钻孔(包括元件孔、安装孔、过孔)的直径小于制造商允许的最小值。

- 后果: 无法加工(钻头最小直径限制);孔铜电镀困难,孔壁铜厚不均,可靠性差(易断路);插装元件无法插入。

- 最小焊环违例:

- 描述: 焊盘围绕钻孔的环形铜环宽度(单边)小于规则要求。主要指通孔焊盘(PTH)和过孔。

- 后果: 钻孔对位稍有偏差就容易导致孔打破焊盘边缘,造成连接不良甚至开路;电镀不良风险增加;可靠性低。

- SMD焊盘上放置过孔:

- 描述: 在SMD(贴片)元件的焊盘上直接放置了过孔(通常在焊盘中心)。

- 后果: 焊接时熔融焊锡可能通过过孔流失到背面(俗称“吸锡”),导致焊点焊锡不足、虚焊或元件立碑(Tombstoning)。解决方式: 采用盘中孔工艺(Via-in-Pad, VIPPO),需特殊制造(树脂塞孔+电镀填平),成本高;或避免在焊盘上直接打孔,将过孔打在焊盘旁边(称为“泪滴”或“狗骨”连接)并用细线连接。

- 铜箔/孤岛:

- 描述: 在铜层(电源层、地层或信号层)上存在面积很小的、未连接到任何网络的孤立铜皮区域。

- 后果: 在蚀刻过程中这些小铜片可能脱落成为导电碎屑,导致板内短路风险;也可能引起EMI问题。

- 锐角:

- 描述: 走线拐弯处形成尖锐的夹角(通常小于90度)。

- 后果: 在制造蚀刻时,锐角处容易蚀刻不足(残留铜)或过度(线变细),增加短路或开路风险;高速信号时阻抗不连续,反射增大。建议使用45度或圆弧拐角。

四、其他规则错误

- 丝印覆盖元件:

- 描述: 丝印层(参考标识符、轮廓线等)放置在了元件的实体区域(通过元件的Place Bound或Courtyard区域判断)。

- 后果: 丝印可能被元件本体覆盖,失去标识作用;某些情况下影响元件放置(如果丝印是实体框)。

- 元件重叠/间距不足:

- 描述: 两个或多个元件的轮廓区域(Place Boundary / Courtyard)存在重叠或其间距小于规则设定的最小装配间距。

- 后果: 元件无法在装配线上正确贴装(机器碰撞);手工焊接困难;影响散热;维修空间不足。

- 阻焊桥缺失:

- 描述: 对于引脚间距很小的IC(如QFN、细间距SOP/QFP),两个相邻焊盘之间的阻焊层没有保留一条狭窄的阻焊材料带(即“桥”)进行隔离。

- 后果: 焊接时焊锡极易在两个焊盘之间桥接(短路)。

- 散热焊盘连接过少/错误:

- 描述: 大功率元件底部的散热焊盘(Thermal Pad/Pour)应该通过多个过孔连接到内层或底层铜皮散热。DRC可能检查连接到散热焊盘的过孔数量是否足够,以及这些过孔的连接方式(花焊盘连接 vs 实心连接)是否符合规则。

- 后果: 散热不良导致元件过热失效。

- 层对规则不匹配:

- 描述: 高速设计中对特定信号层(如所有走线层或相邻层)的规则设置(如线宽、间距)不一致或未按要求设置。

- 后果: 导致阻抗控制失效,信号完整性变差。

处理DRC错误的建议流程

- 理解错误: 仔细阅读DRC报告中的错误描述、涉及的对象(网络、元件、层)和位置坐标。

- 评估优先级:

- 最高优先级: 短路、开路、天线引脚、严重的间距违例(尤其是高压)、最小线宽/孔径违例。这些可能导致电路板完全失效或存在安全隐患。

- 高优先级: 焊盘间距不足、阻焊桥缺失、丝印覆盖焊盘/元件、焊环不足、重要信号间距不足(高速)。

- 中低优先级: 孤岛铜、非关键信号间距稍小、丝印到阻焊间距稍小、轻微的冗余过孔(除非严格限制)等。这些通常影响制造良率或外观,但不一定导致功能失效。

- 定位和修改: 在PCB编辑器中定位错误位置,根据规则要求和设计需求进行修改(如移动对象、调整走线、增加间距、删除多余铜、修改丝印位置、调整焊盘尺寸、增加过孔等)。

- 重新运行DRC: 修改后务必重新运行完整的DRC,确保所有错误均已修复,且修复操作没有引入新的错误。

- 与制造商沟通: 对于某些边界情况或特殊要求(如能否接受某个稍小的间距),提前与PCB制造商沟通确认其工艺能力。

牢记:DRC是保证PCB设计成功制造和可靠工作的关键步骤。绝不能忽视DRC错误直接发板生产! 仔细检查和修复所有DRC错误是PCB设计流程中不可或缺的一环。

嘉立创EDA专业版PCB的DRC与生产输出

前期为了满足各项设计的要求,通常会设置很多约束规则,当一个PCB设计完成之后,通常要进行DRC。DRC就是检查设计是否满足所设置的规则。一个完整

2023-04-04 07:40:02

【实用干货】PCB layout有DRC检查,为什么还要用DFM?

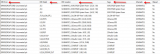

。 DRC和DFM检查原则比较 01 DRC检测项 (以Altium Designer为例) DRC检查 也叫设计规则检查,是

2022-11-17 08:20:06

PCB专业分析工具-独家BOM错误分析

华秋DFM-专业PCB设计分析软件,20万+工程师都在使用 1. 一键导入,自动出报价 2.一键分析23+项常见设计问题,解决设计隐患 3.智能拼版,节约单板采购成本 4.智能阻抗计算和反算 5. BOM智能分析,不再出现低级

资料下载

![]() ah此生不换

2021-08-09 16:52:52

ah此生不换

2021-08-09 16:52:52

华秋PCB-独家BOM错误分析

1、一键DFM分析,23+项常规PCB设计检查,独家断头线分析。 2、三步搞定特性阻抗,并支持反计算满足阻抗参数。 3、打开文件,生产资料,BOM/坐标/Gerber,一步搞定。 4、丝印输出

资料下载

![]() ah此生不换

2021-08-06 17:16:21

ah此生不换

2021-08-06 17:16:21

华秋PCB专业分析工具-独家BOM错误分析

华秋DFM-专业PCB设计分析软件,20万+工程师都在使用 1. 一键导入,自动出报价 2.一键分析23+项常见设计问题,解决设计隐患 3.智能拼版,节约单板采购成本 4.智能阻抗计算和反算 5. BOM智能分析,不再出现低级

资料下载

![]() ah此生不换

2021-07-30 16:49:58

ah此生不换

2021-07-30 16:49:58

电路原理图及PCB布线常见错误资料下载

电子发烧友网为你提供电路原理图及PCB布线常见错误资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

资料下载

![]() 王兰

2021-04-05 08:46:37

王兰

2021-04-05 08:46:37

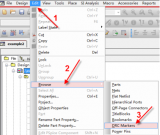

如何使用实时在线的DRC错误检查与管理设置功能

或者.dsn文件以后,OrCAD Capture软件会自动显示给出DRC规则检查的窗口OnlineDRCs,并在窗口中能清晰的看到原理图设计过程中存在的错误和警告信息。(3)在Online DRCs窗口

AD PCB中走直角丁字线的时候,DRC检查会出现当前线未连接错误

请教大家一下,我用的AD版本是17.0.6,在PCB布线中走图中那种直角的丁字线,然后在DRC检查的时候出现Un-Routed Net Constraint: Pad J107-11

Altium designer画了个PCB,用DRC校验没有错误,但在报告中显示有未连接的线应该怎么解决

请问一下,Altium designer画了个PCB,用DRC校验没有错误,但在报告中显示有未连接的线这个问题应该怎样解决啊?

PCB设计领域的DRC和MRC之间有什么区别?

今天的布局工具继续将越来越多的这些规则添加到他们的检查程序中。通常,所有这些规则都在一个设计规则菜单中提供,并为了方便起见分为不同的类别。使用PCB布局工具中提供的所有设计规则检查是确保创建无错误

2019-07-26 11:54:15

PCB设计电气规则检查器解决DRC问题

PADS® HyperLynx® DRC 提供功能强大的定制 PCB 设计电气规则检查器。不同于走线间距和线板边缘边界等传统 PCB 检查,PA

2019-05-21 06:08:00

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机

- 元宇宙概念龙头股一览