ddr3在12层pcb怎么设计叠层

好的,为 DDR3 设计一个 12 层 PCB 叠层需要考虑信号完整性(SI)、电源完整性(PI)、电磁兼容性(EMC)、制造工艺和成本。核心原则是:为关键信号(地址/命令/控制、数据/数据选通)提供相邻、完整的参考平面(GND 或电源),严格控制阻抗,最小化高速信号的过孔 Stub,并合理安排电源分配。

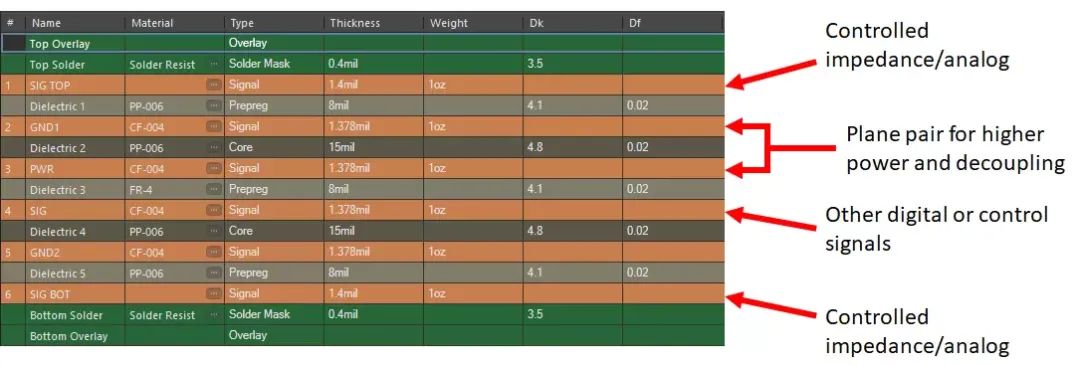

以下是一个经过验证且常用的 12 层叠层设计方案,特别优化了 DDR3 布线:

推荐叠层结构:

| 层序号 | 层类型 | 主要用途/说明 | 厚度 (典型值) | 核心/PP 位置 |

|---|---|---|---|---|

| L1 | 信号 | 顶层: 放置关键 DDR3 组件(内存颗粒、控制器)、少量关键走线、端接电阻、去耦电容。避免长 DDR 走线。 | ~3.5mil | |

| L2 | GND | 完整地平面: L1 的主要参考平面。极其关键!为 L1 和 L3 的高速信号提供低阻抗回流路径。 | ~2.5mil | PP |

| L3 | 信号 | 带状线层: 优先布放 DDR3 地址/命令/控制线 (Addr/Cmd/Ctrl)。参考 L2 (GND) 和 L4 (Power)。 | ~6.5mil | Core |

| L4 | Power | 核心电源平面 (如 VDD/VDDQ): 为 DDR3 颗粒和控制器供电。L3 和 L5 的参考平面。注意分割和载流能力。 | ~1.2mil | Core |

| L5 | 信号 | 带状线层: 优先布放 DDR3 数据组 (DQ/DQS/DM)。参考 L4 (Power) 和 L6 (GND)。 | ~6.5mil | Core |

| L6 | GND | 完整地平面: L5 和 L7 的主要参考平面。极其关键! 系统的中央地平面,提供低阻抗参考和回流。 | ~2.5mil | PP |

| L7 | 信号 | 带状线层: 布放剩余 DDR3 信号(如果 L3/L5 不够用)或其他低速信号、非关键信号。参考 L6 (GND) 和 L8 (Power)。 | ~6.5mil | Core |

| L8 | Power | 辅助电源平面 (如 VTT, VREF, 其他系统电源): L7 和 L9 的参考平面。特别注意 VREF 的纯净度(无噪声耦合)。 | ~1.2mil | Core |

| L9 | 信号 | 带状线层: 布放其他低速信号、非关键信号、GPIO等。参考 L8 (Power) 和 L10 (GND)。 | ~6.5mil | Core |

| L10 | GND | 完整地平面: L9 和 L11 的主要参考平面。关键! 为底层信号提供回流路径。 | ~2.5mil | PP |

| L11 | 信号 | 底层: 放置其他组件、连接器、少量走线、去耦电容。避免长 DDR 走线。 | ~3.5mil | |

| L12 | GND | 完整地平面: L11 的主要参考平面。关键! 屏蔽底层信号并提供回流。 | ~2.5mil | PP |

(PP = Prepreg, 半固化片)

这个叠层设计的关键优点和对 DDR3 的优化:

- 对称结构: (L1/L11, L2/L10, L3/L9, L4/L8, L5/L7, L6居中) 减少了翘曲风险,有利于制造。

- 关键信号内层带状线: 地址/命令/控制 (L3) 和数据组 (L5) 都被放置在内层带状线环境。这提供了:

- 优良的 EMI 屏蔽: 被上下平面包裹,辐射和抗干扰能力强。

- 稳定的阻抗控制: 带状线阻抗受外界影响小,更容易精确控制到目标值(通常是 50Ω 单端,100Ω 差分)。

- 较短的过孔 Stub: L3 和 L5 接近板中心,从表层打到这两层的过孔 Stub 相对较短 (Stub 长度 ≈ 到该层的深度),对高速 DDR3 信号完整性影响较小(相比放在表层或靠外层)。

- 相邻完整参考平面: 每个关键信号层 (L3, L5) 都有直接相邻的上、下参考平面 (L2/GND, L4/PWR 和 L4/PWR, L6/GND)。

- 低阻抗回流路径: 确保高速信号电流有紧密、低感抗的回流路径,减少地弹和 EMI。

- 精确阻抗计算: 参考平面临近且完整,阻抗易于计算和控制。

- 减少串扰: 临近平面限制了信号场向相邻层扩散。

- 坚固的“地-信号-地”三明治结构: L2-GND / L3-Sig / L4-PWR 和 L5-Sig / L6-GND / L7-Sig 形成了有效的“地-信号-电源”或“信号-地-信号”的隔离结构,非常有利于高速信号。尤其是中央的 L6-GND 是系统的“脊柱”。

- 优化的电源分配:

- L4 分配核心电源 (VDD/VDDQ),靠近关键信号层 L3 和 L5。

- L8 分配辅助电源 (尤其 VTT, VREF),靠近可能使用它们的信号层 L7 和 L9。

- VREF 平面 (L8): 确保 VREF 平面非常干净(仔细滤波,远离噪声源),并且靠近其参考的信号层(通常是数据层 L5/L7)。VREF 对噪声极度敏感。

- VTT 平面 (L8): 需要承载较大电流(端接电阻电流),注意平面完整性和足够载流能力。

- 表层用途合理: L1 和 L11 用于放置器件和非常短的连接(如端接到电阻、电容的短线),避免长距离高速走线,减少 EMI 辐射和阻抗不连续性。

设计实施要点:

- 阻抗计算: 必须使用 PCB 厂提供的具体板材参数(如 FR4 的 Er 值)和叠层厚度,利用 SI 工具(如 Polar SI9000或其他EDA工具内置工具)精确计算线宽、间距以达到目标单端阻抗(50Ω)和差分阻抗(100Ω)。

- 参考平面连续性:

- 绝对禁止关键 DDR3 信号线跨分割参考平面的裂缝!这会导致阻抗突变、回流路径剧增,严重破坏 SI。

- 确保 L2, L4, L6, L8, L10, L12 平面在 DDR3 信号布线区域下方是完整无割裂的。电源平面分割要谨慎规划。

- 过孔设计:

- 使用尽可能小的过孔(如 8/16mil)。

- 对于打到 L3 和 L5 的过孔,考虑背钻 (Backdrill) 工艺去除延伸到更远层的多余铜柱(Stub)。这对于 >1Gbps 的 DDR3 速率尤其重要。需与板厂确认能力和成本。

- 尽量减少过孔数量。避免在差分对中间打过孔。

- 走线规则:

- 长度匹配: 严格控制同一字节通道内的 DQ/DQS/DM 之间(±5-15mil),所有字节通道的 DQS 之间(±25-50mil),地址/命令/控制组相对于时钟(CK/CK#)的等长(规格书要求,通常比数据组宽松些)。

- 间距: 遵循 3W 规则(线中心距 >= 3倍线宽)减少串扰,尤其同层平行走线。不同层走线避免上下平行重叠。

- 差分对: 严格控制 DQS±/CK± 的线宽、间距、对内长度差(±1-5mil)。保持对称性。

- 避免锐角: 使用 45° 或圆弧拐角。

- 去耦电容:

- 在 L1/L11 靠近每个 DDR3 颗粒和控制器电源引脚放置多数量、小尺寸(如 0.1uF, 0.01uF)、低ESL 的陶瓷电容。目标是覆盖宽频段(高频电容靠近引脚)。

- VTT 端接电阻附近放置足够的大容量(如10uF)电容,提供瞬态电流。

- VREF 滤波: 使用 RC 滤波器(靠近颗粒 VREF 引脚)确保 VREF 纯净。

- 端接电阻:

- 地址/命令/控制线通常需要并行端接 (VTT),电阻放置在走线末端(靠近最后一个颗粒)。

- 数据组 (DQ/DQS/DM) 通常由控制器和颗粒内部端接(ODT)。外部端接电阻(如果设计需要)应靠近控制器放置。

- 仿真验证: 在最终投板前,强烈建议使用 SI 工具(如 HyperLynx, ADS, HSPICE 等)进行布线前预研和布线后仿真,检查时序裕量、信号质量(过冲、振铃、眼图)、串扰等。

总结: 这个推荐的 12 层叠层将关键的 DDR3 地址/命令组和数据组分别放置在 L3 和 L5 的内层带状线层,为它们提供了稳定、屏蔽、阻抗易控的环境,并配备了直接相邻的完整参考平面。中央的地平面 (L6) 和合理的电源平面分配 (L4, L8) 保障了电源完整性和系统稳定性。务必严格遵守阻抗控制、参考平面连续性、长度匹配和正确的端接/去耦设计原则,并通过仿真验证设计。记住,具体厚度和材料需与 PCB 制造商紧密合作确定以满足阻抗和工艺要求。

PCB叠层结构设计详解

随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层

资料下载

![]() 传奇198

2022-09-30 12:03:38

传奇198

2022-09-30 12:03:38

PCB的分层及叠层有哪些讲究资料下载

电子发烧友网为你提供PCB的分层及叠层有哪些讲究资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用

资料下载

![]() 胡秋阳

2021-04-02 08:46:31

胡秋阳

2021-04-02 08:46:31

PCB叠层的几种不同变体

两个实验设计的结果一起显示。注意,MOSFET和层4平面之间也没有直接连接,相应的电路拓扑将显示在第89页的图2中。 (1)单层板。 (2)2层

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机