pcb 走线延迟

PCB(印制电路板)中的 走线延迟 是指电信号在PCB导线(走线)上传输所需的时间。这是一个关键的信号完整性概念,尤其是在高频或高速数字电路设计中(如DDR内存、高速串行链路、时钟电路等)。

以下是关键要点:

-

物理本质:

- 电信号在导线中以电磁波的形式传播。

- 这种传播速度低于真空中的光速(

c ≈ 3×10⁸ m/s)。 - 延迟就是信号从走线一端传播到另一端所需的时间。

-

计算公式:

- 走线延迟主要取决于两个因素:

- 走线的物理长度 (

L):单位通常为米 (m) 或厘米 (cm)。 - 信号在走线中的传播速度 (

v):单位是米每秒 (m/s)。

- 走线的物理长度 (

- 延迟 (

t_d) 的基本计算公式为:t_d = L / v - 传播速度 (

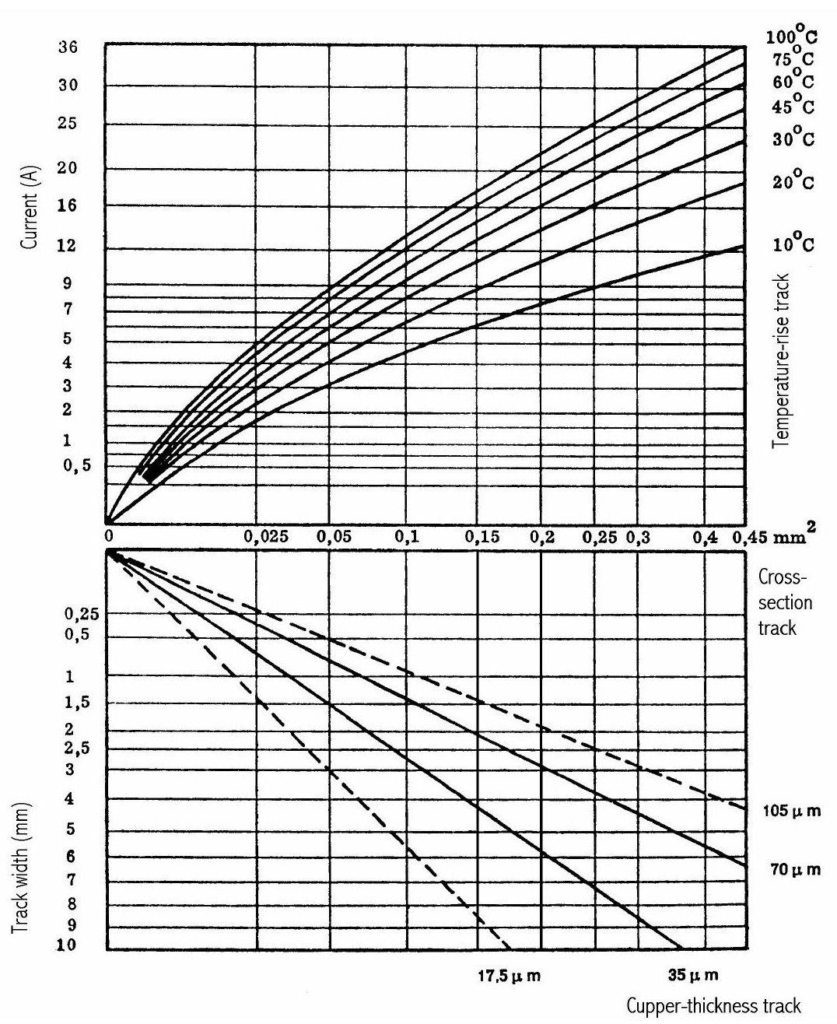

v) 由PCB材料的等效介电常数 (ε_eff) 决定:v = c / sqrt(ε_eff)c是真空中光速。ε_eff是覆铜板材料(如FR-4)和周围环境(阻焊层、空气)共同作用下,信号感受到的“有效”介电常数。对于表面微带线,ε_eff通常在 3.0 到 4.5 之间(FR-4典型值约4.0-4.5);对于内层带状线,ε_eff更接近材料本身的介电常数(FR-4约4.2-4.7)。

- 常用简化估算(FR-4材料):

- 延迟 ≈ 传输长度 × 单位长度延迟

- 单位长度延迟 ≈ 50 - 70 ps/cm (皮秒/厘米)

- 单位长度延迟 ≈ 5.0 - 7.0 ns/m (纳秒/米)

- 传播速度 ≈ 15 cm/ns (厘米/纳秒) 或 6 in/ns (英寸/纳秒)

- 走线延迟主要取决于两个因素:

-

为什么重要?:

- 时序匹配/等长走线:在并行总线(如DDR)或差分对中,信号必须同时到达接收端。走线延迟差异(长度不匹配)会导致时序偏移(Skew),可能引起建立/保持时间违例,导致数据错误。设计师需要进行蛇形绕线来精确匹配关键信号线的延迟。

- 总系统时序预算:信号在芯片、走线、连接器中的传输延迟总和必须满足系统的时序要求。走线延迟是其中重要组成部分。

- 信号完整性分析:仿真信号反射、串扰、衰减等效应时,延迟是基本输入参数。

- 时钟分配:时钟信号到达不同芯片的时间差(时钟偏移)直接影响系统同步性能,其中走线延迟是主要因素。

-

影响因素:

- 走线长度 (

L):最直接的影响因素。长度越长,延迟越大。 - PCB材料介电常数 (

ε_r):板材的ε_r越高(如FR-4的ε_r≈4.5),有效介电常数ε_eff越大,传播速度v越低,单位长度延迟越长。高频板(如Rogers)通常具有更低更稳定的ε_r。 - 走线几何结构:

- 微带线 (Microstrip):信号线在表层,下方有参考平面。

ε_eff受空气(ε_r≈1)和板材共同影响,相对较低(典型3.0-4.5),速度较快,延迟较小。 - 带状线 (Stripline):信号线夹在两个参考平面中间。

ε_eff主要由板材决定且较高(接近板材的ε_r,如4.2-4.7),速度较慢,延迟较大。

- 微带线 (Microstrip):信号线在表层,下方有参考平面。

- 阻焊层:覆盖在表层走线上的阻焊油墨也有介电常数,会影响表层微带线的

ε_eff。 - 温度:材料的介电常数可能稍有温度依赖性。

- 走线长度 (

-

如何应对:

- 精确计算/仿真:使用PCB设计软件(如Cadence Allegro, Mentor Xpedition, Altium Designer)或专用信号完整性工具(如HyperLynx, ADS, SIwave)根据实际的走线几何结构、材料和层叠信息计算延迟并进行仿真分析。

- 等长布线规则:对关键信号组(时钟、数据总线、地址总线、差分对)设定精确的长度匹配(或更准确地说是时间延迟匹配)规则。

- 蛇形绕线:用于增加长度较短走线的实际长度,以达到与其他走线匹配的延迟。

- 选择高频板材:在要求极高的场合(如10+Gbps),选用低

ε_r、低损耗角的材料(如Rogers, Megtron)可以降低延迟并改善信号质量。 - 控制走线类型:在速度和屏蔽需求之间权衡选择微带线(更快)或带状线(更佳屏蔽,但稍慢)。

总结:PCB走线延迟是信号在导线上传输的时间消耗,由长度和传播速度(取决于材料介电常数和走线结构)共同决定。在高速数字设计中,精确管理和匹配走线延迟对于确保系统稳定可靠运行至关重要。FR-4板材下,一般按 50-70皮秒每厘米 (ps/cm) 或 5-7纳秒每米 (ns/m) 估算。

有关PCB走线以及如何为PCB设计正确走线的重要事项

设计 PCB 变得非常容易, 由于可用的工具负载。对于正在接触PCB设计的初学者来说, 他可能不太关心PCB中使用的

2023-05-13 15:15:46

PCB直角走线的影响

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout

资料下载

![]() 时见栖鸦

2022-02-11 15:24:33

时见栖鸦

2022-02-11 15:24:33

PCB设计:通常的BGA器件如何走线?资料下载

电子发烧友网为你提供PCB设计:通常的BGA器件如何走线?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参

资料下载

![]() 向日葵的花季

2021-04-07 08:43:21

向日葵的花季

2021-04-07 08:43:21

PCB设计中如何实现等长走线

频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长

2020-11-22 11:54:17

PCB设计做等长走线的目的是什么

,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走

2020-10-24 09:29:38

pcb蛇形走线

;=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机