quartus sheji pcb

好的,明白了!您的问题“quartus sheji pcb”翻译成中文就是 “Quartus设计PCB”。

不过,这里需要明确一个重要概念:

Quartus Prime (Intel/Altera的FPGA/CPLD开发软件) 本身 不直接 设计 PCB (印刷电路板)。

Quartus Prime 主要用于 FPGA 或 CPLD 器件的 内部逻辑设计、仿真、综合、布局布线 和 生成编程文件。

那么,Quartus Prime 和 PCB 设计有什么关系呢?

Quartus Prime 在 PCB 设计流程中扮演着 至关重要的前期角色,其主要贡献在于:

-

I/O 引脚分配:

- 这是 Quartus 与 PCB 设计最核心的连接点。在设计 FPGA 时,您需要在 Quartus 中精确地指定 FPGA 芯片的每个信号(时钟、数据、控制线等)使用芯片封装的哪个物理引脚。

- 这些引脚分配信息会导出为特定格式的文件(如

.pin,.csv,.tcl等)。

-

生成引脚约束文件:

- Quartus 可以将您分配的引脚信息导出为标准格式的文件。

- 最关键的文件通常是

*.pin文件或*.csv文件(包含 Pin Number, Pin Name, Signal Name, I/O Standard, Direction 等)。 - 有时也需要生成包含引脚位置信息的

IPC-356网表或*.mnl(Allegro) 文件。

-

提供给 PCB 设计工具:

- 上述导出的引脚约束文件,需要导入到专业的 PCB 设计软件(如 Altium Designer, Cadence Allegro, KiCad, Mentor Xpedition/PADS 等)中。

- 在 PCB 设计软件中:

- 引脚约束文件告诉PCB工具: FPGA 芯片的哪个物理引脚对应哪个信号名称(Net Name)。

- 创建/匹配元器件符号: 您需要在PCB软件中为您的FPGA芯片创建一个符号(Symbol)/封装(Footprint),这个符号上的引脚编号(Pin Number)必须与 Quartus 导出的文件中的物理引脚编号 完全一致。

- 连接网络: PCB 设计工程师根据原理图,将其他元器件(如电阻、电容、连接器、存储器等)的信号线连接到 FPGA 符号上对应的网络标签(Net Label)。这些网络标签的名称通常与 Quartus 中的信号名称一致或通过映射关联。

总结流程 (Quartus 如何参与 PCB 设计)

-

在 Quartus Prime 中:

- 完成 FPGA 的逻辑设计、仿真、综合。

- 最关键步骤: 在 Quartus Pin Planner 或 Assignment Editor 中,为所有连接到 PCB 的 FPGA 引脚分配具体的物理引脚编号。

- 导出引脚约束文件 (

.pin,.csv,.tcl,.mnl,IPC-356等 - 具体格式取决于您的 PCB 工具)。

-

在 PCB 设计软件中 (如 Altium, Allegro, KiCad):

- 创建或加载目标 FPGA 芯片的 元器件符号(Symbol) 和封装(Footprint)。确保符号上的引脚编号与 Quartus 分配的物理引脚编号 严格匹配。

- 导入 Quartus 导出的引脚约束文件: 这通常通过特定命令或插件完成。

- 关键作用: 这个导入过程将 Quartus 中的 信号名称(Signal Name) 与 PCB 符号中的 物理引脚编号(Pin Number) 和 网络名称(Net Name)正确地关联起来。

- 设计完整的电路原理图,将 FPGA 与其他元器件通过定义的网络连接起来。

- 进行 PCB 布局布线:根据原理图的连接关系和约束(包括FPGA引脚位置),在电路板上放置元器件并连接铜线。

重要提醒

- 引脚分配的准确性至关重要: Quartus 中的引脚分配错误,会导致 PCB 上错误的连接,可能造成板子无法工作或者需要飞线修改,代价昂贵。务必反复检查!

- 考虑 I/O 标准: Quartus 中分配的不仅是引脚号,还有 I/O 电气标准(如 LVCMOS 3.3V, LVDS, SSTL 等)。这些标准影响 PCB 上的端接电阻、走线阻抗要求等,通常也会导出或在约束文件中体现。

- 目标封装: 在设计 FPGA 逻辑和分配引脚之前,必须确定您将使用的 FPGA 芯片的具体型号和封装。不同封装的引脚排列完全不同。

- 工具链协作: Quartus 和 PCB 工具需要协同工作。了解您使用的 PCB 软件偏好哪种格式的约束文件,并在 Quartus 中正确导出。

简而言之:Quartus 负责为 PCB 设计提供 FPGA 芯片的“接线蓝图”(即引脚分配约束文件),PCB 设计软件则利用这个蓝图来确保电路板上连接到 FPGA 的线路是正确的。

Altera正式推出Quartus Prime Pro 26.1版本

以更快、更广、更简为核心,Altera 正式推出 Quartus Prime Pro 26.1 版本。新版本实现了更高效的编译与时序收敛、更顺畅的开发者设计流程,并简化了用户操作与 AI 集成

2026-04-20 14:29:16

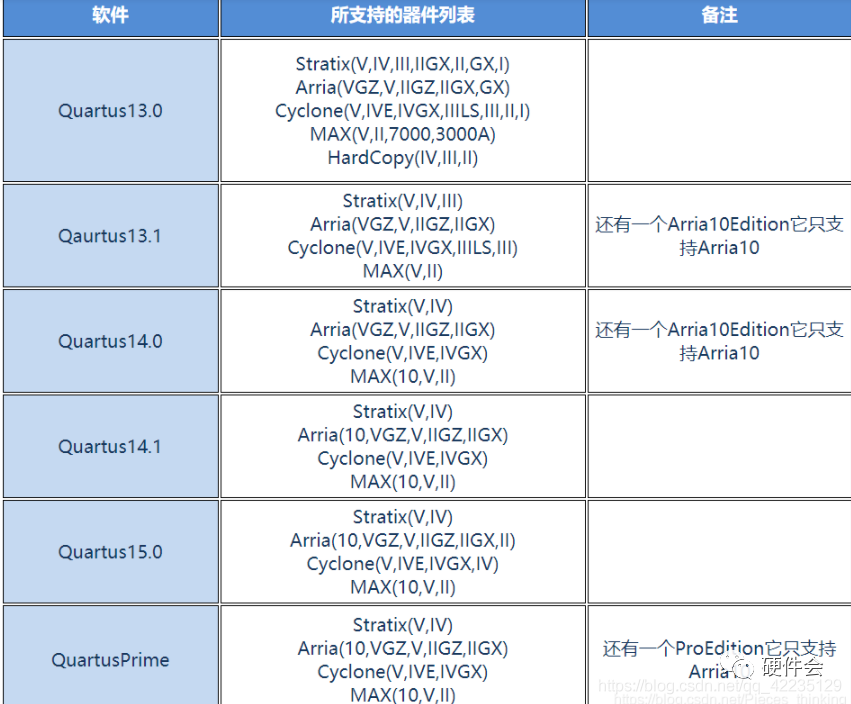

Quartus Prime Pro 25.1版本的安装和使用

如果用户开发板是基于Agilex 3、Agilex 5等高阶器件,则需要安装高版本的Quartus软件比如Quartus Prime Pro 25.1版本,这个版本在安装包和license获取(免费)等方面跟以往的

2025-10-07 13:06:00

使用Quartus II编程CPLD和FPGA设备的教程说明

Quartus II软件为使用Altera?FPGA和CPLD设备进行设计的系统设计师提供了一个完整的软件解决方案。Quartus II程序员是Quartus

资料下载

佚名

2020-09-17 14:41:00

如何使用quartus建立工程详细视频教程免费下载

Quartus II design 是最高级和复杂的,用于system-on-a-programmable-chip (SOPC)的设计环境。 Quartus II design 提供完善

资料下载

佚名

2019-04-23 16:45:43

Quartus的license问题

: quartus License path:E:\\APP\\quartus\\bin64\\license.dat FLEXnet Licensing error:-8,523 For further

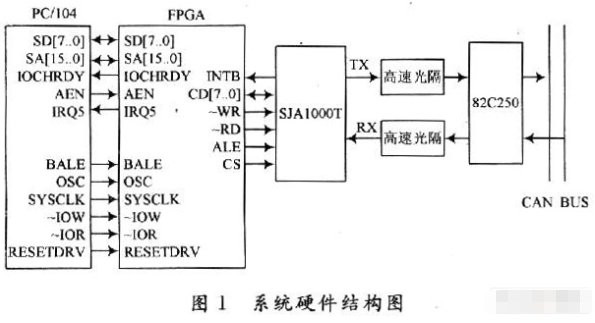

基于QuartusⅡ和控制器实现总线通讯板的设计

QuartusⅡ是Altera公司在21世纪初推出的FP-GA/CPLD开发环境,是Altera前一代FPGA/CPLD集成开发环境MAx+PlusⅡ的更新换代产品,其功能强大,界面友好,使用便捷

2021-06-08 15:43:08

Quartus 安装错误

`There has been an errorError running E:桌面 Quartus Il13.1(64bit)Quar tus

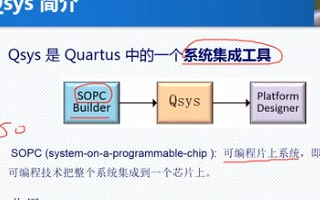

FPGA verilog相关视频:quartus中的qsys的讲解

该课程是正点原子团队编写,详细讲解了quartus中的qsys。也可以从我头像点进去看FPGA verilog相关的视频。

2019-08-06 06:02:00

Quartus II破解和注册

软件无法使用的问题已经在网友的帮助下得到解决,这里我总结一下解决办法:注意:操作之前请先关闭Quartus软件1)点击下载附件keygen.zip,解压。2)对于64位操作系统的电脑,将"

modelsim和Quartus使用问题

Quartus 使用的是12.0版本,modelsim使用的是modelsim se-64 10.4版本,在进行仿真时,出现以下错误:Fatal: Internal Error - vopt

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- ssd是什么意思

- 什么是蓝牙?它的主要作用是什么?

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机