pcb 抢答器电路

好的!这是一个基于常用数字集成电路(74系列)实现的简易PCB抢答器电路设计方案(中文说明),思路清晰,易于理解和制作。

核心功能:

- 多路输入: 允许多名选手(例如4路)通过按钮抢答。

- 优先锁存: 第一个按下按钮的选手信号被锁定,并阻止后续选手的信号通过。

- 状态指示: 通过LED灯显示哪位选手抢答成功。

- 复位: 主持人可以通过一个按钮清除锁存状态,为下一轮抢答做准备。

所需主要元器件:

- 优先编码器:

74LS148(8线-3线优先编码器,我们只用4路或8路) 或74HC147(10线-4线BCD优先编码器,也可只用4路)。核心器件,负责识别最先按下的按钮并输出其编码。 - RS锁存器:

74LS279(四路RS锁存器) 或74HC279。用于锁存“有抢答信号”的状态和获胜者的标识。 - 译码器/驱动器:

74LS47(BCD到7段译码器/驱动器) + 7段数码管 或74LS138(3线-8线译码器) + LED指示灯。用于将获胜者的编码(通常是二进制)转换成直观的显示(数字或点亮对应LED)。 - 或非门:

74LS02(四2输入或非门) 或74HC02。用于组合信号和控制锁存。 - 按钮开关: 用于选手抢答 (

S1-S4) 和主持人复位 (RST)。 - LED: 用于显示抢答成功 (

L1-L4) 或抢答状态指示。 - 电阻: 上拉电阻 (例如10kΩ,用于按钮)、限流电阻 (例如220Ω-1kΩ,用于LED/数码管)。

- 电容: 电源去耦电容 (例如0.1uF陶瓷电容)。

- PCB电路板: 单面板或双面板。

- 电源: 5V直流电源 (为兼容74LS/HC系列芯片)。

电路原理框图与工作流程:

+-----------+ +------------+ +-----------+ +------------------+ +-------------+

| 抢答按钮 | | 优先编码器 | | RS锁存器 | | 译码器 & 驱动器 | | 显示设备 |

| S1, S2, |-->| (74LS148) |-->| (74LS279)|-->| (74LS47 + 数码管 |-->| (数码管 |

| S3, S4 | | 或 74HC147 | | 或 74HC279)| | 或 74LS138 + LED)| | 或 LED L1-L4)|

+-----------+ +------------+ +-----------+ +------------------+ +-------------+

^ | | |

| | | |

| +---v----+ +---v----+ |

| | 或非门 | | | |

| | (74LS02)| | | |

| +----+----+ | | |

| | | | |

| | +---v----+ | |

| +------->| 复位端 | | |

| | (RST) |<--+-------------+

| +--------+ |

| 主持人复位按钮 |

+----------------------------------------------------+

(控制整个系统的复位)详细工作原理:

-

初始状态 (复位后):

- 所有按钮 (

S1-S4) 未被按下。 - 优先编码器 (

U1: 74LS148/147) 的所有输入端 (I0-I3或I1-I4) 为高电平 (通过上拉电阻)。编码器输出其“无有效输入”的状态(对于148是GS为高,A2A1A0为111;对于147是GS为高,输出为伪BCD码如1111)。 - RS锁存器 (

U2: 74LS279) 的输出Q被复位端 (R) 强制为低电平(假设低电平有效锁存抢答信号)。 - 这个锁存器输出

Q的低电平通过或非门 (U3: 74LS02) 反馈到编码器的使能端 (EI- 低电平有效)。此时锁存器输出为低,经过或非门反相后变成高电平,送到编码器EI端,使得优先编码器处于禁止状态(不工作)。 同时,这个低电平也送到译码器的控制端(如消隐端BI/RBO)或作为锁存器的另一个输入。 - 显示设备(数码管或LED)不显示任何获胜者(数码管消隐或所有LED熄灭)。

- 所有按钮 (

-

选手抢答:

- 假设选手1 (

S1) 最先按下按钮。S1对应的输入端(例如I0)被拉低到地。 - 优先编码器 (

U1) 的使能端 (EI) 虽然接收到高电平(来自或非门),但由于锁存器输出Q是低电平(表示系统空闲允许抢答),这个高电平会通过或非门U3的一个门,与锁存器Q一起产生一个低电平信号,送到编码器的EI端,使能编码器工作。(关键逻辑:利用锁存器Q和编码器GS信号通过门电路控制编码器EI和锁存器S) - 检测到有效的低电平输入 (

I0),优先编码器U1工作:- 输出该输入的编码(例如对于148,

I0对应A2A1A0 = 000)。 - 同时,其组选通输出端

GS变为低电平(表示有有效输入)。

- 输出该输入的编码(例如对于148,

- 编码器输出的

GS(低电平有效)信号连接到RS锁存器 (U2) 的置位端S(假设S低电平有效置位)。 GS的低电平将锁存器U2置位,使其输出Q跳变为高电平。- 锁存器

Q变为高电平有两个关键作用:- 它通过或非门

U3反馈到编码器的EI端。Q为高,经过或非门后输出变低,送到了编码器EI端,使得编码器被禁用 (EI高电平禁止)。 这意味着即使此时其他选手再按下按钮(I1-I3变低),编码器也不会再响应和改变输出!优先权被锁定给第一个抢答者(选手1)。 - 这个高电平

Q也作为“抢答有效”信号,可以用于驱动一个蜂鸣器或解锁译码器的显示(例如送到74LS47的LT或BI端)。

- 它通过或非门

- 假设选手1 (

-

显示获胜者:

- 编码器

U1在被禁用之前输出的二进制编码 (A2A1A0或BCD码) 代表了获胜者的编号(选手1)。 - 这个编码被送到译码器/驱动器 (

U4)。- 如果

U4是74LS47+ 数码管:74LS47将BCD码转换成驱动7段数码管各段的信号,数码管显示数字“1”。锁存器Q的高电平可以用来点亮数码管的小数点或控制亮度。 - 如果

U4是74LS138+ LED:将3位二进制编码输入138,其对应的输出端(例如Y0)变为低电平,驱动连接到该输出端的LED(L1)发光,指示选手1获胜。其他LED熄灭。

- 如果

- 编码器

-

主持人复位:

- 主持人按下复位按钮 (

RST)。 RST按钮被按下,产生一个低电平脉冲(通常需要通过一个简单的RC电路消抖)。- 这个低电平脉冲连接到:

- RS锁存器 (

U2) 的复位端R(假设R低电平有效复位),强制其输出Q回到低电平。 - 优先编码器 (

U1) 的某个复位端(如果有)或者作为清除信号送到译码器。

- RS锁存器 (

- 锁存器

Q变低:- 释放了对编码器

EI的控制(EI端恢复为高电平),编码器再次处于允许工作状态(等待下一次抢答)。 - 清除显示(如果

Q低电平用于熄灭LED或数码管消隐)。译码器接收到复位信号也会清除显示。

- 释放了对编码器

- 系统回到步骤1的初始状态,等待下一轮抢答。

- 主持人按下复位按钮 (

PCB设计要点:

- 电源与地:

- 使用足够宽的走线(建议 > 20mil)连接所有芯片的

VCC(5V) 和GND。 - 在 每个芯片的

VCC和GND引脚之间就近放置一个0.1uF的陶瓷去耦电容,以滤除高频噪声,这对数字电路的稳定工作至关重要。电容越靠近芯片引脚越好。 - 电源输入端加一个极性电容(如10uF~100uF)进行大容量储能。

- 使用足够宽的走线(建议 > 20mil)连接所有芯片的

- 信号线:

- 连接按钮的导线:尽量短,并考虑在按钮两端并联一个小电容(如0.01uF~0.1uF)到地,或在软件/硬件上实现消抖。硬件消抖常用方案:在按钮和地之间串联一个电阻(如10kΩ上拉),在按钮和芯片输入端之间串联一个电阻(如1kΩ),再并联一个电容(0.01uF~0.1uF)到地。

- 连接LED的导线:每条LED回路都要串联一个限流电阻(计算阻值:

R = (Vcc - Vf_led) / I_led,常用220Ω~1kΩ)。 - 编码器输出到锁存器、锁存器到译码器、译码器到显示器的信号线:按逻辑清晰布设即可。

- 布局:

- 将选手按钮 (

S1-S4) 布局在PCB边缘方便操作的位置。 - 将主持人复位按钮 (

RST) 单独布局在另一侧或显著位置。 - 将显示器件(数码管或LED指示灯)布局在PCB正面显眼位置。

- 核心芯片 (

74LS148,74LS279,74LS02,74LS47/138) 可以集中布局在中间区域。 - 晶振/时钟源(如果后续增加计时功能): 尽量靠近使用它的芯片,走线短且等长(如果是差分时钟),周围避免高速数字信号线。

- 将选手按钮 (

- 布线:

- 优先布设电源和地线。

- 模拟部分(如果有,如声音电路)与数字部分分离布线,地线最后在电源入口处单点连接。

- 避免信号线在晶振、时钟线下方或其附近平行走线,以防干扰。

- 保持走线顺畅,避免锐角。

- 丝印层:

- 清晰标注所有元件位号 (Designator: R1, C1, U1, S1, LED1 等)。

- 标注按钮功能 (

S1,S2,S3,S4,RST)。 - 标注LED或数码管对应的选手编号 (

1,2,3,4)。 - 标注电源输入接口 (

VCC +5V,GND)。

调试建议:

- 先检查电源: 确保所有芯片的

VCC引脚有正确的5V电压。 - 静态测试: 复位状态下,用万用表测量编码器输入(应为高电平)、锁存器输出

Q(应为低电平)、编码器EI端(应为高电平 - 禁用)、编码器GS端(应为高电平 - 无输入)、译码器输出/显示(应无显示)。 - 动态测试:

- 按下

S1,观察:- 编码器

GS应变为低电平。 - 锁存器

Q应变为高电平。 - 编码器

EI应变为高电平(禁用)。 - 显示应指示选手1。

- 编码器

- 在选手1按下后,再按

S2/S3/S4,观察显示不应改变(锁定优先级)。 - 按下

RST,观察所有状态应恢复到初始状态。

- 按下

- 消抖问题: 如果发现抢答不稳定(一次按下多次触发),重点检查按钮消抖电路是否有效。

- 干扰问题: 如果发现误触发,检查去耦电容是否安装正确且靠近芯片引脚,电源是否干净,按钮走线是否过长或靠近干扰源。

扩展功能 (可选):

- 计时功能: 增加一个计数器(如74LS192/190)和一个晶振/时钟源,在有人抢答后开始计时并显示。

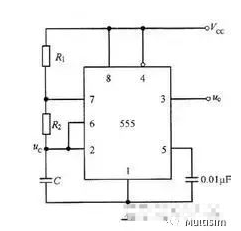

- 声音提示: 增加一个蜂鸣器或扬声器驱动电路,当有人抢答成功时发出声音(可用555定时器或门电路加三极管驱动)。

- 违规提示: 在主裁判发令前抢答视为违规。这需要增加一个“开始”信号(通常也是一个按钮),在“开始”信号有效前,即使按下抢答按钮也无效或触发违规提示(点亮违规灯或特殊声音)。这需要额外的逻辑电路(如门电路)来实现。

总结:

这个基于 74LS148 (或 74HC147) + 74LS279 + 74LS02 + 74LS47/138 的方案是实现抢答器最经典和可靠的核心逻辑。理解优先编码器识别第一个信号、RS锁存器锁定状态并禁用编码器这两步是关键。在PCB设计中,电源完整性(去耦电容)、信号完整性(消抖、走线规划) 和 清晰布局 是成功的关键。按照原理图焊接,仔细调试,应该能够制作出一个稳定的抢答器。

祝你PCB设计和制作顺利!

基于STM32的抢答器设计

前言最近在指导一个小学弟完成他的设计,借此机会记录一个小项目从“系统结构设计、器件选型、PC板绘制、程序调试”的过程。目的:设计一个四人的抢答器设计要求:1、抢答器可同时供四组

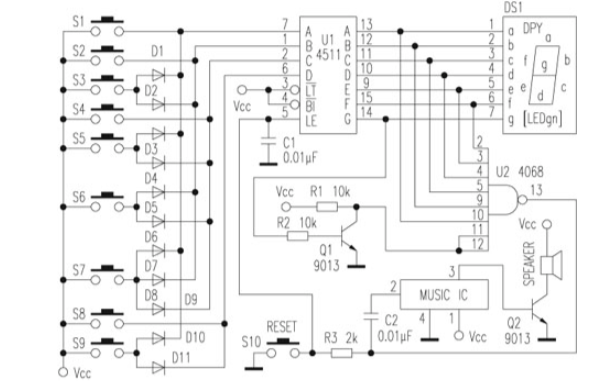

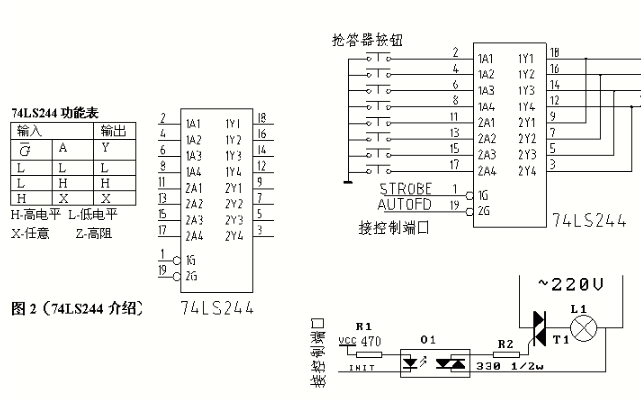

使用CD4511驱动器实现八路抢答器的PCB和电路原理图免费下载

本文档的主要内容详细介绍的是使用CD4511驱动器实现八路抢答器的PCB和电路

资料下载

![]() ah此生不换

2020-12-01 08:00:00

ah此生不换

2020-12-01 08:00:00

使用可编程逻辑器件设计具有扩充功能的抢答器论文免费下载

抢答器是在竞赛、文体娱乐活动(抢答活动)中,能准确、公正、直观地判断出抢答者的机器。电子

资料下载

佚名

2020-08-21 14:51:00

资料下载:知识竞赛抢答器PLC设计

知识竞赛抢答器PLC设计 2009年10月13日 知识竞赛抢答器PLC设计 摘 要:本文介绍了利用三菱FX2N系列PLC对知识竞赛抢答器的控

有偿 基于STC89C52单片机的四路抢答器设计

,若有选手按动抢答器按钮,编号立即锁存,并在LED数码管上显示选手的编号,同时扬声器给出音响提示。本系统以STC89C52为核心,由复位电路、时

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机